Преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«ii980113

{61) Дополнительное к авт. свид-ву (22) Заявлено 25. Об. 81 (21) 3305218/18-24 с присоединением заявки ИВ (31) М. Кп.з

С 08 С 9/00

Государственный комнтет

СССР по делам изобретеннй и открытнй

{23) Приоритет

Опубликовано 07.12.82. Бюллетень È9 45

Дата опубликования описаиия 07.12.82

153} УДК б81. 325 (088. 8) В. Т. Луз инский, Э. В. Андреев, Ю. Д. Бегер, A. В.форицкйй, Г.A.Êðÿæåíêoâà и Н.В.Петропольский

i

Московский институт радиотехники, электроники и автоматики (72) Авторы изобретения (Л) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В КОД

Изобретение относится к автомати" ке и вычислительной технике и может быть использовано для связи аналого" вых источников информации с цифровым вычислительным устройством.

Известны преобразователи перемещений в код, содержащие последовательно соединенные генератор импульсов, делитель частоты, фильтр, фаэовраща- тель, подключенный к блоку преобразования сдвига фазы в код, другой вход которого соединен с генератором импульсов (1) .

Недостатком известного преобразователя является сложность фильтра для обеспечения синусоидального напряжения питания фазовращателя °

Другой известный преобразователь содержит последовательно соединенные генератор импульсов, делитель частоты, формирователь многофаэного ступенчатого напряжеиия, фаэовращатель, фильтр и компаратор, подключенный к управляющему входу блока элементов

И, сигнальные входы которого подключены к выходам разрядов делителя частоты (2) .

Недостатком известного преобразователя является погрешность, вызванная изменением параметров фильтра.

Наиболее близким техническим реше нием к предлагаемому является преобразователь перемещения в код, содержащий генератор импульсов, подключенный к делителю частоты, интегратор, выход которого подключен через усилитель мощности к фазовращателю ., выход фаэовращателя подключен к одному входу блока преобразования сдвига фазы .в код,другой вход которого соединен с выходом делителя частоты. Выход разрядов делителя частоты поцключены к дешифратору,выходы которого подключены к управляющим входам ключей, другие входы ключей соединены с источниками ,тока, а выходы подключены к интегра" тору (3), Недостатком известного преобразователя является погрешность, вызванная изменением параметров источников тока и ключей, Цель изобретения — повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь перемещения в код, содержащий генератор импульсов, подключенный к делителю частоты, интегратор, выход которого подключен через усилитель мощности к фазовращателю, выход фаэовращателя подклю980113 чен к .одному входу блока преобразова» ния сдвига. фазы в код, другой вход которого соединен с выходом делителя частоты, введены блок делителей напряжения и сумматор, входы блока де,лителей напряжения соединены с проме- >

)жуточными выходами делителя частоты, а выходы блока делителей напряжения и выход старшего разряда делителя частоты подключены к сумматору, выход которого подключен к интегратору. 10

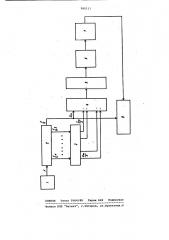

На чертеже представлена структур" ная схема преобразователя.

Преобразователь содержит генератор

1 импульсов, подключенный к делителю

2 частоты, промежуточные выходы кото-15 рого через блок 3 делителей напряже ния подключены к инвертирующим входам сумматора 4, неинвертирующий вх4д которого соединен с выходом делителя

2 частоты, выход сумматора 4 через щ последовательно соединенные интегра- тор 5, усилитель 6 мощности и фазо-: вращатель 7 подключен к одному входу блока 8 преобразования сдвига фазы в код, другой вход которого соединен с выходом делителя 2 частоты.

Преобразователь работает следующим образом.

Импульсы от генератора 1 с частотой g поступают на делитель 2 часто»

;с коэффициентом деления n,êà промежуточных выходах которого формируется и сетка частот < 3; -„5; ..., ."„К, где

К - простое число. Напряжение прямо угольной формы типа меандр с промежуточных выходов делителя 2 частоты поступают на блок 3 делителей .иапря" жения, где они делятся, соответствейно, в 3, 5, 7, ..., К раз. С выходов

)блока 3 напряжения прямоугольной фор"

Ьы поступают на инвертирующие входы, 0

)сумматора 4, иа неинвертирующий вход

Ircoxoporo поступает прямоугольное на-, пряжение с основного выхода делителя

2 частоты, частотой Х)И. В результате сложения в сумматоре 4 указанных вы- 45 ше напряжений, на выходе сумматора 4 формируется сигнал.

U I61È +OH+ 61И И-ИМ+ 8»И - О1И1- " — 5 ВАМИ я- ЫИФ - -8 И ф-4Щ4 б ° У— 61И вЂ” 10fs+++ МИ -Я ЗЗ1Г +" / " )

4 з и " и

Этот сигнал не содержит в своем спектре, 3, 5, 7, 9, ... гармоничес- ких составляющих, в зависимости от ъо

)го сколько промежуточных выходов деI лителя 2 частоты использовано. В ин" теграторе 5 производится фильтрация высокочастотных гармонических состав. ляющих.

С выпада интегратора 5 сигнал пос тупает на усилитель 6 мощности, к вы" ходу которого подключен фаэовращатель

7. На выходе фазовращателя 7 появляется сигнал, фаза которого пропорцио нальна перемещению фазозращателя 7.

Блок 8 преобразует сдвиг по фазе между выходными сигналами делителя 2 и фаэовращателя 7 в код.

В предлагаемом преобразователе вы ходной сигнал интегратора, используемый для питания фазовращателя, прин,ципиально не содержит в своем спектре четных гармоник и постоянной сос-, тавляющей. Напряжение питания фаэовращателя в таком преобразователе бу) дет больше приближаться к синусоидальному, чем в известных преобразователях, что обеспечивает повышение точности преобразователя по сравнению с известными.

Формула изобретения.

Преобразователь перемещения в код, содержащий генератор импульсов, подключенный к делителю частоты, интегратор, выход которого подключен через усилитель мощности к фаэовращателю, выход фаэовращателя подключен к одному входу блока Преобразования) сдви" га фазы в код, другой вход которого соединен с выходом делителя частоты, отличающийся тем, что, с целью повышения точности преобразователя, в него введены блок делителей напряжения и сумматор, входы блока делителей напряжения соединены с промежуточными вы ходами делителя частоты,а выходы блока делителей напряжения и выход старшего разряда делителя частоты подключены к сумматору, выход которого подключен к интегратору.

Источники информации, принятые во внимание при экспертизе

1. Патент C2lh 9 3505669, кл. 340347, 1970.

2. Авторское свидетельство СССР

9 413515, кл. G 08 С 9/00, 1972.

3. Авторское свидетельство СССР

Р 734776, кл. G 08 С 9/04 1977 (прототип) .