Запоминающее устройство с коррекцией дефектных элементов памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

x as ©wcxoev cseggxaascrsv

Союз Советских

Социалистических республик («)980165 (б1) Дополнительное к авт. свид-вур )уц з (22) Заявлено 02.06,81 (21) 3292811/18-24 с присоединением заявки 8о (23) Приоритет—

G 11 С 29/00

Государственный комитет

СССР ио делам изобретений и открытий (53) УДК 681. 327 (088. 8) Опубликовано 07.1282 Бюллетень Ио 45

Дата опубликования описания 10.1282 (72) Авторы изобретения

В.К. Конопелько и А.И. Сухопаров не

/ . 1 :.;

Минский радиотехнический институт (71) Заявитель (54) ЭАПОИИНИПЦЕЕ УСТРОИСТВО С КОРРЕКЦИЕИ

ДЕФЕКТНЫХ ЭЛЕИЕНТОВ IIAKHTH

Изобретение относится к запоми,нающим устройствам и может быть использовано при изготовлении больших интегральных схем запоминающих устройств.

Известно запоминающее устройство с коррекцией дефектных элементов памяти, содержащее матрицу элементов памяти схемы логики обрамления и коррекции (11.

Недостатками устройства йвляются низкое быстродействие и сложность схем коррекции.

Наиболее близким по технической сущности к предлагаемому является запоминанидее устройство с коррекцией дефектных элементов памяти, содер,жащее дешифратор адреса слова, соединенный с адресными шинами матрицы элементов памяти, разрядные шины которой соединены с выходами первых н вторых вентилей, информационными входами первого и второго блоков считывания, управляющие входы первого блока считывания соединены с выходами дешифратора адреса разряда и с первыми входами первых вентилей, вторые, третьи и четвертые входы первых и вторых. вентилей соединены соответственно с шинами разрешения записи, записи, управления и первым входом выходного блока, входы дешиф-. ратора адреса разряда соединены с адресными входами элементов И программируемой логической матрицы выходы элементов И программируемой логической матрицы соединены с входами элемента ИЛИ-НЕ, выходом соединенного с пятыми входами первых вентилей, прямым и инверсным входами первого и второго элементов H„ вторые входы первого и второго элементов И соединены соответственно с выходами первого и второго блоков. считывания, выходы первого и второго элементов Ц соединены с входами элемента ИЛИ, выходом соединенного с вторым входом выходного блока (2g .

Недостатком этого устройства является низкая надежность из-за невозможности коррекции дефектных элементов памяти в дополнительных разрядак.

Цель изобретения — иовыаение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с кор

:рекцией дефектных элементов памяти, содержащее запоминающую матрицу, дешифраторы адреса, блоки считывания

980165

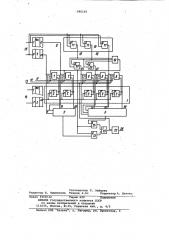

На чертеже приведена функциональ. ная схема устройства.

Устройство содержит запоминающую

5S матрицу 1 с элементами 2 памяти, пер вый 3 и второй 4 дешифраторы адреса, первый 5 и второй 6 блоки считывания, первая 7 и вторая,8 группы эле- ментов И, управляющие входы 9 первого4 блока считывания, разрядные шины 10 запоминающей матрицы, вход 11 разрешения записи устройства, входы 12 записи и 13 управления устройства и адресные входы 14 и 15 устройства., 65 программируемую логическую матрицу, элемент ИЛИ-НЕ, группы элементов И, элемент ИЛИ, элементы и и блок вывода информации, причем первые, вторые и третьи входы элементов И первой и второй групп соответственно объеди- 5 нены и являются входом разрешения записи, входом записи и входом управления устройства, выходы первого дешифратора адреса подключены к адресным шинам запоминающей матрицы, основ- IO ные разрядные и управляющие шины которой соединены соответственно с прямыми выходами элементов И первой группы и вхоцами первого блока считырания и с инверсными выходами элемен-f$ тов И первой группы, дополнительные, разрядные и управляющие шины запоминающей матрицы подключены соответственно к прямым выходам элементов

И второй группы и входам второго блока считывания и к инверсным выходам элементов И второй группы, управляющие входы первого блока считывания соединены с выходами второго дешифратора адреса и четвертыми, входами элементов И первой группы, пятые входы которых подключены к выходу элемента ИЛИ-НЕ и первым входам первого и второго элементов И, вторые входы которых соединены соответствен но с выходами первого и второго блоков считывания, а выходы — с входами элемента ИЛИ, выход которого подключен к первому входу блока вывода информации, второй вход которого соединен с третьими входами элементов И первой и второй групп, а выход является выходом устройства, входы программируемой логической матри цы подключены к входам второго де-. шифратора адреса, а выходы — к входам 40 элемента ИЛИ-НЕ, введена третья группа элементов И, первые и вторые входы которых подключены соответственно к выходам программируемой логической матрицы, а выходы - к четвертым вхо- 45 дам одних иэ элементов И второй группы и к одним из управляющих входов второго блока считывания, другой управляющий вход которого соединен с четвертым входом другого элемента И второй группы и одним иэ входов элемента ИЛИ-НЕ.

Устройство содержит также програм мируемую логическую матрицу 16, выполненную на элементах И 17 с выхо- дами 18, элемент ИЛИ-НЕ 19, третью группу элементов И 20 с выходами

21, блок 22 вывода информации, первый 23 и второй 24 элементы И и элемент ИЛИ 25, выход 26 устройства.

Устройство работает следующим образом.

При изготовлении при обнаружении дефектных элементов памяти в матрице

1 в элементы И 17 матрицы 16 заносятся адреса основных разрядов матрицы

1, которые содержат дефектные элементы памяти. Программирование матрицы 16 осуществляется путем пережигания в ней плавких связей. В том случае, если подключенный дополнительный разряд элементов 2 паияти:управляемый элементами И 8 содержит дефектные элементы 2 памяти, то программируемый адрес вновь заносится в элементы И 17 следующего слова матрицы 16.

При эксплуатации при записи информации на соответствующие шины устройства подаются сигналы разрешения записи 11, записи 12 и управления 13.

При этом происходит возбуждение шин дешифраторов 3 и 4 в соответствии с кодом адреса опрашиваемого элемента 2 памяти матрицы 1. Возбужденная шина дешифратора 3 подключает элементы 2 памяти матрицы 1 выбранного слова к разрядным шинам 10. Одновременно происходит сравнение входного адреса опрашиваемого разряда, поступающего на входы 15 с информацией о дефектных разрядах, содержащейся в матрице 16.

Если опрашивается исправный основной разряд матрицы 1, управляемый элементами И 7, то на выходах 18 матрицы 16 появляются нулевые сигналы которые устанавливают на выходе эле-" мента ИЛИ-НЕ 19 единичный сигнал, а на выходах 21 элементов H 20 — нулевые сигналы..Эти сигналы открывают элементы И 7 и закрывают элементы

И 8. ТОгда в основной разряд матрицы 1, открытый сигналом одного из выходов 9 дешифратора 4 происходит запись входной информации, поступающей по входу 12.

Если опрашиваются дефектный основной разряд матрицы 1 и исправный дополнительный разряд матрицы 1, то на одном из выходов 18 появляется единичный сигнал, который- устанавливает на выходе элемента ИЛИ-НЕ 19 и выходах 21 элементов И 20, кроме одного выхода, нулевые сигналы, которые закрывают элементы И 7 и 8, кроме одного. Таким образом, в дополнительный разряд матрицы 1, управляемый открытым элементом И 8, 980165 мируемой логической матрицы, а вы50 ходы — к четвертым входам одних из элементов И второй группы и к одним из управляющих входов второго блока считывания, другой управляющий вход которого соединен с четвертым входом

55 другого элемента И второй группы и одним из входов элемента ИЛИ-НЕ.

Источники информации, принятые во внимание при экспертизе

1 Авторское свидетельство СССР еО йо заявке Р .2883238/18-24, кл. G 11 С 29/00, 1980.

2. Сад Р, Харди К. Повышение быстродействия статических ЗУПВ.-"Электроника", 1980, Р 20, с.25-34 (прото

65 тип) . произойдет запись входной информации °

Если же опрашиваются дефектный основной разряд и, например два дополнительных разряда, что говорит о дефектности одного из них, то на двух соседних выходах 18 появляются единичные сигналы.

Поскольку соответствующий второму из опрашиваемых дополнительных разрядов матрицы 1 сигнал с соответствующего выхода 18 поступает на инверсный вход соседнего элемента И 20, то устанавливаются нулевые сигналы на выходах элемента ИЛИ-НЕ 19 и этого и других элеменТов И 20, кроме элемента И 20, соответствующего второму из опрашиваемых дополнительных разрядов матрицы 1. В результате в этот дополнительный разряд матрицы

1, открытый элементом И 8, произойдет запись входной информации.

В режиме считывания сигналы по входам 11 и 12 отсутствуют. При этом элементы И 7 и 8 заперты, а сигнал о состоянии опрашиваемого основного элемента памяти матрицы 1 поступает с выхода блока 5 считывания на вход элемента И 23.

Если опрашивается исправный основной разряд матрицы 1, то на выходе элемента ИЛИ-НЕ 19 устанавливается,как в режиме записи, единичный сигнал, который открывает элемент И 23, и информация поступает на выход 26 устройства через блок 22.

Если же опрашивается дефектный основной разряд матрицы 1, то на одном из выходов 21 элементов И 20 появляется единичный сигнал, который разрешает поступление на вход элемента И 24 сигнала с исправного дополнительного разряда матрицы 1 через блок 6. Поскольку на выходе элемента ИЛИ-НЕ 19 нулевой сигнал, который открывает элемент 24, то правильно хранимая информация с дополнительного разряда матрицы 1 поступает на выход 26 устройства.

Таким образом, предлагаемое устройство позволяет производить коррекцию дефектных элементов 2 памяти не только.в основных>но и в дополнительных разрядах матрицы 1, что повышает его надежность, поскольку если в соседних словах матрицы 16 хранится один и тот же адрес, обращение при записи и считываний происходит к одному дополнительному разряду матрицы 1, а не к двум сразу, как в прототипе.

Технико-зкономическое преимущество предлагаемого устройства заключа.ется в его более высокой надежности..

Формула изобретения в

Запоминающее устройство с коррек-, цией дефектных элементов памяти, содержащее запоминающую матрицу, дешиф. раторы адреса, блоки считывания,,программируемую логическую матрицу, элемент ИЛИ-НЕ, группы элементов И, элемент ИЛИ, элементы И и блок вывода информации, причем первые, вто рые и третьи входы элементов И первой и второй групп соответственно объединены и являются входом разре щения записи, входом записи и входом

1ц управления устройства, выходы первого дешифратора адреса подключены к адресным шинам запоминающей матрицы, основные разрядные и управляющие шины которой соединены соответственно

15 с прямыми выходами элементов И первой группы и входами первого блока считывания и с инверсными выходами элементов И первой группы, дополнительные разрядные и управляющие шины за2О поминающей матрицы подключены соответственно к прямым выходам элементов И второй группы и входам второго блока считывания и к инверсным выхо" дам элементов И второй группы, управ25 ляющие входы первого блока считывания соединены с выходами второго де шифратора адреса и четвертыми входами элементов И первой группы, пятые входы которых подключены к выходу 0 элемента ИЛИ-НК и первым входам первого и второго элементов И, вторые входы которых соединены соответственно с выходами первого и второго блоков считывания, а выходы — с входами элемента ИЛИ, выход которого подклю1 чен к первому входу блока вывода информации, второй вход которого соединен с третьими входами элементов И первой и второй-групп, а выход является выходом устройства, входы программируемой логической матрицы подключены к входам второго дешифратора адреса, а выходы — к входам элемента ИЛЙ-НЕ; о т л и ч а ю— щ е е с я тем, что, с целью повышения надежности устройства, в него введена третья группа элементов И;. первые и вторые входы которых подключены соответственно к выходам програм: 98016 5

Составитель Т. Зайцева

Редактор Е. Лушникова Техред A.Ач Корректор A. Дзятко.

5Ъат % 3п7 Тираж 6 Подписное

ВНИИПИ Государственного комитета СССР по.делам изобретений и открытий

113035, Москва, Ж- 35, Раушская наб., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Проектная,