Импульсно-временной дискриминатор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик оц980248 (61) Дополнительное к авт. свмд-ву (22) Заявлено 110231 (21) 3249929/18-21 рцэр, g+ з

Н 03 О 13/00 с присоединением заявки №

Государственный комитет

СССР яо делам изобретений и открытый (23) Приоритет

Опубликовано 07.1282. Бюллетень ¹ 4

Дата опубликования описания 07.12В2

t$3) УДК 621.374..33(088.8) (22) Авторы изобретения

Л.Н. Герасимов и В.В. Скрябин (21) Заявитель (54) ИМПУЛЬСНО-ВРЕМЕННОЙ ДИСКРИМИНАТОР

Изобретение относится к радиоэлектронике и может быть использовано в устройствах стабилизации временного положения импульсов радиолокационных систем.

Известен импульсно-временной дискриминатор, содержащий два триггера, четыре инвертора и четыре элемента

И-НЕ. 10

Недостатком известного устройства является низкая надежность работы.

В этом устройстве. в момент появления на входе второго импульса на второй выходной шине формируется ложный кратковременный сигйал. Кроме того, устройство содержит относительно большое количество логических элементов.

Наиболее близким по технической сущности к предлагаемому является импульсно-временный дискриминатор, соцержащий триггер, четыре элемента

И-НЕ, выход первого из которых соединен с нулевым входом триггера, и цва инвертора, выходы которых соединены с входами второго элемента H-HE, выход которого подключен к единичному входу триггера, выход которого соединен с первыми входами третьего и четвертого элементов И-НЕ, первая выходная шина соединена с входом перво- 30 го инвертора, первым входом первого элемента И-НЕ и вторым входом третьего элемента И-НЕ, а вторая входная шина соединена с входом второго инвертора и вторыми входами первого и четвертого элементов И-НЕ, .выход третьего элемента И-НЕ соединен с третьеим входом четвертого элемента

И-НЕ, выход которого соединен с третьим входом третьего элемента И-НЕ.

Недостатком известного устройства является низкая, надежность работы, обусловленная тем, что при одновременном поступлении импульсов на входы дискриминатора, на одном из его выходов формируется кратковременный ложный сигнал, который может быть воспринят как сигнал запаздывания одного импульса относительно другого.

Цель изобретения — повышение надежности работы устройства.

Поставленная цель достигается тем, что в импульсно-временном .дискриминаторе, содержащим триггер, четыре элемента И-НЕ, выход первого из которых соединен с нулевыч входом триггера, и и два инвертора, выходы которых соединены с входами второго элемента И-НЕ, выход которого подключен к единичному входу триггера, выход которого со.

980248

Формула изобретения

3 единеи с первыми входами третьего и четвертого элементов И-НЕ, первая входная шина соединена с входом первого инвертора, первым входом первого элемента И-НЕ и вторым входом третьего элемента И-НЕ, а вторая ши- 5 на соединена с входом второго инвер«

1тора и вторыми входами первого и четвертого элементов И-НЕ, выход перво- . го инвертора соединен с третьим входом четвертого элемента И-НЕ, четвер- 0 тый вход которого соединен с выходом второго элемента И-НЕ и третьим,входом третьего элемента И-НЕ, четвертый вход которого подключен к выходу вто,рого инвертора. 15

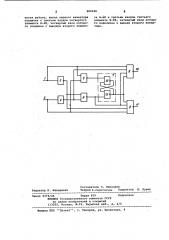

На чертеже изображена структурная электрическая схема устройства.

Импульсно-временный дискриминатор содержит входные шины 1 и 2, инверторы 3 и 4, элементы И-HE 5 и 6, триггер 7, элементы 8 и 9, выходные шины

10 и 11. Триггер 7 состоит из элементов И НЕ 12 и 13.

Выход первого элемента.И-ЙЕ 5 соединен с нулевым входом триггера 7, выходы инверторов 3 и 4 соединены с входами второго элемента И-НЕ б, выход которого подключен к единичному входу триггера 7, выход которого соединен с первыми входами третьего и четнертого элементов И-HE 8 и 9, пер-З0 вая входная шина 1 соединена с входом первого элемента И-НЕ 5 и вторым входом третьего элемента И-ЙЕ 8. Вторая входная шина 2 соединена с входом второго инвертора 4 и вторыми 35 входами первого и четвертого элементов И-НЕ 5 и 9, выход первого инвертора 3 соединен с третьим входом четвертого элемента И-НЕ 9, четвертый вход которого соединен с выходом нто-40 рого элемента И-НЕ б и третьим входом третьего элемента И-НЕ 8, четвертый вход которого подключен к выходу второго инвертора 4.

Импульсно-временный дискриминатор 45 работает следующим образом.

При поступлении импульса на шину

1 на выходе элемента И-НЕ 5 сохраняется логическая единица, на ныходе элемента И-НЕ б устанавливается логическая единица, триггер 7 не изменяет своего состояния, открывается элемент И-НЕ 8, с выхода которого на выходную шину 10 поступает сигнал, соответствующий логическому нулю. Такое состояние сохраняется до появления второго импульса на шине 2. По фронту импульса на шине 2 на ныходе инвертора 4 устанавливается логический нуль, который закрывает элемент

И-НЕ 8, на шине 10 устанавливается 60 логическая единица. Кроме того, открывается элемент И-НЕ 5, по сигналу с выхода которого переключается в нулевое состояние триггер 7 и дополнительно блокирует элементы И-НЕ 8, 65

9. По окончании действия первого импульса на шине 1 на выходе элемента

И-НЕ 5 появляется логическая единица, а по окончании действия второго импульса на шине 2 на выходе элемента И-НЕ б устанавливается логический нуль, в результате чего триггер 7 переключается в единичное состояние.

Таким образом, на одной из выходных шин 10 и ll дискриминатора в конкретных ситуациях вырабатывается импульс, длительность которого определяется временем запаздывания одного входного импульса относительно дру-: гого.

Если же оба импульса одновременно подаются на шины 1 и 2, то ни на одной их выходных шин 10 и ll не появ ляются сигналы. В первый мсмент (при появлении входных импульсов на шинах

1 и 2) элементы И-НЕ 8 и 9 удерживаются н закрытом состоянии логическим нулем с выхода элемента И-НЕ 6. Далее через время, равное времени задержки срабатывания одного логического элемента, закрытое состояние элементов И-HE 8 и 9 поддерживается логическими нулями с выходов инверторов 3 и 4, при этом элемент И-HE 6 закрывается, и на его выходе устанавливается логическая единица, не препятствующая переключению в нулевое состояние триггера 7 от логического нуля с выхода элемента И-HE 5. После окончания. действия первого импульса н а шине l или 2 (при входных импуль! сах, отличающихся от длительности) закрытое состояние элементов И-НЕ 8 и 9 поддерживается логическим нулем с триггера 7.

Предлагаемый дискриминатор по сравнению с известным обладает более высокой надежностью, так как он не формирует ложных сигналов при одновременном поступлении импульсов на его входы.

Импульсно-временной дискриминатор, содержащий триггер, четыре элемента

И-НЕ, выход первого из которых соединен с нулевым нходом триггера, и два инвертора, выходы которых соединены с с входами второго элемента И-НЕ, выход которого подключен к единичному входу триггера, выход которого соединен с первыми входами третьего и четвертого элементов И-НЕ, первая входная шина соединена с входом первого инвертора, первым входом первого элемента И-НЕ и вторым входом третьего элемента И-НЕ, а вторая входная шина соединена с входом второго инвертора и вторыми входами первого и четвертоro элементов И-НЕ, о т л и ч а ю щ и йся тем, что, с целью повышения надеж980248

Составитель С. Николаев

Техред Е.Харитончик Корректор Н; Буряк

Редактор П. Макаревич

Заказ 9379/46 Тираж -959

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 ности работы, выход первого инвертора соединен с третьим входом четвертого элемента И-НЕ, четвертый вход которого соединен с выходом второго элемента И-HE и третьим входом третьего элемента И-НЕ, четвертый вход которо

ro подключен к выходу второго инвертора.