Преобразователь разбаланса дифференциальных датчиков в интервал времени

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистическик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 190181 (21) 3240562/18-21 )5$) М. Кд.3 с присоединением заявки Нов (23) Приоритет—

Н 03 К 13/20

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681. 325 (088.8) Опубликовано 071282. Бюллетень Йо45

Дата опубликования описания 07 ° 12. 82 (72) Авторы изобретения

В.Л.Баландин, В.И.Кулапин,А.И.Мартяшин,Б.Л;Сщ стунов и В.И.Чернецов

Пензенский политехнический институт (71) Заявитель (54 ) ПРЕОБРАЗОВАТЕЛЬ РАЗБАЛАНСА ДИФФЕРЕНЦИАЛЬННХ

ДАТЧИКОВ В ИНТЕРВАЛ ВРЕМЕНИ

Изобретение относится к контроттю параметров радиоэлектронной аппаратуры и параметров различных технологических процессов с помощью дифференциальных датчиков.

Известны устройства для преобразования выходных величин дифференциальных датчиков в унифицированные сигналы, содержащие частотнонезависимую мостовую схему, плечи которой образуют рабочую и компенсационную половину датчика, а также опорные элементы. Напряжение с измерительной диагонали несет информацию о выходной величине датчика и с целью повышения точности обычно используется для управления уравновешиванием моста t 1).

Недостатки таких устройств - нелинейность функции преобразования, а также невысокое быстродействие, что существенно ограничивает их использование для исследования быстропротекающих процессов.

Известен преобразователь разбаланса дифференциальных датчиков, содержащий два опорных элемента, делитель напряжения, выход которого соединен с первым входом компаратора, выход которого соединен с входом ин тегратора и первым входом суммато= ра 2). едостаток устройства заключается в том, что выходной сигнал зависит не только бт информативного параметра b.Q но и от паразитного сопротивления Ry,, Цель изобретения — повышение точности преобразования.

Поставленная цель достигается тем, что в преобразователь разбаланса дифференциальных датчиков в интервал времени, содержащий два опорных элемента, делитель напряжения, выход которого соединен с первым входом .компаратора, выход которого соеди= нен с входом интегратора и первым входом сумматора, введены два операционных усилителя, дополнительные ком паратор и сумматор, причем выход компаратора подключен к входу делителя напряжения, выход дополнительного компаратора соединен с вторым входом сумматора, выход которого подключен к первому входу дополнительного компаратора и к общей точке половин дифференциального датчика, выходы которого подключены к входам операционных усилителей, в цепи отрицательных

;обратных связей которых включены опор

980277

Преобразователь работает следующим образом.

В момент включения напряжения пи- 50 тания на выходах компараторов 1 и 9 устанавливается напряжение, равное

+ Ue . Таким образом, на выходе сумматора 3

U = - (U + U ) = - 20 ).

ЗТ

Это напряжение подается на общую точку половин дифференциального датчика 5, представленной схемой замещения для одной К СХ и Х Х 60 для другой.

Выходной сигнал усилителя б имеет вид

2 0„ t 2Uo CU.

8ИХ 6 R>Ce Сб

65 ные элементы, а их выходы подключены к первому и второму входам дополнительного сумматора, третий вход которого подключен к выходу интегратора, а выход - к вторым входам.компаратора и дополнительного компаратора.

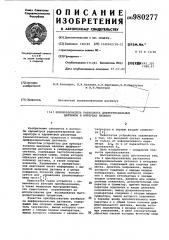

На фиг. 1.приведена функциональная схема предлагаемого преобразователя, на фиг. 2 †временные диаграммы, поясняющие его работу. 10

Преобразователь разбаланса диф,ференциального датчика в интервал

1времени содержит компаратор 1, делитель 2 напряжения, сумматор 3, ин; тегратор 4, дифференциальный датчик 15

5, представленный четырехэлементной схемой замещения, первый операционный усилитель б с опорным элементом, выполненным в виде конденсатора емкостью С в цепи отрицатель- 20 ной обратной связи, второй операционный усилитель 7 с опорным элементом, выполненным в виде конденсатора емкостью Су в цепи отрицательной обратной связи, дополни- 25 тельный сумматор 8, дополнительный компаратор 9. При этом выход компаратора 1 дополнительно соединен с входом пассивного делителя 2 и одним из входов сумматора 3, сигнал с выхо- 30 да сумматора 3 подают на один из входов дополнительного компаратора

9 и на общую точку половин дифферен циального датчика 5, а с выходов дифференциального датчика 5 на соответствующие входы операционных усилителей б и 7. Сигналы с выходов операционных усилителей б и 7 поступают соответственно на два входа дополнительного сумматора 8, на третий вход которого поступает сигнал с вы- 40 хода интегратора 4, а выход дополнительного сумматора 8 подключен к другому входу дополнительного компаратора 9, причем выход дополнительного компаратора 9 подключен к входу сум- 45 матора 3.

Аналогичным образом выходной сигнал усилителя 7 имеет вид и

yale> R>C> 1

Напряжение с выхода компаратора 1 подают еще и на вход интегратора 4.

Напряжение с выхода интегратора 4 имеет вид

U, * - U-—

SSia4 где С вЂ” постоянная времени интеграИ тора 4.

Также это напряжение компаратора 1 подают на делитель 2 напряжения с коэффициентом деления и, напряжение с выхода делителя имеет вид

ВЫХ

Сигналы, поступающие на входы дополнительного сумматора 8, суммируются с коэффициентами 0,-(-1), 1 -.844 1 1

ИЬ(Х 7 ЬЫХ4

Напряжение с выхода дополнительного сумматора 8 имеет вид иь х11 (8ь/х г ьыхь иьж43 .20ц t 20О (Д 2Ц t 20P Сх х б

Если величины С6 С = С, то

20о t 1 1 2Up н и

u = — (— - — „) + — о(с - с„.)+u с ц в„" са х а-с

Коэффициент деления и выбирается таким, чтобы дополнительйый компаратор 9 изменил выходное напряжение на противоположное раньше, чем компаратор 1. На дополнительном компараторе 9 происходит сравнение напряжений с выхода дополнительного сумматора 8 и с выхода сумматора 3, в момент равенства этих напряжений происходит изменение полярности напряжения на выходе дополнительного компаратора 9. Равенство напряжений поступает. в момент времени

В момент времени t, с выхода дополнительного компаратора 9 получа ем -0 Тогда с выхода сумматора

3 на дйфференциальный датчик поступает напряжение равное нулю

U 0 -U = О.

8Ь!Х Ь о

Тогда напряжение с выхода операционных усилителей б и 7 будет

au r., ЬЫХ о . И"Х, i „ ХC6

На выходе дополнительного сумматора 8 имеем

2 011 t q 220 t f

ИЫХ 8Х СО RX Са О и

2u, ti t (— - — т)+Π—.

R p С

980277

Из условия определения равенства напряжений на входах дополнительнога компаратора 9 следует

20., 1 1 с, 0 с (-, - — „) =-20 -u — - — („. - с„).

Таким образом, t 20 I 11

0 =0ь " 20 (С Cp()

3ЫXgty+ Г„oP> о 0а

На компараторе 1 напряжение"6 ц сравнивается с напряжением, поступающим с выхода делителя 2, и для момента времени й<, когда происходит равенство напряжений на входах компаратора 1, имеем

15

n u =u —,- u — - 20- — -(с - с„).

20 i u

4 0 О ГД а Г„о- Са Х

Из этого следует

2t и е - c - ; (и. +2)+ — "(С - С ) и СО К

= 4 (2 + "т) + — б "х.

2 Ги и

Таким образом, интервал времени, равный разности времени срабатыва=Г(„+2)+ "аС

2 Г и а С

О

При переключении компаратора 1 ,цикл повторяется с обратными знаками для напряжений.

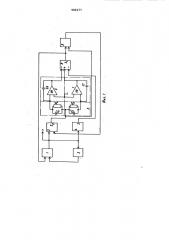

При использовании индуктивного диф--ЗО ференциал .и датчика, представленного двухэлементной последовательной схемой замещения для каждой области, причем для первой икотки активное ! сопротивление Ry, ин,к;-вность

И для второй R> и L X опорными элементами служат индуктивности Lz. Схема включения представлена на фиг. 3 °

При этом опорные элементы включают на входах операционных усилителей, а 40 каждая обмотка дифференциального датчика подключена соответственно в цепь отрицательной обратной связи каждого из операционных усилителей.

При этом описание работы устройств остается без изменения, а выходная величина описывается выражением ния компаратора 1 и дополнительного компаратора 9, определен только информативным параметром дифференциальноГо датчика. Следует отметить, что в результате технологического процесса у дифференциальных датчиков КХФ R>, данный преобразова тель позволяет полностью устранить их влияние на выходной. параметр.

- Формула изобретения

Преобразователь раз баланса дифференциальных датчиков в интервал времени, содержащий два опорных элемента, делитель напряжения, выход которого соединен с первым входом компаратора, выход которого соединен с входом интегратора и первым входом сумматора, о т л и ч а ю шийся тем, что, с целью повышения точности преобразования в него введены два операционных уси. лителя, дополнительные компаратор и сумматор, причем выход компаратора подключен к входу делителя напряжения, выход дополнительного компаратора соединен с вторым входом сумматора, выход которого подключен к первому входу дополнительного компаратора и к общей точке половин дифференциального датчика, выходы которого подключены к входам операционных усилителей, в цепи отрицательных обратных связей которых включены опорные элементы, а их выходы подключены к первому и второму входам дополнительного сумматора, третий вход которого подключен к выходу интегратора, а выход.к вторым вхедам компаратора и дополнительного компаратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р 561909, кл. Н 03 К 13/20,i 1977.

2. Авторское свидетельство СССР

9 420117, кл. Н 03 К 13/20, 1974. (прототип ).

980277

Составитель В.Махнанов

Редактор А.Мотыль Техред A.йч Корректор Е.Рошко

Заказ 9381/48 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная., 4