Двенадцатитактный реверсивный распределитель импульсов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублнм

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОА4У СВйДЕТЕЛЬСХВУ

<1,980287 (б1) Дополнительное к авт. свид-ву (22) Заявлено 12. 06. 81 (21) 3301455/18-21 (И1М. Кл. с присоединением заявки N9

Н 03 К 17/62

Государственный комитет

СССР по . делам изобретений и открытий (23) Приоритет

Опубликовано 07.1?82. Бюллетень М245 (331УДК 681.32 (088.8) Дата опубликования описания 07. 12. 82 (72) Авторы изобретения

В.П. Пайгин Ю.Л. Соколов (71) Заявитель (54) ДВЕНАДЦАТИТАКТНЫЙ РЕВЕРСИВНЫЙ РАСПРЕДЕЛИТЕЛЬ

ИМПУЛЬСОВ

Изобретение относится к .автоматике и вычислительной технике.

Известны двенадцатитактные реверсивные распределители импульсов, содержащие D-триггеры и элементы 2И.ИЛИ (1).

К недостаткам указанных распределителей относится низкая помехоустойчивость.

Наиболее близким к предлагаемому является двенадцатитактный реверсивный распределитель импульсов, содержащий шесть D-триггеров, С-входы которых соединены с тактовой шиной, D-вхсды подключены соответственно к выходам элементов 2И-ИЛИ, а единичные выходы — к выходным шинам, шина обратного хода соединена с первыми входами первых элементов И элементов

2И ИЛИ., а шина прямого хода — с первыми входами вторых элементов И элементов 2И-ИЛИ, причем второй и третий входы первых элементов И элементов 2И-ИЛИ соединены соответственно с нулевыми выходами четвертого и пятого, пятого и шестого, шестого и первого, первого и второго, второго и третьего, третьего и четвертого

D-триггеров, а второй и третий: входы вторых элементов И элементов 2И-ИЛИ соединены соответственно с нулевыми выходами третьего и четвертого, четвертого и пятого, пятого и шестого, шестого и первого, первого и второго, второго и третьего D-триггеров (2).

К недостаткам известного распределителя относится низкая помехоустойчивость.

Цель изобретения - повышение ïîìåхоустойчивости двенадцатитактного реверсивного распределителя импульсов.

Указанная цель достигается тем, что в двенадцатитактном реверсивном распределителе импульсов, содержащем шесть D-триггеров, С-входы которых соединены с тактовой шиной, D-входы подключены соответственно к выходам элементов 2И-ИЛИ, а единичные выхо2О ды - к выходным шинам, шина обратного хода соединена с первыми входами первых элементов И элементов 2И-ИЛИ, а шина прямого хода - с первыми входами вторых, элементов И элементов

2И-ИЛИ, причем второй и третий вхо?5 д первых элементов И элементов

2И-ИЛИ соединены соответственно с нулевыми выходами четвертого и пятого, пятого и шестого, шестого и первого, первого и второго, второго и третьего, третьего и четвертого

980287

Если на шине 20 имеется единичный логический уровень, то двенадцатитактный реверсивный распределитель импульсов работает в обратном направлении, а если единичный логический уровень имеется только на шине 21, то распределитель импульсов работает в прямом направлении. Во втором случае единичный сигнал присутствует только на D-входах D-триггеров 1,2 . и 3. Первый тактовый импульс перебрасывает D-триггер 3 в единичное состояние; такое же состояние поддерживается в D-триггерах 1 и 2. Второй тактовый импульс приводит к сбросу

D-триггера 1, а в D-триггерах 2 и 3 единичное состояние сохраняется. Далее процессы протекают аналогично, а на выходах D-триггеров 1-6 формируется последовательность 12-123-23234-34-345-45-456-56-561,-61-612-12... (в этой последовательности цифрами

D-триггеров, а второй и третий входы вторых элементов И элементов 2И-ИЛИ соединены соотве тс твен но с нулевыми выходами третьего и четвертого, четвертого и пятого, пятого и шестого, шестого и первого, первого и второго, S второго и третьего D--триггеров, нулевые выходы шестого, пятого и четвертого D-триггеров соединены с R-входами соответственно третьего, второго и первого D-триггеров.

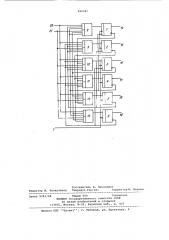

На чертеже представлена функциопальная схема двенадцатитактного реверсивного распределителя импульсов.

Распределитель содержит D-триггеры 1-6, С-входы которых соединены с 15 тактовой шиной 7, D-входы подключены соответственно к выходам элементов 2И-ИЛИ 8-13, а единичные выходы— к выходным шинам 14-. 19; шина 20 обратного хода соединена с первыми входами первых элементов И элементоь

2И-ИЛИ 8-13, а шина 21 прямого хода с первыми входами вторых элементов И элементов 2И-ИЛИ 8-13. Второй и третий входы первых элементов И элементов 2И-ИЛИ 8-13 соединены соответственно с нулевыми выходами D-триггеров 4 и 5; 5 и б; б и 1; 1 и 2;

2 и 3; 3 и 4, а второй и третий входы вторых элементов И элементов

2И-ИЛИ 8-13 соединены соответственно . c нулевыми выходами D-триггеров 3 и

4; 4 и 5; 5 и б; б и 1; 1 и 2; 2 и 3.

Нулевые выходы D-триггеров 6,5 и 4 соединены с R-входами соответственно D-триггеров 3,2 и 1. 35

Функционирование двенадцатитактного реверсивного распределителя импульсов осуществляется следующим образом.

В начальный момент времени D-триг- 40 геры 1 и 2 находятся в единичном состоянии, а Р-триггеры 3-6 — в нулевом. указаны единичные выходы D-триггеров 1-6) . При смене полярности на шинах

20 и 21 наблюдается обратная последовательностьь 12-6 1 2-6 1-5 6 1-56- 45645-345-34-234-23-123.-12. ° . В двенадцатитактном реверсивном распределителе импульсов некоторые запрещенные комбинации вовсе невозможны: llllll

110111 100111 и т.д. Из других запрещенных комбинаций (например 000001) переход к нормальному рабочему режиму осуществляется первым же тактовым импульсом. Третьи запрещенные комбинации переводятся вначале в полный сброс D-триггеров, а затем — в рабочие комбинации (например 010101-

- 000000 - 000111).

Таким образом, предлагаемый реверсивный распределитель импульсов по сравнению с известным отличается повышенной помехоустойчивостью.

Формула изобретения

Двенадцатитактный реверсивный распределитель импульсов, содержащий шесть D-триггеров, С-входы которых соединены с тактовой шиной, D-входы подключены соответственно к выходам элементов 2И-ИЛИ, а единичные выходы — к выходным шинам, шина обратноro хода соединена с первыми входами первых элементов И элементов 2И-ИЛИ, а шина прямого хода — c первыми входами вторых элементов И элементов

2И-ИЛИ, причем второй и третий входы первых элементов И элементов 2И-ИЛИ соединены соответственно с нулевыми выходами четвертого и пятого, пятого и шестого> шестого и первого, первого и второго, второго и. третьего, третьего и четвертого D-триггеров, а второй и третий входы вторых элементов И элементов 2И-ИЛИ соединены соответственно с нулевыми выходами третьего и четвертого, четвертого и пятого, пятого и шестого, шестого и первого, первого и второго, второго и третьего D-триггеров, о т л и ч аю шийся тем, что, с целью повышения помехоустойчивости, нулевые выходы шестого, пятого и четвертого

D-триггеров соединены, с R-входами соответственно третьего, второго и первого D-триггеров.

Источники информации, принятые во внимание при экспертизе

1. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М., Советское радио, 1973, с, 211, рис. 6.9.

2. Авторское свидетельство СССР

Р 593314, кл. Н 03 17/62, 20.11.75 (прототип) .

980287

Г1

Составитель В. Чачанидзе

Редактор М. Рачкулинец Техред М.Гергель ЕорректорМ. Шарами

Заказ 9381/48

Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал- ППП Патент, г. ужгород, ул. Проектная, 4