Управляемый делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соаетскнк

Соцкалисткческик

Республик

<1!980290 (61) Дополнительное к авт. свид-ву— (22) Заявлено 20. 03. 81 (21 ) 3262314/18 21 с присоединением заявки М (233 Приоритет

Опубликовано 07.12,82. Бюллетень Но 45

Дата опубликования описания 07.12.82 И}М.К .

Н 03 К 23/00

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 621,374 ° 44 (088. 8) (72) Авторы . изобретения

A.Â. Шанин и Г.П. Митин, (71) Заявитель (54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ

ИМПУЛЬСОВ

Изобретение относится к импуль сной технике и может быть использовано в системах синхронизации цифровых устройств в качестве делителя частоты с переменным коэффициентом деления.

Известен делитель частоты следования импульсов, содержащий счетчик, дешифратор, триггер и элементы И (11.

Наиболее близким по технической сущности к изобретению является уп. равляемый делитель частоты следования импульсов, содержащий счетчик импульсов, выход которого соединен с выходной шиной делителя частоты, триггер, выход которого соединен с первым входом элемента И, блок формирования кода поправки, вход котоpî à, соединен с шинами кода деления, а выход — с информационными входами счетчика импульсов, линию задержки, вход которой подключен к выходной шине делителя частоты, а выход соединен с вторым входом элемента И и .с одним входом триггера, второй вход которого через инвертор соединен с выходной шиной делителя частоты (2).

Недостатком данного делителя частоты является ограниченное быстродействие из-за наличия в схеме линии задержки.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что в управляемый делитель частоты следования импульсов, содержащий триггер, прямой выход которого соецинен с первым входом первого элемен та И, блок формирования кода поправки, группа входов которого соединена с шинами кода деления, а вы ходы — с информационными входами счетчика импульсов, введен второй

15 элемент И, первый вход которого соединен с инверсным выходом триггера, второй вход — с вторым входом первого элемента И и входной шиной, а выход — с синхровходом счетчика импульсов и первым входом триггера, второй вход которого соединен с выходом счетчика импульсов, тактовый вход которого подключен к выходу первого элемента И.

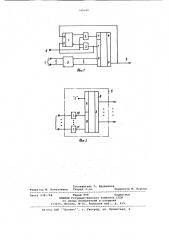

При этом блок формирования кода поправки выполнен в виде сумматора, первая группа входов которого соединена с выходами соответствующих инверторов, входы которых являются группой входов блока формирования

980290 кода, взваля группа входов — с шинами кода константы, а выходы являются выходами блока формирования ко да поправки.

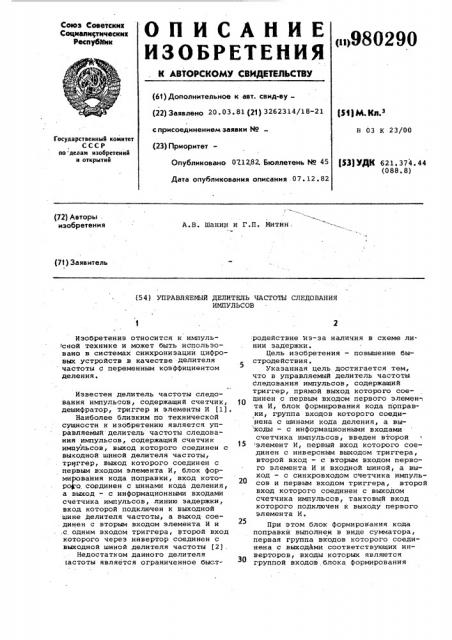

На фиг. 1 представлена структурная схема предлагаемого делителя 5 частоты; на фиг. 2 — блок формирования кода поправки.

Управляемый делитель частоты содержит триггер 1, элементы И 2 и 3, счетчик 4 импульсов, блок 5 формиро- IO вания кода поправки, входную шину 6, шины 7 кода деления и выходную шину 8.

Блок формирования кода поправки содержит двоичный сумматор 9, инвер торы 10 и 11.

Делитель работает следующим образом.

Предположим, триггер 1 находится в нулевом состоянии, импульсы сче- 2О та поступают по шине 6. Первый поступающий импульс проходит через открытый элемент 3 на синхровход счетчика 4. Своим передним фронтом этот им,пульс записывает в счетчик 4 код поправки, сформированный блоком 5, а задним фронтом переключает триггер 1 в единичное состояние, так что вход, ные импульсы, начиная со второго, поступают через элемент 2 на тактовый вход счетчика 4.

Импульс переполнения с выхода счетчика поступает на шину 8 и своим задним фронтом переключает триггер 1 в нулевое положение. -Далее работа схемы происходит аналогично. 35

Схема формирования кода поправки преобразует код деления, поступающий по шинам 7, в код поправки, равный

2 -K +1 = K +1+1 Ъ+2, 40 и Д д где К вЂ” код коэффициента деления;

n — разрядность счетчика.

Предлагаемый управляемый делитель частоты отличается повыаенным

45 быстродействием и может применяться в системах автоматики и импульсной техники для получения любого целочисленного коэффициента деления частоты следования импульсов.

Формула изобретения

1. Управляемый делитель частоты следования импульсов, содержащий триггер, прямой выход которого соединен с первым входом первого элемента

И, блок формирования кода поправки, группа входов которого соединена с шинами кода деления, а выходы — с информационными входами счетчика импульсов, отличающийся тем, что, с целью повышения быстродействия, в него введен второй элемент И, первый вход которого соединен с инверсным выходом триггера, второй вход — с вторым входом первого элемента И и входной шиной, а выход — с синхровходом счетчика импульсов и первым входом триггера, второй вход которого соединен с выходом счетчика импульсов, тактовый вход которого подключен к выходу первого элемента И.

2. Делитель частоты по п. 1, о тл и ч а ю шийся тем, что блок фор. мирования кода поправки выполнен в виде сумматора, первая группа входов которого соединена с выходами соответствующих инверторов, входы которых являются группой входов блока формирования кода, вторая группа входовк шинам кода константы, а выходы являются выходами блока формирования кода поправки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 513507, кл. Н 03 К 23/00, 1974.

2 ° Авторское свидетельство СССР

9 524320, кл. Н 03 К 23/00, 1975.

Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 938) /46

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель О. Кружилина

Редактор М. Рачкулинец Техред Р,.Ач Корректор М. Иаро аи