Устройство для автоматического контроля цифроаналогового преобразователя

Иллюстрации

Показать всеРеферат

И С А Н И Е М981944

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 07.05.81 (2! ) 3288824/18-24 с присоединением заявки,%

- (23) Приоритет (и)м. кл .

605 B 2М02

РщудврстненныН квинтет

СССР ао амак изобретений и открытий

Опубликовано 15.12 82. Бюллетень № 4.-6

Дата опубликования описания 15.12.82 . (53) УДК621. ..327.8 (088.8) 1

Е

Г. Ф. Горбонос и Г. М. Щфсман г (72) Авторы изобретения

1

Всесоюзный электротехнический ййститут.им, B. И. Лвнина (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ

БИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ

Изобретение относится к автоматике и вычислитяльной технике и может быть; использовано для автоматического контроля работоспособности электронных устройств систем автоматики, регулирования и управления, в частности для определения отказов в устройствах со ступенчатым изменением выходного сигнала. Известно устройство для контроля цифровых схем, содержащее задатчик тестов, блок сравнения, блок ввода $1) .

Недостатком данного устройства является ограниченная область применения вследствии невозможности контроля цифроаналоговых преобразователей.

Наиболее близким техническим решением к изобретению является устройство для контроля радиоэлектронных блоков, содержащее компаратор, дифференциатор, индикатор 2) .

Недостатком данного устройства является низкая точность контроля вследствие того, что его абсолютная погрешность определяется величиной ступеньки, выходного напряжения генератора эталонного ступенчатого напряжения.

Бель изобретения — повышение точности контроля.

Поставленная цель достигается тем, что в устройство для автоматического контроля цифроаналогового преобразователя, содержащее дифференпиатор, компара1о тор и индикатор введены формирователь импульсов, логический блок и элемент

HIIH, соединенный выходом со входом ин. дикатора, первым входом через компаратор - с выходом дифференциатора и с входом формирователя импульсов, соединенного выходом с первым входом логического блока, выход которого подключен к второму входу элемента ИЛИ, второй вход - к входу контролируемого xrpeo6pa-;

2О зователя, соединенного выходом с входом дифференциатора.

Причем логический блок содержит элемент ИЛИ-НЕ, элемент ИЛИ ИСКЛЮ44 4

Дифц)еренпиатор 3 фиксирует любые скапси выходного czrнала контролируемого преобразоватепя в виде импульоов, амплитуда которых пропорциональна величине скачков сигнала источника

При контроле преобразователя 1 допускается, что сбой в работе реверсивного счетчика этого преобразователя может произойти только в младшем разряде.

Сбой в работе преобразователя 1, например, из-аа сбоя в любом разряде его счетчика контролируемого устройства, приводит z тому, что выходной сигнал его имеет увеличеттньтй скачок, что вываляется коьптаратором 4 в виде иъптульса на его выходе (см. фиг. З„поз. 3, 4 р момент 4 >). Далее выделенный импульс, пройдя через элемент ИЛИ 7, поступаеФ на индикатор 8 и фиксируется как неисправность контролируемого устройства

Одновременно любые скачки выходного сигнала контролируемого преобразователя .

1, выявлените диффереттпиатором 3, поступатот на вход формирователя 5 и преобразуются в нормированные короткие логические импульсы.

Далее полу тетптые логические тпптульсы поступают на вход логического блока 6, работающего по следующему алгоритмуо

При отсутствии тптипиирующих командтпж сигналов со входа 2 скачки выходного:, сигнала контролируемого преобразовате- ля 1 (а, следовательно, и импульсы на выходе формирователя 5) должны соответствовать. Любой ложный скачок, например в момент 4 (фиг. 3), свидетельс твует о неисправности контролируемого преобразователя 1, отмечается в виде логического сигнала отказа на выходе блока 6 и, пройдя по второму входу логического элемента ИЛИ, фиксируется индикатором 8.

При появлении книпиирутотцего команд- ного сигнала логический блок 6 формирует сигнал отказа, если будет пропущен хотя бы один скачок в течение времени сушествования командного сигнала (например в момент $, $, - ) на фиг. 3).

Указанный алгоритм обесйечивается логическим блоком 6.

Логический блок 6 работает следующим образом.

При отсутствии инипиирующего zoмащцтого сигнала на входе 2 выход триггера 1 1 устанавливается (логичес ким сигналом 1 на входе 5 триггера

11) в состояние логической "1, что

3 9819

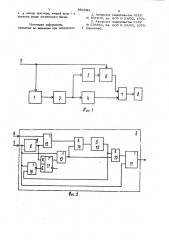

ЧИТЕЛЬНОЕ, rrepsrN u второй одновибратсры, первый и второй элементы ИЛИ, первый и второй элементы И. триггер, соединетптьтй <) -входом с выходом элемет, та ИЛИ-НЕ, прямым выходом с первым входом первого элемента ИЛИ, соединенного вторым входом с вторым входом логического блока, входом первого одновибратора, первым входом элемента

ИЛИ HE и первым входом элемента ИЛИ

ИСКХ1К)ЧИТЕЛЬНОЕ, соециненного вьтхо= дом с выходом логического блока, вторьтм входом «с выходом первого элемента И, соециненного непосредственно пер= вым НхороМ с вторым вхо,цом элемента 15

ИЛИ-НЕ, а через второй одновибратор с выходом второго элемента И, соединенного первым входом с выходом первого элемента ИЛИ и вторым входом первого злам<- и Ра И в торьтм входо<м .," выходов< 0

; р<)) о злем<ента ИЛИ, ттервыи ьхот которого подключен к выходу первого одновпбратора ц Q -входу триггера, второй вхо, :., — :, первому входу логического бло--. ка "5

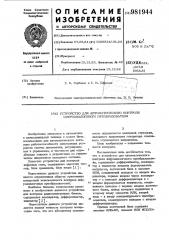

На фиг, 1 приведена блок-схема стройства*, тта фиг. 2 = нр)инттипиальная схеМс. Icc! Ичест<о. о блот<а HG фиг . 3 вре мелпые диаграммы работы устройства.

Устройс тво,цля контроля преобразова- М тели 1 содержит вход 2, дифференщжтор

3, компаратор 4, формирователь итптуль=

cов, ). логический блот< 6з элемент ИЛИ

7, тпт,цикато1-) 8, первый 9 и второй 10 оцновибраторы триггер 1 1 v торой 12 и первый 13 элементы ИЛИ, второй 14 и ттервттй 15 злеметттьт И, элемент ИЛИ Щ16, элемент ИЛИ ИСКЛЮЧИТЕЛЬНОЕ 17Устройство работает следутоитим образом 46

Контролируемый преобразователь 1 содержит, наттример, двоичный счетчик и преобразователь двоичный код-напряжение и работает следующим образом: при отсутствии инпциирутощих командных сигна лов на входе 2 выходной.сигнал контролируемого преобразователя имеет неизмен. ное постоянное значение (на любом уровне во всем диапазоне заботы контролируемого источника); при появлении инипттирутощего командного сигнала ("прибавить-убавить ) выходной сигнал сразу же (например, в интервале периода следования тактовых импульсов счетчика контролируемого преобразователя) начи5$ пает изменяться ступенями строго дозированной величины, соответствующей, например, младшему разряду счетчика контролируемого преобразователя. о годности преобразователя 1 на каждом из тактов изменения его выходного с»»гнала, причем точность контроля определяется не и»агом квантования эталонного сигнала, а чувствительностью компаратора 4 и может быть в зависимости от его выполнения сушественно повышена,, Таким образом, введение блоков 5, 6 повьш!ает точность контролч вь»хладного ступенчато-меняюшегося напряжения преобразователя 1.

1. Устройство для автоматического контроля цифроаналогового преобразова-. теля, содержашее дифференциатор, компаратор и индикатор, о т л и ч а ю ш ее с я тсм, что, с целью повышен»»я точности контроля, в устройство введены формирователь импульсов, логический блок и элемент ИЛИ, соединенный выходом с входом индикатора, первьп.» входом через компаратор - с выхоцом дифференш»атора и с входом формирователя имп чьсов соединенного выходом с первьг», I ьходом логического блока, выход кототюго подключен к второму входу элемента

ИЛИ, второй вход — к входу контролируе мого преобразователя, соед»»неьп»ого выходом с входом дифференпиатора.

2. Устройство по и. 1, о т и и ч а *ю ш е е с я тем, -»To логический блок содерж1»т элемент ИЛИ-НЕ, элеме»»т ИЛИ

ИСКХПОЧИТЕЛЬНОЕ, первьп» и второй одновибраторь», первый и второй элементы ИЛИ, первый и второй эпементь» И и триггер, соединенный Ь -входом с выходом элемента ИЛИ-НЕ, прямым выходом - с первым входом первого элемента ИЛИ, соединенного вторым входом с . вторым входом логического блока„входом первого одновибратора, первым входом элемента ИЛИ-HE. и с первьы входом элемента ИЛИ ИСК1ПОЧИТЕЛЬНОЕ, сое диненного вь!ходом с входом логического блока, вторъ»м входом - с выходом первого элемента И, соединенного непосредственно первым входом с вторым .входом элемента ИЛИ-НЕ, а через второй одновибратор - с выходом второго элемента И, соединенного первым .входом

1л птл с выходом первого элемента ИЛА и с вторым входом первого элемента И, вто- . рым входом — с выходом второго элемента ИЛИ, первый вход которого подключен к выходу первого одновибратора

3 !

5 О& 194 позволяет логическому элементу И 14 пропустить любой ложный импульс по входу (т.е. выходной сигнал формирова; тепя 5) через логический элемент ИЛИ

12 и запустить одновибратор 10. Им- . % пульс с выхода одновибратора 10, пройдя через логический элемент И 15, поступает на один из видов логического элемента ИЛИ ИСКЛ10ЧИТЕЛЬНОЕ 17, на другой вход которого подается сиг)0 нал входа 2. На выходе элемента 17 формируется импульс отказа при несов-. падении сигналов на его входах.

При проявлении инициируюшего команд. ного сигнала на вход 2 запускается одно1$ вибратор 9. Короткий логический импульс с выхода одновибратора 9 проходит перез логические элементы 12 и 14 и запускает одновибратор 10 (независимо

20 от того, имеются ли скачки сигнала, контролируемого пр,",>бразователя 1, т.е. появляются ли импульсы на входе o j, Нормально функцио-.»ируюший контролируемый. преобразователь 1 должен сразу же

25 скачками изменять свой выходной сигнал.

Поэтому периодически (например, с тактовой частотой работы счетчика преобразователя 1) по входу»".! должны поступать импульсы, свидетельству-юшие о наличии скачков выходного сигнала преоб30 разователя Й, и поддерживать логический сигнал "1 на выходе одновибратора 10.

В случае же пропуска и!п»ульса по входу 4, например, в момент 4 (на фиг. 3) одновибратор 10 через заданное 35, время на своем выходе устанавливает (в момент . ) логический сигнал 0".

При этом несовпадение сигналов на входах логического элемента 17 приводит к формированию на его выходе сигна- 40 ла отказа.

Наличие логического элемента ИЛИ-НЕ

16, связанного своим входом с выходом одновибратора 10, необходимо для того, чтобы не появился ложный сигнал отказа 45 в момент снятия инициирующего командного сигнала со входа 2, пока одновибратор 10 не установит на своем выходе логический сигнал "0 (фиг. 3, поз. 1013 в период - ). 30 !

Таким образом, блок 6 контролирует . »»аличие необходимого количества ступенек" выходного сигнала преобразова.теля и обнаруживает пропадание ипи до%5 бавпение "ступенек". В то же время компаратор 4 контролирует амплитуду каж дой ступеньки". Наличие сигнала годности с блоков 6 и 4 свидетельствует

Формула изобретения

7 981946 и р -входу триггера, второй вход — к первому входу логического блока. go

NcTo информапии принятые во внимание при экспертизе

1. Авторское свидетельство СССР

498619, кл. 695 В 23/02, 1971.

2. Авторское свидетельство СССР

Ра Q2g8g1 кл. QQQ Q 2 j/Q2 1@73 (прототип}.

981944

ВНИИПИ Заказ 9709/66 Тираж 914 Подписное, Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4