Стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ р>981974

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 28.01.81 (21) 3240015/24-07 с присоединением заявки ¹ (23) Приоритет

Опубликовано 151282. Бюллетень ¹ 46

Дата опубликования описания 15. 12.82

th)) М Кп 3

G 05 Р 1/56

Государственный комитет

СССР но делам изобретений и открытий

153) УДК 621. 316. .722.1(088,8) (72) Авторы изобретения а (.

В.A. Áû÷êoâ (71) Заявитель (54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к стабилизированным источникам электропитания постоянного тока.

Известны стабилизаторы напряжения, содержащие регулирующий орган, усилитель обратной связи с цепью амплитудно-частотной коррекции, источник опорного напряжения, делитель выход. ного напряжения (1 ).

Наиболее близким по технической сущности к изобретению является стабилизатор постоянного напряжения, содержащий регулирующий орган, управляющий вход которого соединен с выходом однокаскадного дифференциального усилителя, один вход которого подключен к выходу перного делителя напряжения, нторой вход — к блокироночному конденсатору и к выходу Nкаскадного дифференциального усилителя,. первый вход которого подключен к источнику опорного напряжения, а второй вход — к выходу нторого делителя напряжения (2 ).

Недостаток известных стабилизаторов заключается н низких динамических параметрах стабилизатора.

Целью изобретения янляется улучшение динамических параметров стабилизатора.

Поставленная цель достигается тем, что в стабилизаторе постоянного напряжения второй делитель напряжения и источник опорного напряжения соединены с измерительными выводами стабилизатора для подключения контрольных цепей к нагрузке, а заземляющий вывод блокироночного конденсатора и первый делитель напряжения подключены к силовым цепям от стабилизатора, соединенным с выводами для подключения нагрузки.

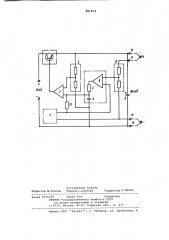

На чертеже приведена электрическая схема стабилизатора постоянного напряжения.

Стабилизатор содержит регулирующий орган 1, однокаскадный дифференциальный усилитель 2, выход которого соединен со входом регулирующего органа 1, первый вход — с выходом первого делителя напряжения 3, второй вход — к первому выводу блокировочного конденсатора 4, и через резистор 5 к выходу — каскадного дифференциального усилителя 6, первый вход которого подключен к источнику опорного напряжения 7, а второй вход ко второму делителю напряжения 8.

Стабилизатор содержит также конденсатор фильтра 9 и резистор 10, вклю98197 4 ченный между вторым входом усилителя 2 и источником опорного напряжения 7. При этом второй делитель напряжения 8 и источник опорного. напряжения 7 соединены с измеритель-. ными выводами стабилизатора 11 и 12, которые цепями контроля связаны с нагрузкой. Первый делитель напряжения 3 и второй вывод конденсатора

4 соединены с силовыми цепями стабилизатора, в данном случае с вы- 1О ходньми силовыми выводами для подключения к нагрузке.

В динамическом режиме работы стабилизатора на быстрые изменения режима нагрузки реагирует усилитель 2, 15 управляемый разностным сигналом, полученным путем сравнения части выходного напряжения, поступающего с первого делителя напряжения 3, с напряжением на блокировочном конденса- gQ торе 4, выполняющего здесь вторую функцию источника опорного напряжения. Полученный разностный сигнал усиливается усилителем 2, выходным напряжением которого управляется регулирующий орган 1, компенсирующий изменение выходного напряжения стабилизатора. Благодаря высокому быстродействию однокаскадного дифференциального усилителя 2, динамическая ошибка будет невелика, хотя его коэффициент усиления существенно ниже результирующего коэффициента усиления усилителей 2 и 6. Поскольку усилитель 2 определяет стабильность выходкого напряжения источника в динамическом режиме, то величину блокировочного конденсатора 4 в цепи усилителя 6 можно выбирать большей величины, что повышает устойчивость стабилизатора. 40

Одновременно сигнал ошибки выходного напряжения стабилизатора выделяется на входе усилителя 6 путем сравнения части выходного напряжения, поступающего со второго делителя напряжения 8 с напряжением, поступающим с источника опорного напряжения 8 с напряжением, поступающим с источника опорного напряжения 7. В результате между выходом усилителя 6 и источником опорного напряжения 7, на балластном резисторе 10 будет выделяться усиленный сигнал ошибки, действующий на входе усилителя 6. Указанное напряжение корректирует величину опорного напряжения, действующего на входе однокаскадного дифференциального усилителя 2, в результате чего и достигается высокая точность стабили- 60 зации по среднему значению выходного напряжения стабилизатора. Теперь влияние высокой постоянной времени усилителя б нЕ приведет к ухудшению динамических параметров стабилизатора, поскольку усилитель 6 будет осуществлять коррекцию хотя и с преж ней постоянной времени, но уже малой ошибки выходного напряжения стабилизатора, соответствующей статической ошибке, обусловленной коэффициентом усиления однокаскадного дифференциального усилителя 2, понижая ее до статической ошибки, определяющим коэффициентом усиления усилителей 2 и б, В качестве резисторов второго делителя 8 следует применять проволочные резисторы, имеющие малый температурный коэффициент сопротивления, а в качестве резисторов первого делителя 3 — непроволочные, имеющие малую индуктивность.

Данное техническое решение позволяет улучшить динамические параметры стабилизатора, повысить

его устойчивость и сократить габариты за счет сокращения объема, занимаемого конденсаторами, включенными на выходе стабилизатора .

Формула изобретения

Стабилизатор постоянного напряжения, содержащий регулирующий орган, управляющий вход которого соединен с выходом однокаскадного дифференциальнОго усилителя, один вход которого подключен к выходу первого делителя напряжения, второй вход к блокировочному конденсатору и к выходу N-каскадного дифференциального усилителя, первый вход которого подключен к источнику опорного напряжения, а второй вход — к выходу второго делителя напряжения, отличающийся тем, что, с целью улучшения динамических параметров стабилизатора, второй делитель напряжения и источник опорного напряжения соединены с измерительными выводами для подключения контрольных цепей к нагрузке, а заземляющий вывод блокировочногo конденсатора и первый делитель напряжения подключены к силовым цепям стабилизатора, соединенным с выводами для подключения нагрузки.

Источники информации, принятые во внимание при экспертизе

1. Аналоговые и цифровые интегральные схемы. Под ред. Якубовского С.В., М., Советское радио, 1979, с. 279-281, рис. 4.65,б, 2. Назаров С.В. Транзисторные стабилизаторы напряжения, М., Энергия, 1980, с. 65, рис. 46.

981974

Составитель В.Есин

Редактор М.Товтин Техред И.Коштура

Корректор О.Билак

Заказ 9710/67 Тираж 914 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4