Устройство для сложения чисел по модулю

Иллюстрации

Показать всеРеферат

(981994

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сеюз Советских

Сфциалистическии

Реснублик (е1) Дополнительное к авт. свид-ву(22) Заявлено 10. 04. 81 (21) 3273877/18-24

Р М К з с рисоединением заявки М(23) Приоритет

G 06 F 7/49

Государственны% нойнтет

CCCI но делай нзобретеннй н отирытнй

Опубликовано 15.12Я2. Бюллетень Мо46

Дата опубликования описания 15. 12. 82 ($3) УДК681. 325. .5:(088.8) (72) Авторы изобретения

В.И. Рабинович и С.О. Веселовский 1 >e(.Qfgg fQ p

g sir ; . ")(%г лсс;р, ." и

Новосибирский электротехнический ин титуфвд н@

Отр;.4

1 (73) Заявитель (54) УСТРОИС1 ВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ

Изобретение относится к вычислительной технике и может быть ис« пользовано для выполнения операций сложения и вычитания двоичных данных по модулю 2 --1 (и - целое, болыаее и единицы) .

Известно устройство для сложения чисел, состоящее из двух сумматоров и мультиплексора и позволягсщее получить сумму двух чисел, представленных в системе оснтаточных классов остатками K=amod(2-1) и I bmod(2"-1), при этом операция суммирования выполняется на двух сумматорах одновре-. менно, причем на первом суыгаторе выполняется действие K+I на второмK+I-р (р 2"-1 модуль), при этом sa истинный принимается результат одного из этих сумматоров в зависимости от знака результата второго сумматора (1) .

Недостатком устройства является невысокое быстродействие за счет того, что операция K+I-р осуществля» ется путем последовательного включения сувматоров.

Наиболее близким к данному изобретению техническим решением является устройство для обработки данйых в . системе остаточных классов по модулю 2 -1, в котором используется и-рази рядный сумматОр, на одни входы которого подается сигнал K=amod(2"-1), на другие — сигнал I=bmod(2"-1),при-. чем выход переноса старшего разряда связан со входом переноса младшего разряда, выходы сумматора связаны со входами п-входовой схегы И-HE u

1О первыми входами и двухвходовых схем

И, выходы которых являются выходами. устройства, вторые входы двухвходовых схем И связаны с выходом схемы, И-НЕ.Сигналы К и I могут подаваться на вход сумматора как в прямом, так

И и в инверсном виде, что позволяет с помощью указанного устройства осу-. ществлять операции сложения,вычитания, кодирования и декодирования сигналов по модулю (2 .

Однако, это устройство не позволяет повысить быстродействие по сравнению с предыдущим устройством,так как хотя операции суммирования проводятся на одном сумматоре, но,они выполняются (учитывая перенос) последовательно два раза.

Цель изобретения - повыаение быстродействия.

Поставленная цель достигается .тем, что в устройство для сложения чисел

981994

Формула изобретения по модулю, содержащее сумматор по модулю, элемент И-НЕ, первую группу элементов И, причем первая и вторая группы входов сумматора по модулю соединены соответственно с первой и второй группой информационных входов устройс гва, выходы суммы сутиатора по модулю соединены со входами элемента И-НЕ, выход которого соединен с первыми входа ли элементов И первой группы, выходы которых являются выходами устройства, введены группа сумматоров по модулю два, нторая группа элемейтов И, причем первые нходы сумматоров по модулю два группы соединены с соответствующими выходами суммы сумматора по модуля, выходы элементов И второй группы подключены ко вторым входам соотнетствующих сумматоров по модулю дна группы, начиная со второго, выходы сумматоров по моду- 20 лю два группы подключены ко вторым входам соответствующих элементов И первой группы, j-e входы i-x элементов И второй группы ()=1...:.,i, i=1...,, n- 1) подключены к j-м выхо- 25 дам суммы сумматора по модулю, (j+1)-е входы элементов И второй группы соединены с выходом переноса сумматора .по. модуля и вторым входом первого сумматора по модулю два 30 группы.

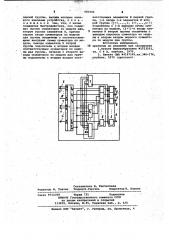

На чертеже представлена блок-схема устройства ° устройство содержит сумматор по модулю 1, элемент И-НЕ 2, группу эле-.35 ментов И 3, группу элементов И 4, группу сумматоров по модулю два 5, информационные входы 6 и 7, выходы 8.

Устройство работает следующим образом. 40

На выходы 6 и 7 подаются соответственно сигналы КО,К,...,К„ л, где

I=bmod(2 -1)(n — разрядность суммаИ тора 1) . Эти сигналы могут подавать- 4 ся на вход сумматора как в прямом, так и в инверсном виде, что позволяет производить. не только операция сложения, но и вычитание.

На выходах сумматора 1 возможны следукщие,соотношения между результатом сложения и величиной основания системы р, равной 2"-1:

K + I.(p

К+1р

К + I rAMi б где И - модуль сумматора 1, M=P+1 Z

В первом случае на выходе перено- са (Р„.,) сумматора 1 оказывается ло-. фО гический ноль, что приводит к появлению логического нуля на выходах элементов И.4 и на первых входах сумматоров по модулю два 5 ° В. ре зультате на выход сумматоров по мо- б5 дулю два 5 проходит код с выхода сумматора 1 и поступает на выходы устройства 8 через открытые элементы И

3 логической единицей с выхода элемента И-НЕ 2. На выходе элемента

И-HE 2 — логическая единица, так как хотя бы на одном выходе сумматора 1 логический ноль (K+ I 2"-1) .

Во втором случае (K+I=2"-1) на всех выходах сумматора 1 логическая единица (перенос отсутствует) и, следовательно, на выходе элемента

И-НЕ 2 — логический ноль, который закрывает элементы И 3, что приводит к появлению на всех выходах устройства логических нолей.

В третье л случае К+1>2, но

И

К 2 -. 1, Г 2 -1, следовательно и .!

2" K+I 6 2" -2. Результат. операции на сумматоре 1 равен

С = K+I-M=K+I-2 =K+I-(2 -1)-1;

П .п

С = K+I-1mod(3 - 1), т.е. меньше истинного на единицу, следовательно необходимо прибавить в младший разряд единицу, которая формируется в разряде переноса сумматора 1. На входах элемента И-НЕ 2 будет хотя бы один логический ноль, так как 2" ЯК+1 с 2 "2 что вызывает появление на его выходе логической единицы, которая открывает элементы

И 3. На выходе младшего разряда устройства будет результат сложения выходного сигнала младшего разряда сумматора 1 и выходного сигнала разряда переноса. На элементах И 4 формируется перенос из предыдущих разрядов таким образом, что на выходе этих элементов .будет логическая единица в том случае, если логическая единица присутствует на выходе всех предыдущих младших разрядов сумматора 1 и на выходе переноса сумматора 1.Таким образом, на выходах, устройства 8 окажется код, равный K+I-2"+1=K+I-р.

Таким образом,повышение быстродействия происходит за счет того, что суммирование выполняется только один раз, а возникший в его результате перенос учитывается при поМощи введенных в устройство сумматоров по модулю два 5 и элементов И 4.

Устройство для сложения чисел по модулю, содержащее сумматор по модулю, элеМент И-НЕ, первую группу ° элементов И, причем первая и вторая группы входов сумматора по модулю соединены соответственно с первой .и второй группой информационных входов устройства, выходы суммы сумматора по ьюдулю соединены с входами элемента И-HE выход которого соединен с первыми входами элементбв И

981994 первой группы, выходы которых являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит группу сумматоров по модулю два, вторую группу элементов И, причем первые входы сумматоров по модулю два. группы соединены с соответствующими выходами сумин сумматора по модулю, выходы элементов И второй группы подключены к вторым входам соответствующих сумматоров по моду лю два группы, начиная с .второго вы ходы сумматоров по модулю два группы подключены к вторым входам соот-

d ветствующих элементов И первой группы, j-е входы 1-х элементов И второй группы (j=1», 1 1=l,...,n- 1 ) подключены к j-м выходам суммы,сумматора по модулю, (j+1,)-е входы элементов И второй группы соединены с

- выходом переноса сумматора по модулю и вторым входом первого сумматора по модулю два группы.

Источники информации, 10 принятые во внимание при экспертизе

1.Патент Великобритании 91513101, кл. G 4 А, опублик. 1979.

2. Патент СНА 94187549,кл.346-176, (опублик. 1979 (прототип1.

Составитель В, Евстигнеев

Редактор М. Товтин Техред М.Гергель Корректор Н. Король

Заказ 9712/68. Тира к 731 Подписное

ВНИИПИ.Государственного комитета СССР по делам изобретений и открытий

113035, МОсква, Ж-35, Раушская наб., д,: 4/5

Филиал ППП "Патент"-, г. Ултород, ул. Проектная, 4