Псевдостохастический сумматор

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (>982003 (61) Дополнительное к авт. свид-ву (22) Заявлено 04. 05. 81 (21) 3282338/18-24

Р М К з с присоединением заявки Й9G 06 F 7/70

Государственный комитет

СССР по делам изобретений и открытий (23) ПриоритетОпубликовано 15,12.82. Бюллетень М 46 (53) УДК 681. 3 (088. 8) Дата опубликования описания 15.12.82

В.М.Ерухимович, В.Г.Казаков, 3.A.Ìàðòûíåíêo н A.Ã.Ðûãàëü (72) Авторы изобретения

4

Специальное проектно-конструкторское и тезснологическое бюро по погружному электрооборудованию для буренйя.екваж!ин и добычи нефти (71) Заявитель (54) ПСЕВДОСТОХАСТИЧЕСКИЙ СУММАТОР

Изобретение относится к вычислительной технике и может быть использовано в стохастических вычислительных машинах для суммирования К-чисел, представленных в двоичной форме.

Известны стохастические суммирующие устройства, которые содержат преобразователи число-вероятность,двоичные счетчики, логические элементы И, ИЛИ, НЕ, а также источники несовместных случайных последовательностей для обеспечения несовместимости последовательностей представляющих слагаемые Е12 и (2).

Недостатком указанных устройств является низкое быстродействие,связанное с представлением суммируемых чисел случайными последовательностями, при котором точность вычислений зависит от длины декодируемой последовательности, представляющей результат вычислений.

Наиболее близким по технической сущности к изобретению является псевдостохастическое суммирующее устройство, содержащее по числу слагаемых и-разрядные регистры, и-разрядный сдвиговый регистр с обратной связью, группу элементов И, и-разрядный счетчик, выходы разрядов которого явля-, ются выходами устройства, коммутаторы,. первые входы которых соединены с выходами одноименных п-разрядных регистров, а вторые входы соединены с выходами группы элементов И, входы которых соединены соответственно с выходами разрядов сдвигового регистра с обратной связью. Устройство содержит также группу сумматоров по модулю два, дешифратор, вторую группу элементов И для образования К несовместных в каждом такте псевдослучайных последовательностей, цредставляющих К слагаеиих с весовым коэффициентом 2, где — является целой частью 1о8 К. Суммирование осуществляется с помощью k-входного: элемена та ИЛИ, выход которого соединен со входом счетчика, 30 Р тактов в счетчике воспроизводится результат суммирования с погрешностью 2 ". При за» данной точности вычислений быстродействие данного псевдостохастического устройства превышает быстродействие известных устройств (3).

Однако недостатком устройства является отсутствие обратной пропорциональности ме кду весовым коэффициейтом равным 2, и количеством суммируеьвис чисел К, так как Р равно

982003 целой части log К, что приводит к трудностям при вычислениях, связанных с масштабированием результатов, а также к нерациональному использованию оборудования.

Умножение и-разрядных чисел на весовой коэффициент 2 при 1 близких к и приводит к потере информации, особенно в случаях, когда производится обработка малых значений операндов. При большом числе сумми- 10 руемых операндов аппаратурные затраты на известный сумматор существенно возрастают за счет усложнения бло- ков сумматоров по модулю два и дешифратора. 15 !

Цель изобретения — упрощение сумматора и расширение функциональных возможностей за счет получения при суммировании весового коэффициента, обратно пропорционального коли-20 ,честву слагаемых.

Поставленная цель достигается тем, что псевдостохастический сумматор, содержащий блок и-разрядных регистров (n=1,2,3....) группу коммутаторов, и-разрядных чисел, первые входы разрядов каждого из которых соединены с выходами сЬответствующего п-разрядного регистра группы, группу элементов И, выходы которых соединены в об-30 ратном порядке со вторыми входами младших (n-1) разрядов коммутаторов группы, сдвиговый регистр с обратной связью, прямой выход первого разряда которого соединен со вторыми входами 35 и-ых разрядов коммутаторов, группы, инверсный выход первого разряда — соединен с первыми входами элементов И группы, прямой выход второго разряда соединен со вторым входом первого эле- 40 мента И группы, прямой выход каждого

i-ro (i = 1,2,....n) разряда, начиная с третьего, - соединен со входом вторым (i-1)-ro элемента И группы, а инверсный выхоц каждого i-го разряда, 45 начиная со второго, — соединен с (i+1)-ми входами старших по номеру элементов И группы, начиная с i-ro, счетчик, установочный вход которого соединен с выходом (n-1)-ro элемента

И группы, а выходы - являются выхода50 ми сумматора, дополнительно содержит цифро-аналоговый преобразователь, нульорган и суммирующий операционный усилитель, входы которого соединены с

-выходами соответствующих коммутаторов группы, а выход — соединен с первым входом нуль-opraHa.âõoäû цифроаналогового преобразователя соединены в обратном порядке с прямыми выходами сдвигового регистра с обратной 60 связью, а выход — соединен со вторым входом нуль-органа, выход которого соединен со счетным входом счетчика.

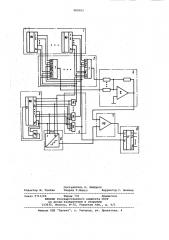

На чертеже. представлена блок-схема устройства. 65

Сумматор содержит группу 1 п-разрядных регистров (n=1,2,3...), группу 2 коммутаторов и-разрядных чисел, сдвиговый регистр 3 с обратной связью, группу 4 элементов И, цифро-аналоговый преобразователь 5, суммирующий операционный усилитель б, нуль-орган

7, счетчик 8.

Выходы и-разрядных регистров группы 1 соединены с первыми входами разрядов соответствующих коммутаторов группы 2, выходы которых соединены с соответствующими входами суммирующего операционного усилителя б. Прямой выход первого разряда сдвигового регистра 3 с обратной связью соединен со вторыми входами п-ых разрядов коммутаторов группы 2, инверсный выход первого разряда,. соединен с первыми входами элементов И группы 4, прямой выход второго разряда — соединен со вторым входом первого элемента И группы 4, прямой выход каждого i-го (i= 1,2,3...n) разряда, начиная с третьего - соединен со вторым входом (i-1)-го элемента И группы 4, а инверсный выход каждого i-го разряда, начиная со второго, — соединен с (i+1)-ми входами старших по номеру элементов И группы 4, начиная с i-го.

Входы цифро-аналогового преобразователя 5 соединены в обратном порядке с прямыми выходами сдвигового регистра 3 с обратной связью, а выход — соединен со вторым входом нуль-органа 7, первый вход которого соединен с выходом суммирующего операционного усилителя б, а выход — соединен со счетным входом счетчика 8. Установочный вход счетчика 8 соединен с выходом (n-1)-го элемента И блока 4 °

Сумматор работает следующим образом.

С помощью сдвигового регистра 3 с обратной связью групп 4 элементов

И, блока 2 коммутаторов двоичные коды чисел, содержащиеся в и-разрядных регистрах группы 1, преобразуются в К псевдослучайных последовательностей, математическое ожидание каждой из которых пропорционально соответствующему числу. Последовательности с выходов коммутаторов группы 2 поступают на соответствующи е входы суммирующего операционного усилителя б.

На выходе суммирующего операционного усилителя б образуется ступенчатое напряжение, амплитуда которого в данном также пропорциональна количеству импульсов на его входах. Напряжение на выходе суммирующего операционного усилителя б представляет собой псевдослучайный процесс с математическим ожиданием, пропорциональным сумме математических ожиданий входных последовательностей с весовым коэффициентом, обратно пропорциональным

982003

Формула изобретения

Псевдостохастический сумматор,со- 50 держащий группу и-разрядных регистров числу слагаемых. Измерение за 2"-<тактов математического ожидания процесса на выходе суммирующего операционного усилителя б производится путем его преобразования в псевдосдучайную импульсную последовательность. Для этого выходное напряжение суммирующего операционного усилителя б подается на первый вход нуль-органа 7, на второй вход которого поступает напряжение с выхода цифро-аналогового преобразователя 5, присоединенно го к разрядам сдвигового регистра с обратной связью в обратной последовательности их номеров по отношению к последовательности номеров разря- 15 дов, присоединенных к блоку 4 элементов И.

В результате сравнения указанных напряжений на выходе нуль-органа

:образуется псевдослучайная последо-,ф вательность, математическое ожидание которой пропорционально сумме исходных .чисел с весовым коэффициентом, обратно пропорциональным количеству слагаемых.

Предлагаемая схема соединений цифро-аналогового преобразователя с разрядами сдвигового регистра позволяет.обеспечить некоррелированность последовательностей на входах Зр суммирующего <операционного усилителя б и на выходе нуль-органа 7,Последовательность с выхода нуль-органа 7 поступает на счетчик 8, где декодируется в течение периода сдви- 35 гового регистра 3 с обратной связью.

В счетчике 8 за 2 и-1 тактов воспроизводится в двоичном коде результат суммирования.

Применение суммирующего операцион- 4р ного усилителя, нуль-органа и цифроаналогового преобразователя, соединенных по предлагаемой схеме, упрощает устройство и позволяет проводить операцию сложения К чисел с весовым коэф-45 фициентом, равным 1/К. (n=1,2,3...), группу коммутаторов и-разрядных чисел, первые входы разрядов каждого из которых соединены с выходами соответствующего п-разрядного регистра группы, группу элементов И, выходы которых соединены в обратном порядке с вторыми входами младших (n-1) разрядов коммутаторов группы, сдвиговый регистр с обратной связью, прямой выход первого разряда. которого соединен с вторыми входами п-х разрядов коммутаторов группы, инверсный выход первого разряда соединен с первыми входами элементов И группы, прямой выход второго разряда соединен с вторым входом первого эле- мента И группы, прямой выход каждого

i-ro (i=1,2,...,ï) разряда, начиная с третьего, соединен с вторым входом (i- 1)-ro элемента И группы, а инверсный выход каждого i-го разряда, начиная с второго, соединен.с (1+1)-ми входами старших по номеру элементов И группы, начиная с i-го, счетчик, установочный вход которого соединен с выходом (n-1)-ro элемента И группы, а выходы являются выходами сумматора отличающийся тем, что, с целью упрощения, сумматор содержит цифроаналоговый преобразователь, нульорган и суммирующий операционный усилитель, входы которого соединены с выходами соответствующих коммутаторов группы, а выход соединен с первым входом нуль-органа, входы цифроаналогового преобразователя соединены в обратном порядке с пряжами выходами сдвигового регистра с обратной связью, а выход соединен с вторык входом нульоргана, выход которого соединен со счетным входом счетчика.

Источники информации, принятые во внимание при экспертизе

1. Федоров P ° Ф., Яковлев В.В., Добрис Г.В. Стохастические преобразователи информации, Л., "Машиностроение", 1978, с. 15.

2. Гладкий В.С. Вероятностные вычислительные модели. М., "Наука", 1973, с. 104.

3. Авторское свидетельство СССР

Р 737948, кл. G 06 F 7/38, 1980 (прототип).

982003

Составитель О. Майоров

Техред К.Мыцьо Корректор С. Шекмар

Редактор N. Товтин

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Заказ 9713/69 Тираж 731 Подпи сн ое

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5