Устройство для распределения задач между процессорами

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ()982005 (61) Дополнительное к авт. свид-ву (22) Заявлено 25.05. 81 (21) 3291446/18-24 (51) М.Кл з с присоединением заявки М—

G 06 F 9/46

G F 15/20

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет -

Опубликовано 15.1282. Бюллетень М 46

Дата опубликования описания 15.12 82 (53) УДК681. 325 (088. 8) (72) Автор изобретения

В.A ° Богатырев

М

Ленинградский ордена Трудового Красного Знамени институт точной механики и оптики (71) Заявитель (54) УСТРОЙСТВО ДЗИ РАСПРЕДЕЛЕНИЯ ЗАДАЧ

МЕЖДУ ПРОЦЕССОРАИИ

Изобретение относится к вычислительной технике и может найти применение в отказоустойчивых многопроцессорных системах для распределе- 5 ния нагрузки между процессорами.

Известно устройство для распределения заданий процессорам, содержащее регистры, регистр сдвига, узел управления и логические элементы, 10 однако оно не может быть применено в качестве узла распределения функций (заданий) в вычислительных системах предусматривающих перераспредеl ление функций (кодов настроек на выполнение функций) после отказов t1).

Наиболее близким по технической сущности к изобретению является устройство для управления распределением задач, содержащее блок памяти, регистры, шифраторы, узел опроса, счетчик, узлы анализа столбцов и строк, схем сравнения, триггеры, логические элементы (2).

Однако это устройство характеризуется сложностью.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что устройство для распределения задач между процессорами, содержащее блок памяти и элемент И-НЕ снабжено дешифратором и блоком перебора перестановок, причем вход устройства соединен с входом дешифратора, группа выходов которого соединена с первой группой входов блока памяти, вторая группа входов которого соединена с группами выходов блока перебора перестановок и устройства, группа выходов блока памяти соединена с группой входов элемента И-HF., выход которого соединен с тактовым входом блока перебора перестановок.

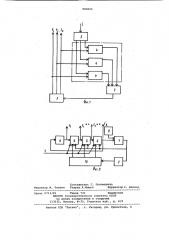

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - возможный вариант реализации блока перебора перестановок.

Устройство для распределения задач между процессорами содержит блок памяти 1 и элемент И-НЕ 2, блок перебора перестановок 3, элементы памяти 4 и дешифратор 5.

Блок перебора перестановок по фиг.2 содержит последовательно соединенные в кольцо регистры бл...6„,схему сравнения 7, дополнительный регистр

8, счетчик 9, блок памяти 10 (постоянной) .

Устройство предназначено для распределения вычислительной нагрузки

982005 ьв> ду процессорами вычислительной системы, в которой при потере какимлибо процессором (вычислительным модулем) способности выполнения возложенной на него функции производится перераспределение функций (заданий) между процессорами так, чтобы система восстановила, работоспособность

Формирование различных вариантов распределения функций производится 10 блоком перебора перестановок З.Код функции Е на.j-ом выходе которого

1 соответствует настройке j-ro процессора (на выполнение функции f ) . Проверка работоспособности распределения1 5 функций (перестановки) между процессорами происходит по информации, хра- нимой в блоке памяти 1. В блок памяти 1 заносится матрица памяти!И„ф элемент которой Ф„. = 1, если j-ый процессор способен выполнять функцию в противном случае „" = О, j ûé элемент памяти 4 соответствует j-му столбцу матрицы ПФ„.tl.

Запись "О" в ячейкУ 9„" происходит 25 при потере j-ым процессором способности выполнения возложенной на него функции, На вход дешифратора 5 подается код j, отказавшего процессора.

Возбужденным выходом дешифратора 5 осуществляется выборка j-ro элемента памяти 41. Адрес (соответствующий коду потерянной функции) подается с j-ro элемента блока перебора перестановок 3 на вход адреса элемента памяти 4 . При этом на выходы элемента памяти 4 подается "0" (содержимое выбранной ячейки Ч„j). На выходе элемента И-НЕ 2 формируется

"1", поступающая на тактовый вход блока перебора перестановок 3. Блок перебора перестановок 3 формирует следующий по порядку вариант распределения функций f,f ......f>.Если сформированное распределение функ ций является работоспособным, то на 45 выходах всех элемента. памяти 4л,..., ...,4и выдаются "1" и на тактовый вход блока перебора перестановок с выхода элемента И-HE 2 импульс не поступает. Если выработанный ва- 50 риант распределения функций не является работоспособным, то на выходе элемента памяти 4 содержатся "0" и на выходе элемента И-НЕ 2 вырабатывается "1", поступающая на такто- 55 вый вход блока перебора перестановок 3. При этом будет выработан следующий вариант распределения функций и т.д.

Блок перебора перестановок 3 предназначен для генерирования всевозможных перестановок кодов настроек Г Я И.

В блок постоянной памяти 10 построчно заносятся всевозможные перестановки кодов f,Е,..., fz, в ре-. гистры 6,,...,6 эачосятся коды

Ед, в регистр Π— код .. В регистрах б„,...,би происходит циклический сдвиг кодов 1,Е,...Юи, при поступлении в регистр б кода

Е на выходе схемы сравненйя 7 вырабатывается сигнал, по которому происходит запись в регистры б ...,6,„ следующей по порядку перестановки кодов т,f+,..., f и изменение адреса в счетчике 9. Такая схема обеспечивает перебор всевозможных перестановок кодов f„,f,,...,Е,„ (возможен перебор перестановок сповторяющимися элементами - кодами).

Данное устройство характеризуется упрощением, так как íà его реализацию требуется значительно меньше аппаратуры,чем на реализацию устройства — прототипа.

Данное устройство может найти применение при проектировании отказоустойчивых вычислительных систем, в которых восстановление работоспособности после отказа достигается перераспределением функций,возложенных на процессоры.

Формула изобретения

Устройство для распределения задач между процессорами, содержащее блок памяти и элемент И-НЕ, о т л и ч а ющ е е с я тем, что, с целью сокращения объема оборудования, оно содержит дешифратор и блок перебора перестановок, причем вход устройства соединен с входом дешифратора, группа выходов которого соединена с первой группой входов блока памяти, вторая группа входов которого соединена с группами выходов блока перебора перестановок и устройства, группа выходов блока памяти соединена с группой входов элемента И-HE выход которого соединен с тактовым входом блока перебора перестановок.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 629538, кл. G Об F 9/00, 1976.

2. Авторское свидетельство СССР

9 696471, кл. G 06 F 15/20, 1976 (прототип).

Составитель Г. ПономареВа

Редактор М. Товтин Техред К.Мыцьо Корректор С. Шекмар

Заказ 9713/69 Тираж 731 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва,. Ж-35, Раушская наб.(д. 4/5

Филиал ППП "Патент", .г. Ужгород, ул. Проектная, 4