Запоминающее устройство

Иллюстрации

Показать всеРеферат

О Il И С А Н И И ()982085

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски«

Социалистически«

Республми (61) Дополнительное к авт. синд-ву(22)Заявлено 24.04.81 (21) 3283!27/18-24 с присоединением заявки .%(23) Приорнтет

Опубликовано 15. т2. 82. Бюллетень № 46

Дата опубликования описания 15..12.82 (51)M. Кд.

G- 11 С 11/00

1Ьоударотю«ый комитет

СССР аю делам «зобретеиий и от«рыт«й (53) Уд К 681 327 .6(088.8) В.А.Авдеев,1

\

У

Таганрогский радиотехнический инстйтут=- „ им. В.Д.Калмыкова (72) Автор. изобретения (7l) Заявитель (54) ЗАПОМИНАЮЦЕЕ УСТРОЙСТВО

Изобретение относится к вычисли- тельной технике и может быть использовано для организации программной перестановки информации в режиме разделения времени в многопроцессор5 ных вычислительных системах, а также в автоматизированных телефонных станциях.

Известно устройство коммутации аналоговых блоков, содержащее считывающее устройство, выходы которого через дешифратор адреса шагового искателя и блок управления подключены к входам блока коммутации (1$ .

Однако данное устройство имеет низкое быстродействие, связанное с тем,что блок коммутации выполнен на шаговых искателях.

Наиболее близким к предлагаемому о является запоминающее устройство, содержащее накопитель, информационные. входы которого соединены с выходами первого регистра слова, а информационные выходы — с входами второго регистра слова, подключенного выходами к информационным выходам устройства, информационные входы которого соединены с входами первого регистра слова, первые адресные входы накопи" теля подключены к выходам первого дешифратора адреса, соединенного входами с выходами счетчика адреса, вторые адресные входы накопителя подключены к выходам второго дешифратора адреса, соединенного входами с выходами регистра адреса, вход которого соединен с первым выходом буферного регистра, подключенного вторым выходом к входу счетчика адреса и входами к выходам блока связи, кроме того, выходы блока управления соединены с управляющими входами накопителя, счетчика адреса регистра адреса и буферного регистра,,а входы " с выходами блока связи через регистр кода операции и де— шифратор кода операции 2);

982085

15 3

Однако это устройство имеет, во-пер вых, сложный на копит ель в свя зи с пространственной организацией распределения в нем информации, пос-. тупающей на входы первого регистра. слова и выводимой из накопителя на входы второго регистра слова, т.е. каждый элемент памяти помимо функции хранения выполняет и функцию коммутации информации. Сложность накопителя этого устройства подчеркивается

"наличием большого количества связей: двух адресных входов, двух информационных входов и выходов и управляющих входов. Во-Вторых> организация ввода программы коммутации матрицы в накопитель характеризуется также относительно большими затратами оборудования. Необходимы дополнительные аппаратурные затраты (регистр кода операции и дешифратор кода операции для задания режимов работы и для индентифйкации -адресов, вводимых либо в регистр адреса, либо в счетчик адреса. В-третьих, наличие блока свя- 2з зи и второго дешифратора также усложняет устройство.

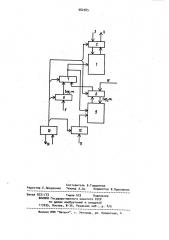

На чертеже изображено устройство.

Устройство содержит постоянный накопитель 1, регистр 2 слова, информационные входы 3 и выходы 4, адресные входы 5, счетчик 6, дешифратор 7, регистр 8 адреса, оперативный накопитель 9, адресные входы

1О и 11, адресный блок 12, блок 13 управления, управляющие входы-выходы 14.

Устройство работает следующим образом.

Устройство выполняет программируемую перестановку m информационных слов, поступающих через информаци- онные входы 3 последовательно по словам параллельным f.-разрядными кодами, Считываемые из накопителя

1 информационной памяти информационные улова на информационных выходах

4 устройства могут быть переставлены . в соответствии с программой (массивом адресов), хранящихся в накопителе 9 управляющей памяти.

Принцип действия устройства в раз. личных режимах работы условно можно, представить следующими схемами.

Цель изобретения - повышение надежности запоминающего устройства.

Пос1авленная цель достигается тем, что запоминающее устройство,содержащее накопитель, информационные входы которого соединены с выходами регистра слова, входы которого являются информационными входами устройства, последовательно соеди,ненные счетчик и дешифратор, входы счетчика являются одними адресными входами устройства, а выходы дешифраторв подключены к адресным входам постоянного накопителя, блок управления, выход. которого соединен с управляющими входами счетчика, регистра слова, регистра адреса и дешифратора, содержит адресный блок и оперативный накопитель, информационные входи и выходы которого подключены к соответствующим выходам и входам регистра адреса, другие выходы которого подключены к входам дешифратора, выходы которого подключены к одним. адресным входам опера-. тивного накопителя, другие адресние входы которого подключены к выходам адресно о блока, входы которого являются адресными входами устройства, в управляющие входы адресного блока соединены с выходом блока управления, Режим записи (ЗП) постоянного накопителя 1 и считывания (СЧ) оперативного накопителя 9 описывается следующим образом.

8 этом режиме по одному и тому же адресу осуществляется запись слова из регистра"2 слова в постоянный накопитель 1 и считывание адреса из оперативного накопителя 9 в регистр 8 адреса.

Режим счйтывания постоянного накопителя 1 и записи (ввод массива адресов через вторые адресные входы 10 устройства) оперативного накопителя 9 можно представить так„ что в первом режиме производится естественная адресация ячеек постоянных накопителей 1 и onepaTcyHoro накопителя 9 с помощью счетчика 6 и дешифратора g, а во втором режиме" принудительная адресация ячеек постоянного накопителя 1 с помощью регистра 8 адреса и дешифратора 7 и ячеек оперативного накопителя 9 с помощью блока 12.

Режимы работы устройства задает блок 13 управления, формирующий различные последовательности сигналов.

Предлагаемое запоминающее устройство является экономичным и быстродействующим, позволяющим соединить

5 9820 любой временной канал уплотненного информационного входа 3 с любым временным каналом уплотненного информационного выхода 4.

Пространственным эквивалентом з устройства является запоминающее устройство (прототип), выполняющее пространственные произвольные соединения между m входами и щ выходами, информация через которые передается последовательными кодами.

Сравнительная оценка устройства.

Сложность накопителя прототипа оценивается сложностью его запоминаю; щей части и сложностью логической

1 части М, выполняющей функцию коммутации. Емкость памяти прототипа и число логических схем И . N=--m .

Кроме того, необходимо иметь в блоке связи, либо во внешней памяти, подключаемой к блоку связи, Vg = = в3оф m 5 и Т памяти для хранения

2 программы коммутации, вводимой в запоминающее устройство (пространственный коммутатор).

При m = Р,относительно одинаковом быстродействии сравниваемых. устройств общая емкость коммутаторного запоминающего устройства .

М=Ч,+М = + COfаФ, но М = 4m. i$

Таким образом, прототип имеет более сложную логическую часть нако-.

1 пителя, дополнительные регистр и.дешифратор кода операций и более сложный блок связи. 46

При Ьш более быстродействующими является предлагаемое устройство, а при в>1 наоборот более высокое .быстродействие имеет прототип. В ре-. .жиме настройки устройств (ввода про- 43 граммы коммутации1 более быстродей85 6 ствующим (с меньшим временем доступа) оказывается предлагаемое устройство благодаря организации непосредственной связи накопителя управляющей памяти с накопителем информационной памяти.

Формула изобретения

Запоминающее устройство, содержащее накопитель, информационные входы которого соединены с выходами регистра слова, входы которого являются информационными входами устройства, последовательно соединенные счетчик и дешифратор, входы счетчика являются одними адресными входами устройства, а выходы дешифратора подключены к адресным входам постоянного накопитея, блок управления, выход которого соединен с управляющими входами счет", чика, регистра слова, регистра адреса и дешифратора, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит адресный блок и оперативный накопитель, информационные входы и выходы которого подключены к соответствующим выходам и входам регистра адреса, другие выходы которого подключены к входам дешифратора, выходы которого подключены к одним адресным входам оперативного накопителя, другие адресные входы которого подключены к выходам адресного блока, входы которого являются адресными входами устройства, а управляющие входы адреоного блока соединены с выходом блока управле:ния.

Источники информации, принятые во внимание при экспертизе I. Àâòñðñêîå свидетельство СССР

Й 410392, кл. G 11 С ll/00, 1977.

2. Авторское с виде тель ство С С CP (11 6112 2, кп. G ll С 11/00, 1978.

Составитель В.Гордонова

Редактор Е.Лазуренко Техред Д.дц Корректор В.Прохненко

Заказ 9721/73 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. Ю/5 .Филиал flAA "Патент", г. Ужгород, ул. Проектная, 4