Оперативное запоминающее устройство на динамических элементах памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Сом(каписткческик

Республик ((ц 982{}89 (6! ) Дополнительное к авт. свид-ву (22) Заявлено 05.03.81 (2! ) 3298733/18-24 с присоединением заявки J% (2З } Приоритет

Опубликовано 15. 12.82 Бюллетень № 46

Дата опубликования описания 15-12 82 (51)М. Кд. 11 С 11/34

Гооударстееииый комитет

СССР

Ro делан изобретений и открытий (5З) ДК681. . 327(088.8) с

В. А. Верстаков, Д. Л. Преснухин и H. О. Kpbmmoa и, (72) Авторы изобретения

Московский институт электронной техники -= --(7l) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНА10ШЕЕ УСТРОЙСТВО

HA ДИНАМИЧЕСКИХ ЭЛЕМЕНТАХ ПАМЯТИ

Изобретение относится к запоминаюшнм устройствам и предназначено для применения в универсальных и специализированных вычислительных устройствах и системах в качестве оперативного запоминающего устройства (ОЗУ).

Известны ОЗУ, используемые в вычислительных устройствах и системах, пост роенные на динамических элементах памяти, которые содержат накопитель, фор30 мирователи управляющих сигналов, а также блоки управления динамической полупроводниковой памятью, представляющие комбинационные схемы, обеспечива!

5 ющие такой режим функционирования памяти, при котором регенерация осуществляется до или после обращения к цамяти, если в определенный момент обращение к памяти не осуществляется, то автоматически выполняется регенера 1)

Недостатками этих устройств saastcmci nw cpu быстродействия памяти за счет

2 невозможности обращения к нему в моменты регенерации.

Наиболее близким техническим реше. нием к изобретению является ОЗУ, состоящее из адресного регистра, первые выходы которого соединены с первым входами первого мультиплексора, вторые входы которого соединены с первыми !

:выходами схемы управления, выходы ко» торого соединены с первыми входами второго мультиплексора, вторые входы которого соединены с вторыми выходами адресного регистра, а выходы второго мультиплексора соединены с первой груп пой адресных шин накопители, третьи выходы адресного регистра через декоди:рующее устройство и схему синхронизьции присоединены к второй группе адрео ных шин накопителя, второй выход схемы управления соединен с управляющим sxo дом первого мультиплексора и первым уп» равляюшим входом декодирук пего устройства, третий выход схемы управления соединен

3 9820 с вторым управляющим входом декодирующего устройства, четвертый и пятый выходы схемы управления через схему синхронизации соединены с управляющи- . ми входами накопителя, выход которого через усилитель считывания подключен к входу регистра считывания, управляющий вход которого соединен с шестым выходом схемы управления. В случаях, когда это запоминающее устройство регенерирует собственное содержимое, при поступлении запроса на обращение в подходящий момент в течение процесса регенерации, осуществляется прерывание этого процесса, и обращение реализуется.

В моменты, когда прерывание процесса регенерапии невозможно выдается сигнал "Занято ° обращение не реализуется, и процесс регенерации продолжается (21.

Недостатками этого ОЗУ являются потеря быстродействия за счет невозможности обращения к памяти в определенные моменты времени, когда прерывание процесса регенерации памяти невозможно, а также необходимость повторного обращения к памяти в этом случае.

Цель изобретения - повышение быстродействия ОЗУ на динамических элементах памяти, которое при обращении к нему запоминало бы заявки на запись, считывание, регенерацию до их выполнения по очереди в порядке поступления.

Поставленная. цель достигается тем, что в оперативное запоминающее устройство на динамических элементах памяти, содержащее регистр адреса, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с первым бл о и 40 вход-- с вторым выходом блока управ ления, а выход подключен к адресному входу накопителя, первый и второй управ ляющие входы которого соединены соответственно с третьим и четВертым выходами 4 блока управления, а информационный вы» ход подключен к входу регистра данных, выход которого является выходом усчройства, à управляющий вход соединен с пяъъ м выходом блока управления, вве 0 .дены три группы последовательно соединенных первого триггера, элемента задержки элемента И и второго триггера, причем выход второго триггера первой грут пы подключен к первому входу блока управления и первым входам элементов И второй и третьей групп, выход- второго трщтера второй группы соединен с вто89 4 рым входом блока управления, первым входом элемента И первой группы и втоым входом элемента И третьей группы, ыход второго триггера третьей группы подключен к третьему входу блока управления и вторым входам элементов И первой и второй групп, управляющие входы триггеров одноименных групп объединены и подключены соответственно к шестому, седьмому и восьмому выходам блока управления, девятый выход которого соединен с информационным входом одного из триггеров первой группы, информационные входы первых триггеров других групп являются входами устройCTHG

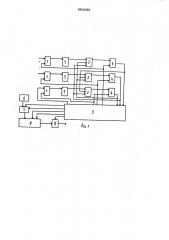

На фиг. 1 изображена структурная схема ОЗУ на динамических элементах памяти; на фиг, 2 — часть схемы на фиг. 1

{раскрыта структура блока управления).

Устройство содержит три группы пооледовательно соединенных первого триггера 1, элемента 2 задержки, элемента И 3, и второго триггера 4, блок 5 управления, регистр 6 адреса, мультиплексор 7, накопитель 8 и регистр 9 данных.

Блок 5 управления (на фиг. 2 выделен пунктирной линией) содержит генератор

10 тактовых импульсов, элемент И-НЕ

11, элементы ИЛИ-НЕ 12-14, усили.тель 15 сигналов, делитель 16 частоты, триггер 17, элемент ИЛИ-НЕ 18, сдвигающий регистр 19, счетчик 20 адреса регенерации, элемент ИЛИ-НЕ 21, усилитель 22 сигналов, элемент ИЛИ-НЕ

23.

Устройство работает следующим образом.

Команды выбора режима, поступающие на входы ОЗУ, устанавливают триггеры 1, служащие для хранения команд выбора

1 режима, в единичное состояние. Перезапись команд из триггеров 1 в соответст вующие триггеры 4, служащие для управления, осуществляется через элементы

2 задержки и элементы И 3.

Единичное состояние одного из триггеров 4 вызывает реализацию соответствующего режима ОЗУ.

Элемент И 3 обеспечивает передачу команды из триггера 1 в соответствующий триггер 4 при условии, что два других триггера 1 находятся в нулевом состоянии, в противном случае выполнение команды, запомненной в триггере 1, задерживается до обнуления триггера 4, происходящего по команде из блока 5 управ5 982 ления по окончании выполнения соответствующего режима. Сброс триггеров 1 происходит по этим же командам из блока 5 управления. Если два или три триггера 1 переклю- g чены в единичное состояние одновременно, то очередность передачи команд триггера 4 и, следовательно, их выполнение осуществляется разными длительностями задержек в эличинтах 2 задержки. 1©

Благодаря введению новых элементов и связей оперативное запоминающее устройство на динамических элементах памяти имеет возможность автоматически поддерживать очередь заявок на запись, считывание, регенерацию с минимизацией времени перехода от реализации одной заявки к реализации другой, что позволяет повысить быстродействие устройства и, кроме того, упростить процедуру обращу ния к памяти центрального процессора.

Технико-экономический эффект от внедрения предлагаемого устройства проявляеъся за счет повышения быстродействия

ОЗУ и выражается в экономии 4% машинного времени.

Формула изобретения

36

Оперативное запоминающее устройство на динамических элементах памяти, содержащее регистр адреса, выход которо го соединен с первым информационным входом мультиплексора, второй информаявьМ онный вход которого соединен с первым выходом блока управления, управляющий вход - с вторым выходом блока управления, а выход подключен к адресному входу накопителя, первый и второй управЮ ляюшие входы которого соединены соответственно с третьим и четвертым вы089 6 ходами блока управления, а информационный выход цодюпочен к вхощ регистра данных, выход которого яилаетса выходом устройства, а управляющий вхаа соеди нен с пятым выходом блока управления, о т л и ч а ю щ е е с s тем, что, с целью повышения быстродействия устройства, в него введены три группы поо, ледовательно соединенных первого триг гера, элемента задержки, элемента И и второго триггера, причем выход второго триггера первой группы подключен к первому входу блока управления и пер вым входам:э лементов И второй и третьей групп„выход второго триггера второй, группы соединен а вторым входом блока управления, первым входом элемента И первой группы и вторым входом элемента И третьей группы, выход вто рого триггера третьей группЫ подключен . к третьему входу бдока управления и, вторым входам элементов И первой и второй групп, управляющив входы триг геров одноименных групп объединены и подключены соответственно к шестому, седьмому и восьмому выходам блока

: управления, девятый выищ которого соединен с информационным входом одного

: из триггеров первой группы, информационные входы первых триггеров дру гик групп являются вкоаами устройства.

Источники информации, принятые во внимание при экспертизе

1. Заявка Японии )4 545939, кл. 97(7) С 19, опублик. 1979.

2.- Заявка Японии Ир 545659, кл. 97(7) С 19, опублик. 1979 (прото тип) б

982О89

Составитень 9. Рудаков

Редактор Е, Лазаренко Техред А.Бакинец Корректор B. Прокненко

Закю 9723.!73 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР но деним изобретений и открытий

113035. Москва, Ж35, Раушскаа наб., д. 4/5

Фи пмш ППП «Патент», г. Ужгород„уп. Проектная, 4