Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

ОП КСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Соээз Советских

Социалистических

Респубики

it ii982100 (61) Дополнительное н авт. свид-ву(22) Заявлено 25. 02. 81(21) 3291499/18" 24 (51)М. Кл. с присоединением заявки ¹

6 11 С 29/ОО

Гоаударстеенный каиьтет

СССР ао делая изобретений и открытий

{23) П риорнтет

Опубликовано 15, 12, 82 ° Бюллетень № 46

Дата опубликования описания 15, 12.82 (@)УДК е81 327 (o88.8) чти

Е, В. Батырев, В.Л. Нуров, В.Н. Павлов, В.ll. Пащенков и В,В.Черенков (72) Авторы изобретения

Московский институт электронной техни (71) Заявитель (g4) УСТРОДСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к запоминающим устройствам, в частности

;: реднаэначено для входного функцио» нального контроля полупроводниковых оперативных запоминающих устройств (ОЗУ) с произвольной выбор» кой.

Известно устройство для контроля памяти, содержащее генератор случайных чисел, построенный на регистре сдвига, который вырабатывает тес. ты на основе линейных и нелинейных случайных кодовых комбинаций 1).

Недостаток данного устройства состоит в низкой достоверности контроля эа счет возможности появле" ния на выходе контролируемого блока памяти неопределенных состояний, no" скольку среди .входных наборов встре-. чаются запрещенные комбинации, а также в невозможности определения статистических характеристик работы контролируемого блока памяти.

Наиболее близким к изобретению является устройство для .контроля блоков памяти, содержащее блок управления, блок памяти, генератор случайных чисеп, блок сравнения, s; контрольный выход которого соединен . с первым входом блока управления $2).

Недостатком этого устройства является необходимость перед контро. лем блока памяти ."аписывать в него конкретный тест, являющийся произ", водным адресной информации, что сни. жает достоверность контроля ввиду невозможности выявить все взаимовлияния элементов, а также случай ных сбоев в блоке памяти на его ра бочей частоте, Кроме того, данное устройство не позволяет определить статистические характеристики рабогю ты контролируемого блока памяти.

Целью изобретения является повы, шение надежности устройства.

Поставленная цель достигается. .тем, что в устройство для контроля

3 982100, 4 памяти, содержащее генератор случайных чисел, схему сравнения, блок индикации и блок управления, первый и второй-"входы которого подключены соответственно к одним из выходов генератора случайных чисел и схемы сравнения, другие выходы которой соединены с одними из входов блока ин" дикации, другой вход которого подключен к первому выходу блока управ.пения, второй вход которого соединен с одним из выходов генератора случайных чисел, введены блок местного управления и статистический анализатор„ управляющие входы которых подключены соответственно к третьему и четвертому выходам блока управления, входы блока местного управления соединены с другими. выходами гене-, ратора случа" íûõ чисел, один из вы.ходов подключен к одному из входов статистического анализатора, выходы которого соединены со .входами схемы сравнения, другие выходы блока местного управления и другой вход статистического анализатора являются соответственно выходами и входом устройства.

Кроме того, блок местного управле ния содержит Формирователь тактовых

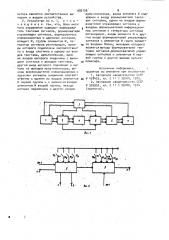

c:игналов, формирователи управляющих сигналов, Формирователи информационных и адресных сигналов, элемент И, группы элементов И, генератор сигналов регенерации, выходы которого подключены соответственно ко входу счетчика и одному из входов триггера, мультиплексор, одни из входов которого соединены с выходами счетчика и выходом триггера, другой вход которого подключен к одному из выходов мультиплексора, выходы формирователей информационных и адресных сигналов соединены соответственно с одними из входов элементов И пер" вой группы и с одними из входов элементов И второй группы, выходы которых подключены к другим входам мультиплексора, выход элемента И подключен ко входу формирователя тактовых сигналов, одним из входов формирователей управляацих.сигналов и входам формирователей информационных сигналов и генератора сигналов регенера ции, входы элемента И и другие входы формирователей управляющих сигналов и элементов И групп являются вхо.. дами блока, выходами которого являются выходы формирователя тактовых сигналов, формирователей управляющих сигналов и элементов И первой. группы и другие выходы мультиплексора, На фиг. 1 представлена структурная схема устройства для контроля памяти; на фиг, 2 и 3 изображены соответственно структурные схемы блока управления и блока местного управления, Устройство для контроля памяти (фиг, 1) содержит генератор 1 случайных чисел, блок 2 местного управления, служащий для формирования временной диаграммы, блок 3 управле1S ния, Блок 4 памяти является контролируемым блоком памяти. Устройство также содержит статистический анализатор 5, схему 6 сравнения и блок 7 индикации.

2р Блок 3 управления (фиг. 2) содержит реле 8 времени, компаратор

9 и переключатели 10 -10

Блок 2 местного управления (фиг,31 содержит формирователи управляющих д сигналов, являющиеся Формирователем 11 сигналов записи-считывания и формирователем 12 сигналов выбора микросхемы, фбрмирователь 13 информа. ционных сигналов, формирователь 14 адресных сигналов, элемент И 1, первую 16 и вторую 17 группы элементов И, генератор 18 сигналов регенерации„ счетчик 19, триггер 20 мультиплексор 21 и формирователь 22 тактовых импульсов.

Устройство работает следующим образом, Блок 3 управления хранит программу контроля полупроводникового ОЗУ, в соответствии с которой вырабатыва" ет сОвокупность управляющих сигналов для генератора 1 случайных чисел, блока 2, статистического анализатора 5 и блока 7 индикации.

hS

При поступлении управляющего сиг- . нала от блока 3 управления генератор ,1 случайных чисел вырабатывает независимые простейаие случайные потоки двоичных сигналов со средним значением m и среднеквадратическим отклонением(3 . Тактовая частота генератора 1 соответствует рабочей частоте контролируемого полупроводникового ОЗУ. Экспоненциальное распределение простейших случайных потоков наиболее близко соответствует характеру распределения информационных потоков в реальных условиях работы ОЗУ, 5. -9821

Далее случайные потоки двоичных: сигналов поступают на блок 2, который по команде с блока 3 управления, в зависимости от типа контролируемого ОЗУ, организует временные задержки по каждому каналу для формирова-.. ния требуемой временной диаграммы контроля. Крома того, блок 2 реализует специальные режимы контроля (например, регенерация для динами- . se ческих ОЗУ) и производит маскирование запрещенных входнь:х наборов, В результате на выходе контролируемо" го ОЗУ (блока 4) отсутствуют неопределенные состояния, И

На входы контролируемого блока

4 памяти подаются независимые простейшие случайные потоки двоичных сигналов, временные соотношения меж-, ду которыми соответствуют требуемой 20 временной диаграмме контроля.

С выхода контролируемого блока

4 памяти случайный поток двоичных сигналов поступает на один вход статистического анализатора 5, на дру- И гой вход которого поступает эталонный простейшйй поток с контрольного выхода блока 2. Статистический аналиЪ затор 5 представляет собой цифровой статистический анализатор характерис- З@ тик случайных процессов, построенный по известной схеме (3 ), который при поступлении управляющих сигналов с блока 3 вычисляет и выдает на схему 6 сравнения среднее."значение и среднеквадратическое отклонение для каждого из .входных случайных потоков, При прохождении простейших случайных потоков через исправное полу" ,проводниковое ОЗУ (блок 4}, пред" ставляющее собой регулярную структу- . ру, характер их распределения и ста-тистические характеристики не меняются, причем для простейших потоков с зкспоненциальным-распределением среднее значение и ореднеквадратическое отклонение равны между собой, т.е.

1 где P " ия енсивность случайного по$0 тока.

В схеме 6 сравнения производится сравнение средних величин обоих случайных потоков, а также сравнение средней величины случайного потока, поступающего с выхода -контрЬли руемого блока 4 памяти с его среднеквадратическим отклонением. Резуль00 б таты- сравнения поступают на блоки 3" и 7, .где отображаются в цифровом виде с помощью семисегментных индикаторов.

В блоке 3 производится сравнение. информации, поступающей со схемы 6 с предварительно заданным ее значением, и, в зависимости от результатов сравнения вырабатываются сигналы Тоден" или "Брак", которые затем отображаются блоком 7 индикации, Таким образом, технико-.зкономическое преимущество предлагаемого устройства заключается, во-пераНх в осуществлении входного контроля блоков памяти в стационарном режимв на их рабочих частотах, во-вторых, в повышении надежности устройства за счет получения дополнительных ста" тистических характеристик блока памяти, что дает возможность повысить достоверность контроля и не только определить работоспособность контролируемого блока памяти, но и оценить его параметрическую. надежность.

Формула изобретения

1. Устройство для контроля памяти, содержащее генератор случайных чисел, схему сравнения, блок индикации и блок управления, первый и второй входы которого подключены соответствено к одним из выходов гене-. ратора случайных чисел и схемы сравнения, другие выходы которой соединены с одними из входов блока инди-, кации, другой вход которого подключен к первому выходу блока управления, второй выход которого соединен с одним из входов генератора случай". ных чисел, о т л и ч а ю щ е е с я те, .что, с целью повышения надеж" ности устройства, в него введены блок местного управления и статистический анализатор, управляющие входы котопых подключены соответственно к третьему и четвертому выходам блока управления, входы блока местного управлеиия соединены с другими выходами генератора случайных чи" сел, один из выходов подключен к одному из входов статистического ана-. лизатора, выходы которого соединены с входами схемы сравнения, другие выхоДы блока местного управления и другой вход статистического анали-.

Источники информации, .

+ принятые во внимание при экспертизе

1. Авторское свидетельство СССР щ hP 428455, кл. G 11 С 29/00 1972.

2, Авторское свидетельство СССР

М 526952, кл. G 11 С 29/00, 1974 (прототип), 98 з атор а я вля ются соот нет ст вен но выходами и входом устройства, 2. Устройство по и. 1, о т л и,ч а ю щ е е с я тем, что, блок мест. нога управления содержит формирователь тактовых сигналов, формирователи управляющих сигналов, формирователь информационных и адресных сигналов, .элемент И, группы элементов И, генератор сигнапов регенерации, выходы, которого подключены соответственно к входу счетчика и..одному из входов триггера, мультиплексор, одни из входов которого. соединены с выходами счетчика и выходом триггера, другой вход которого подключен к одному из выходов мультиплексора, выходы формирователей информационных .и адресных сигналов соединены соответственно с одними из входов элементов

И первой группы и с одними из входов элементов И второй группы, выходы которых подключены к другим входам

2100 8 мультиплексора, выход элемента И подключен к входу формирователя тактовых сигналов, одним из входов формирователей управляющих сигналов и

3 входами Формирователей информационных сигналов и генератора сигналов регенерации, входы элемента И и другие входы Формирователей управляоцих сигналов и элементов И групп являют/ ся входами блока, выходами которого являются выходы Формирователей тактовых сигналов, формирователей управляющих сигналов и элементов И первой группы и другие выходы мульти> плексора.

982!00 акаэ 9 ираж 2 одлисное

ВНИИПЙ Государственного комитета СССР по делам изобретений и открытий

ll 3035, Москва, N-35, Рауаская наб., д. 4/5

Филиал, атент, г. жгород, ул, роектная, Составитель В,Рудаков

Редактор С,Тимохина Техред Т.Фанта Корректор Н,Король