Интегрирующий аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советски к

Социапистичесиик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Н 03 K 13/20

Гееударстеенный комитет

СССР пв делам изобретений и открытий (53) УДК 681 ° 325 (088.8) Опубликовано 15. 12. 82. Бюллетень № ч6

Дата опубликования описания 15.12.82

A. П-. - Ксяопкям;- ==-, А. И:;-,Хорса а, 1

И. М. Вишенчук, Н. Г. Гитшов, О. О. Каганов,:

P. В. Курдыдык, В.Ф. Ткаченко и (72) Авторы изобретения

1

1 t

Львовский ордена Ленина политехнически им. Ленинского комсомола

2 -. и нст иту t(71) Заявитель (54 ) ИНТЕГРИРУЮЦИЙ АНАЛОГО-ЦИФРОВОЙ

ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к цифровой злектроизмерительной технике.

Известны интегрирующие АЦП с двухтактным интегрированием, осуществляющие аналого-цифровое преобразование разнополярных напряжений с одним источником опорного напряжения и с запоминающей обратной связью для компенсации дрейфа усилителей устройства. Особенностью известных АЦП является запоминание на конденсаторах запоминающей обратной связи не только корректирующей поправки, но и всего опорного напряжения (или его части, соответствующей пределу измерения ), которое в интервале двух тактов аналого-цифрового преобразования должно оставаться неизменным, так как erq нестабильность вйзывает нелинейную составляющую погрешности преобраэова-щ ния.

Известны интегрирующие аналого-цифровые преобразователи, в которых используется один источник опорного на2 пряжения, два запоминающих конденсатора, на одном иэ которых запоминается напряжение, компенсирующее дрейф усилителей устройства, а на другомI напряжение 0о, близкое по абсолютному значению и обратное по полярности опорному напряжению, и результирующее напряжение дрейфа l1).

Недостатком этих АЦП является большая погрешность, возникающая вследст" вие разряда запоминающего конденсатора через сопротивление изоляции между выводами конденсатора. Кроме того, в этих АЦП требуется дополнительное время для заряда второго sàïîìèíàþùåãî конденсатора, что снижает быстродействие АЦП. 8 иих интегратор используется в биполярном режиме, которому свойственна нечувствительность в 3оне нуля, вызываемая неопределенностью выходного напряжения нуль-органа, запаздыванием интегратора, нуль-органа и ключей, для устранения которой требуется дополнительное оборудование.

3 98219

Наиболее близким к предлагаемому является аналого-цифровой преобразователь, содержащий коммутатор, первые входы которого соединены соответственно с входной шиной, с выходом источни-> ка опорного напряжения и с выходом делителя спорного напряжения, а вторые входы — с входом интегратора, выпол- фиг. 2 " временные диаграммы работы ненного на операционном усилителе с конденсатором в цепи обратной связи, 1О выход интегратора соединен с входом усилителя-компаратора, выход которого через ключ соединен с первым выводом запоминающего конденсатора (2 3.

Недостатком известного АЦП являет- 1 ся большая погрешность, возникающая вследствие разряда запоминающего конденсатора через сопротивление изоляции между выводами конденсатора, особенно ощутимая в широком диапазоне 2о воздействия дестабилизирующих Факторов. Кроме того, устройство содержит сложный узел - дифференциальный усилитель, предназначенный для выделения с высокой точностью разности между 25 вспомогательным и опорным или между вспомогательным и входным напряжения" ми, что усложняет схему.

Цель изобретения - повышение точности преобразования разнополярных зо напряжений с применением одного источника опорного напряжения и упрощения схемы.

2 4 дополнительный резистор соединен с инвертирующим входом усилителя интегратора, неинвертирующий вход которого соединен с выходом делителя опорного напряжения.

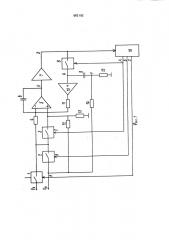

На фиг. 1 представлена структурная электрическая схема устройства; на (Фиг. 2, б ) ключ 1 замыкается, остальные ключи 2, 3 и 8 разомкнуты. Поскольку неинвертирующий вход операционного усилителя 5 находится под напряжением 0 „,, снимаемом с делителя, образованного резисторами 12 и 13, происходит интегрирование разности входного напряжения Ux и напряжения

Uo (Фиг. 2 е ). После окончания интервала Т1 сигналом устройства 16 (фиг. 2 б) ключ 1 размыкается, а ключ

2 замыкается (Фиг. 2 в), подключая к входу интегратора опорное напряжение

Uo, ключи 3 и 8 разомкнуты. Происходит в течение интервала Т2 интегрирование разности напряжений Qо и Uo при котором напряжение на выходе интегратора стремится к нулю (фиг. 2 е ), при достижении которого срабатывает усилитель-компаратор 7. Интервал Т2 длится от окончания интервала интегрирования до срабатывания компаратора. В интервале Т3 сигналами устройства 16 ключ 2 размыкается (фиг. 2 в ) а ключи 3 и 8 замыкаются (фиг, 2 г), ключ 1 разомкнут. В таком состоянии устройство находится в течение интервала Т3 от момента срабатывания нульоргана до начала следующего цикла измерения. На конденсаторе 9 происходит запоминание напряжения дрейфа усилиДля этого в интегрирующий аналогоцифровой преобразователь, содержащий коммутатор, первые входы которого соединены соответственно с входной шиной, с выходом делителя опорного напряжения, и с выходом делителя опорного напряжения, а вторые входы с вхо40 дом интегратора, выполненного на операционном усилителе с конденсатором в цепи обратной связи, выход интегратора соединен с входом усилителя-компаратора, выход которого через ключ соединен с первым выводом запоминающего конденсатора, введены дополнительный делитель с коэффициентом де" ления, равным коэффициенту деления делителя опорного напряжения, повторитель и дополнительный резистор, причем дополнительный делитель включен

I между выходом источника опорного напряжения и общей шиной, выход дополнительного делителя подключен к второму выводу запоминающего конденсатора, первый вывод. которого подключен к входу повторителя, выход которого через устройства

Устройство содержит коммутатор, состоящий из ключей 1, 2 и 3, резистор

4, операционный усилитель 5 и конденсатор 6, образующие интегратор, усилитель-компаратор 7, ключ 8, запоминающий конденсатор 9, повторитель 10, дополнительный резистор ll, резисторы

12 и 13, образующие делитель опорного напряжения, резисторы 14 и 1$ образующие дополнительный делитель, устройство управления 16.

Работает аналого-цифровой преобразователь следующим образом.

Цикл работы преобразователя Фиксированный, состоит (фиг. 2 ) из интервалов интегрирования Tl, преобразования Т2 и коррекции Т3. 8 течение фиксированного интервала интегрирования

Т1 сигналом устройства управления 16

Формула изобретения.

5 98219 телей 5, 7 и 10 и разности напряжений

U „„ и напряжения в точке F. Напряжеwe в точке G близко к U . Длительность интервала Т2 однозначно определяет величину и полярность измеряемо- ® го напряжения.

Выходное напряжение интегратора в интервале Tl равно

u -u -т

0 (х см) 1 в„с„ 30 в интервале Т2

U (Up uCh4 ) Т я„с„ где R„C„- интегрирующие резистор и конденсатор (резистор 4 и конденсатор 6 ).

Так как Оп„+Оn — — О

Т— (Uce )х ). Ta ()о см

При U 0 получаем 20

Т2 (О )=Т1 (при К- U — 2 )

"см

Т2(О)=1/2Т1 (при K=3)

Включение эквивалентного сопротивления дополнительного делителя после- 2g довательно с запоминающим конденсатором практически исключает его влияние на устойчивость схемы при эамыкации обратной связи.

Интегрирующий аналого-цифровой пре- образователь, содержащий коммутатор, первые входы которого соединены соответственно с входной шиной, с выходом

2 б источника опорного напряжения и с выходом делителя опорного напряжения, а вторые входы - с входом интегратора, выполненного на операционном усилителе с конденсатором в цепи обратной связи, выход интегратора соединен с входом усилителя-компаратора, выход которого через ключ соединен с первым выводом запоминающего конденсатора, отличающийся .тем, что, с целью повышения точности преобразоваHNR раэнополярных напряжений с применением одного источника опорного напряжения и упрощения схемы, введены дополнительный делитель с коэффициентом деления, равным коэффициенту деления делителя опорного напряжения, повторитель и дополнительный резистор, причем дополнительный делитель включен между выходом источника опорного напряжения и общей шиной, выход допол нительного делителя подключен к второму выводу запоминающего конденсатора, первый вывод которого подключен к входу повторителя, выход которого че" рез дополнительный резистор соединен с инвертирующим входом операционного усилителя интегратора, неинвертирую" щий вход которого соединен с выходом делителя опорного напряжения.

Источники информации, принятые во внимание при экспертизе

Патент США И 4034364, кл. 340347, 1977.

2. Патент Англии N 1390064, кл. G 4 Н, 3975 (прототип).

982 1 92

Заказ 9733/78

Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, Составитель В. Иахнанов

Редактор К. Волощук ТехредЛ,Пекарь Корректор И. Шаооши