Сумматор в коде "м" из "n

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< >983706

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свнд ву(22) Заявлено 17.07.81 (2) ) 3315868/18 24 (53)M. Кл.

QO65 7/49 с присоединением заявки №(23) П риори.тет— ееударетиввых веюхтет

CCCP аю делен нзебретеввй и атерытвй (53 ) УД К 681. 325 (088.8) Опуб,хиновано 23.12.82. Бюллетень № 47

Дата опубликования описания 23.12.82 ф

f,: (72) . Автор изобретения

В. А. Гуменюх

Киевский ордена Трудового Красного Знамени институт инженеров гражданской авиации (7I) Заявитель (54) СУММАТОР В КОДЕ "М ИЗ Й "

Изобретение относится к вычислительной технике и предназначено для сумми-рования чисел, представленных в коде

"М изМ ".

Известен двухразрядный сумматор в . коде "M из H младший разряд которого содеркит блок выдачи результата, шифратор, матрицу элементов И, блок. переноса и блок контроля, старший разряд содержит1. о два блоха выдачи результата, два шифратора, матрицу элементов И, блох переноса и блок контроля, причем выходы матрицы младшего разряда соединены с входа ми блока переноса и шифратора младшего 1 разряда, выходы матрицы старшего разряда соединены с входами блока переноса и обоих шифраторов старшего. разряда, выходы шифратора и блока контроля младшего разряда соединены с входами блока 20 выдачи.младшего разряда, выходы блока.

: переноса младшего разряда и обоих шифраторов старшего разряда соединены с входами соответствуюших блоков выдачи

2 ,старшего разряда, выходы блока контроля старшего разряда соединены с входами блоков выдачи старшего разряда,. выходы блоков выдачи младшего и старшего разрядов и .блока переноса старшего разряда соединены с соответствуюшими шинами устройства Р 1) .

Недостатками этого устройства являются сравнительно невысокое быстродействие из-еа необходимости прохождении сигналов, соответствующих результату выполненной операции, через блоки выдачи результата, и большие аппаратурные затраты на реализашпо блоков контроля и выдачи результата.

Наиболее близким к изобретению является сумматор в коде "М изб, кото рый содеркит регистр результата, шифратор, матрицу сложения и блок переноса, причем входы матрицы сложения соедине ны соответственно с входами шифратора и блока переноса, выходы регистра результата соединены с выходными шинами сумматора, первая группа входов регистра

3 98370 результата соединена с входной шиной установки сумматора, выходы шифратора соединены с второй группой входов регистра результата t 2) .

Недостатком этого устройства является сравнительно невысокое быстродействие вследствие необходимости прохождения входных сигналов до формирования результата на выходах устройства последовательно через три блока: матрицу сло- 30 .;жения, шифратор и регистр результата.

Бель изобретения - повышение быстродействия сумматора в коде "М из Я ".

Поставленная цель достигается тем, что в сумматоре в коде "М из и ", 15 содеркашем матрицу сложения и регистр результата, причем первый и второй входы

1 матрицы сложения соединены соответственно с входными шинами перврго и второго операндов сумматора, первая группа вхо- щ дов регистра результата соединена с входной шиной установки регистра результата, .а выходы регистра результата соединены с первой группой выходных шин сумматора,; первая и вторая группы выходов матрицы i сложения соединены с второй группой входов регистра результата и второй груп- пой выходных шин сумматора соответст» венно, причем матрица сложения состоит из многовходовых элементов И, имеюших 30 по Я«М+1 идентичных, но гальванически независимых выходов, 4 -е (1 1<М-М) ,выходы элементов И матрицы сложения, которые соответствуют одинаковым разрядам кодовых слов результатов, содержашим нули, соединены с соответствуюши. ми 1-ми выходами первой группы выходов матрицы сложения, Н-М+1 - е выходы элементов И матрицы сложения, которые соответствуют одинаковым переносам в старший разряд, соединены с соответствующими, выходами второй группы выходов матрицы сложения.

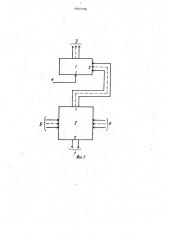

На фиг. 1. представлена блок-схема сумматора в коде "М иэ К "; на фиг. 2 - 45 матрица сложения при использовании кода

2 иэ 4", основании системы счисления рФ4 си следуюшем алфавите: 0-0011, 1-0101; 2-1010; 3-1100, где 0-я по, зиция кодового слова — крайняя справа.

Устройство содеркит регистр 1 результата, матрицу 2 сложения.

Группа выходов блока 1 соединена с первой группой выходных.шин 3 устройства, первый вход блока 1 соединен с вход55 ной шиной 4 установки регистра результата, первая группа выходов блока 2 соединена с второй группой входов блока 1, 6 4 первая и вторая г руппы входов блока 2 соединены с группами входных шин 5 и

6 устройства, вторая группа выходов блока 2 соединена с выходными шинами 7 устройства..

Блок 1 устройства представляет собой регистр из N триггеров, единичные входы которых образуют первую группу входов блока, а нулевые - вторую группу входов блоха. Единичные выходы триггеров о6раэуют группу выходов блока.

Блок 2 устройства представляет собой матрицу многовходовых элементов И. Количество входов элемента И равно 2М.

Входы элементов И матрицы 2 соединены с определенными шинами ходов операндов, согласно выбранному алфавиту. Шины кодов операндов соединены с входами матрицы 2. Каждый элемент И имеет по hl-М+1 идентичных, но гальванически независимых выходов. Такой элемент может представлять, например, группу из К-М+

+1 многоэмиттерных транзисторов по

2М эмиттеров в каждом.

4-е выходы элементов И матрицы 2 (1 1 < Й -М), которые соответствуют одинаковым позициям кодовых слов результатов, содержашим "единицы", соединены шинами с соответствуюшими -ми выходами первой группы выходов матрицы 2, образуя при этом так называемый

"проводной шифратор" в коде, обратном коду "М из И ", hl-М+1 -е выходы элементов И матрицы сложения, которые соответствуют одинаковым переносам в старший разряд, соединены с соответствуюшими выходами (ПО,П1) второй группы выходов матрицы сложения.

Устройство работает следуюшим обра-, зом.

Операнды в коде М из N " поступают на входы матрицы 2 сложения. Если поступают правильные слова, срабатывает один из элементов И и с его выходов сигналы, соответствуюшие результату операции, поступают на g-М выходов первой группы выходов таким образом, что на них образуется кодовое слово результата в ходе, обратном коду "М из Й ", и на соответствуюший выход переноса второй группы выходов. С выходов первой группы выхоцов матриц 2 сложения сигналы поступают на соответствуюшие входы второй группы входов регистра 1 результата, на нулевые входы триггеров, предварительно установленных в единичное состояние. Сигналы с выходов второй группы

5 083 выходов матрицы -2 сложения поступают в выходную шину устройства. На выходах регистра 1 результата образуется кодовое слово, соответствуюшее результату операции в коде "М из Й 5

Появление ошибочных кодовых слов операндов с меньшим, чем положено, количеством " единип", приводит к отсутствию сигналов на всех выходах матрицы 2 сло. жения. Появление ошибочных кодовых слов о операндов с большим, чем положено, коли-

1 чеством единиц", приводит к появлению на выходах матрицы 2, кроме истинных, также некоторого количества лишних сиг налов, которые . шифруются проводным

» 35 шифратором" как. результаты несхольких правильных операций, появившихся одновременно, в коде, обратном (по уровням напряжений) коду "М из H . Вследствие этого на выходах регистра 1 результата . о образуется кодовое слово с меньшим, чем положено, количеством единиц, так как большее, чем нужно количество триггеров (установленных ранее в единичное состояние), переводится в нулевое состоя-

5 ние. Такое слово не может быть дешифровано как правильное и, следовательно, ошибка не,получает дальнейшего распро: странения.

Рассмотрим работу матрицы 2 сложе- ЗО ния (фиг. 2) на конкретном примере. Как было отмечено, "проводной шифратор", входяший в состав матрицы 2 сложения и не вносяший дополнительной задержки, шифрует результат сложения в коде, обратном коду "2 из 4, при следуюшем алфавите:

0-0011; 1-0101; 2-1010; 3-1100.

Каждый элемент И матрицы в этом случае имеет по четыре входа и по три идентичных,но гальванически независимых 4 выхода, причем два из последних соединены с соответствуюшими выходами первой группы выходов блока 2, а третий - с соответствуюшим выходом второй группы выходов блока 2. При сложении, например45 чисел 1 и 2 сигналы, представляюшие их, поступают на все входы (Ha Фиг. 2входы не показаны) элементов И. С выходов сработавшего элемцнта сигналы поступают на выходы 0-я позиция результата" и 5о 1-я. позиция результата» первой l руппы выходов блока 2 и на выход Перенос нуля

{ ПО) второй группы выходов блока 2.

После воздействия упомянутых сигналов с выходов первой группы выходов блока

2 на нулевые входы соответствуюших трит

706 6 геров:блока 1 (предварительно установ ленных в единичное состояние), на выходах последнего образуется кодовое слово

- результата сложения 1100, что соответ ствует цифре 3.

Положительный эффект от внедрения устройства заключается в увеличении быстродействия, так как в данном устройстве сигналы до получения результата сложения проходят через два блока, а в известием устройстве - через три блока.

Формула изобретения

Сумматор в коде «М из М», содержа» ший матрицу сложения и регистр результата, причем первый и второй входы матрицы сложения соединены соответственно с входными шинами, первОго и второго операндов сумматора, первая группа входов регистра результата соединена с, входной шиной установки регистра результата, а выходы регистра результата соединены с первой группой выходных шин сумматора, о т л. и ч а ю ш и и с я тем, что, с целью повышения быстродействия, первая и вторая группы выходов матрицы сложения соединены с второй группой входов регистра результата и второй группой выходных шин сумматора соответственно, причем матрица сложения состоит из многовходовых элементов И, имеющих по

Я-М+1 идентичных, но гальванически независимых выходов, q -е (1 1 » »М -М) выходы элементов И матрицы cJIQKBHHH, которые соответствуют одинаковым разрядам кодовых слов .результатов, содержашим "нули, соединены с соответствующими 1 -ми выходами первой группы выходов матрицы сложения, t4-М+1 -е, вы« ходы элементов . И матрицы сложения, которые соответствуют одинаковым переносам в старший разряд, соединены с сеответствуюшими выходами второй группы выходов матрицы сложения.. Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

% 798828,. кл. 606F 7/50, 1981.

2. Авторское свидетельство СССР по заявке ¹ 2838935/18 -24, клЛОВГ 7/50, 1980 (прототип).

983706

Составитель Н. Захаревич

Редактор А. Шишкина Техред А. Бабинец Корректор E. Рошко

Заказ 9924/58 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушскаи наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4