Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик (io 983757

:ф

- I г

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22}.Заявлено 02. 07. 81 (23) 3310247/18-24 с присоединением заявки N9— (23) Приоритет—

Опубликовано 231282. бюллетень Ко 47

Дата опубликования описания 23.12.82

Р М g+ з

С 11 С 29/00

Государственный комитет

С.СС P по делам изобретений и открытий (53) УДК 6 81. 327 (088. 8) В. П. Дудалев, Л. A. Колосков и С. A. Ше еко:;., " - ф

4 : ми щ т:@ т .: -: :.!, а ., g

У (72) Авторы изобретения (71 j Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к эапотлинающим устройствам;

Известно устройство для контроля памяти, содержащее два счетчика, накопитель, блок управления и выходной . регистр (11.

Недостатком этого устройства является то, что он не обеспечивает контроль выбранных разрядов информа.ции при записи.

Наиболее близким по технической сущности к изобретению является устройство для контроля памяти, содержащее запоминающие ячейки (накопитель), входы каждой йз которых подключены через элементы И к информационным шинам, первый дешифратор, выходы которого подключены к вторым входам соответствующих элементов И,. а вхо. ды соединены с выходами первого счетчика, подключенного через второй счетчик к генератору тактовых импульсов, и выходной регистр, Входы которого соединены с выходами коммутатора, а вход сброса подключен к первому выходу первого дешифратора Р 2).

Недостатками этого устройства являются низкое быстродействие, так как для контроля информации при записи в любую запоминающую ячейку по любым заранее заданным разрядам необходимо обращаться к выбранной ячейке столько раз, сколько задано раз5 рядов в данной ячейке и низкая надежность, так как оно обеспечивает контроль каждого. разряда только для неисправных запоминающих ячеек.

Целью изобретения является повышение быстродействия устройства. . Поставленная цель достигается тем, что в устройство для контроля памяти, содержащее элементы памяти, входы которых подключены к выходам элементов И, первый дешифратор, счетчики, генератор тактовых импульсов, первый коммутатор и вйходной регистр, информационные входы которого соединены с выходами первого коммутатора, а вход сброса подключен к одному иэ, выходов первого дешифратора, другие выходы которого соединены с первыми входами элементов И, а входы — с вы« ходами первого счетчика, вход которого подключен к одному из выходов второго счетчика, вход которого соединен с выходом генератора тактовыХ импульсов, вторые входы элементов И соответственно объединены и являются информационными входами устройства, 30 введены мультиплексор, второй дешиф983757 ратор, шифраторы, второй и третий коммутаторы, причем входы второго ! дешифратора соединены с выходами вто" рого счетчика, а выходы — с одними из входов второго и третьего коммутаторов, другие входи которых подклю- 5 ! ,чены к другим выходам первого дешиф.Ратора, вхожая первого и второго шиф4 раторов соединены соответственно с . выходами второго и третьего коммутаторов, выходы первого и второго шиФ- 1р раторов подключены к управляющим входам мультиплексора и первого коммутатора соответственно, выход мультиплексора соединен с входом первого коммутатора, а информационные входы подключены к вторым входам соответствующих элементов И.

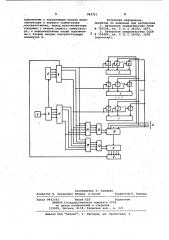

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит элементы 1 памяти, элементы И 2, информационные входы 3, первый дешифратор 4, первый

5 и второй б счетчики, генератор 7 тактовых импульсов, выходной регистр

8, первый .коммутатор 9, мультиплексор 10, второй дешифратор 11, первый

12 и второй 13 шифраторы, второй 14 и третий 15 коммутаторы, выполненные программируемыми. Второй коммутатор 14 может быть выполнен, напри- 30 мер,, в виде наборного поля, Устройство работает следующим образом.

Входная информация со входов 3 синхронно, с частотой, определяемой 35 генератором 1 и счетчиком б, поступает через элементы И 2 в элементы 1 " памяти. Счетчик 5 и дешифратор 4 обеспечивают последовательное;заполнение всех элементов 1 памяти. Считы-40 вание каждого бита информации, поступающей в заданный разряд каждого заранее заданного элемента 1 памяти, производится с помощью регистра 8.

При этом номеР разряда, котоРый сле- 4 дует считывать из элементов 1 памяти, устанавливается с помощью программируемого коммутатора 14. Импульсы с выходом дешифраторов 11 или 4, открывая для записи выбранный элемент

1 памяти, проходят в соответствии с заранее установленной программой через коммутатор 14 на вход шифратора 12, выходной импульс которого настраивает мультиплексор 10 на передачу информации заданного разряда.

Эта информация с выхода мультиплексора 10 поступает на вход коммутатора 9, который направляет ее в требуемый разряд регистра 8, предварительно обнуленного импульсом с выхода дешифратора 4, соответствующего нулевому состоянию .счетчика 5. Второй коммутатор 15 по заданной программе переключает выходы дешифраторов 11 или 4 на соответствующий вход шифра- 65 тора 13, выходной импульс которого управляет коммутатором 9. Таким образом, информация, соответствующая выбранному разряду для каждого элемента 1 памяти, записывается в заданный разряд регистра 8. Выбор номера выхода дешифраторов 4 и 11 обеспечиваетая настройкой коммутаторов 14 и 15 и определяет состав информации в регистре 8. При этом дешифратор 11 обеспечивает запись выбранных разрядов одного какого-либо элемента 1 памяти, а дешифратор 4 обеспечивает конкретный выбор этого запоминающего элемента 1 памяти.

В итоге контроль записываемой информации независимо от числа контролируемых разрядов каждого элемента 1 памяти обеспечивается без потерь времени.

Таким образом, повышается быстродействие устройства путем сокрац1ения времени на контроль записываемой информации.

Технико-экономическое преимущество предлагаемого устройства заключается в его более високом, по сравнению с известным быстродействии..

Формула изобретения

Устройство для контроля памяти, содержащее элементы памяти, входы которых подключены к выходам элементов И, первый дешифратор, счетчики, генератор тактовых импульсов,.первый коммутатор и выходной регистр, информационные входи которого соединены с выходами первого коммутатора, а вход сброса подключен к одному из выходов первого дешифратора, другие выходи которого соединены с первыми входами элемеитов И, а входы — с выходами первого счетчика, вход которого подключен к одному из выходов второго счетчика, вход которого соединен с выходом генератора тактовых импульсов, вторые входы элементов И соответственно объединены и являются информационными входами устройства, о т л и ч а ю ц е е с я тем, что, с целью повышения быстродействия устройства, в него введены мультиплексор, второй дешифратор, шифраторы, второй и третий коммутаторы, причем входы второго дешифратора соединены с выходами второго счетчика,. а выходы — c одними из входов второго и третьего коммуторов, другие входы. которых подключены к другим виходам первого дешифратора, входы первого и второго шифраторов соединены соответственно с выходами второго и третьего коммутаторов, выходи первого и второго шифраторов

983757

Составитель Т. Зайцева

Редактор Н. Лазаренко Техред З.Палий Корре ктор Л. Бокка н

Заказ 9933/б1 Тираж б22 Подписное

ВИНИШКИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 подключены к управляющим входам мультиплексора и первого коммутатора соответственно, выход мультиплексора соединен с входом первого коммутатора, а информационные входы подключены к вторым входам соответствующих элементов И.

6 .Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 705526, кл. С 11 С 29/00, 1977.

2. Авторское свидетельство СССР

9 754485, кл. G 11 С 29/00, 1978 .(прототип).