Устройство для синхронизации генераторов переменного тока

Иллюстрации

Показать всеРеферат

Союз Советскик .

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ о1983892 (61) Дополнительное к авт. саид-ву— (22) Заявлено 261180 (21) 3009018/24-07 f51) bA. Ktl.З с присоединением заявки ¹â€”

Н 02 J 3/42

Государственный комитет

СCCP по делам изобретений и открытий (23) Приоритет— (ЩУДК 621.316..729 088.8) Опубликовано 231282 Бюллетень ¹47 .Дата опубликования описания 23.1282

Л.З.Рудерман, Т.Н.Бобылева, И.С.Пузыревичф В;Н-.-Константинов, Л.Ш.Майзель и М.Б.Вандер1 (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ГЕНЕРАТОРОВ

ПЕРЕМЕННОГО TOKA

Изобретение относится к синхрони.зации синхронных генераторов и может быть использовано в частности, в системах автоматизированного управления судовыми электроэнергетическими установками для выполнения режимов включения на параллельную работу судовых синхронных генераторов.

Известны устройства для включения на параллельную работу с постоянным углом опережения момента включения, формирование сигнала в которых осуществляется в результате выделения огибающей напряжения биения путем его выпрямления и последующей фильтрации 1).

Недостатком известных устройств является большая ошибка измерения фаз, вносимая искажениями огибающей напряжения биения при искажениях слагающих его напряжений.

Наиболее близким по технической сущности к изобретению является устройство для синхронизации генератоpos переменного тока, содержащее формирователи импульсов с выходами для подключения на напряжения синхронных генераторов, причем выходы формирователей подключены к блоку логики, счетчик импульсов со счетным вхо дом, под ключ е н ным к выходам дв ухвходовой схемы совпадения, первый вход которой подключен к блоку логи ки, а второй вход — к генератору высокочастотных импульсов, дешифратор с входами, подключенными к соответствующим разрядам счетчика импуль. сов, блоки запре — à по разности частот и разности напряжений и формирователь выходного импульсаf2 3.

В этом устройстве определение момента включения должно обязательно начинаться при значениях угла опережения в 2-3 раза больших допустимого, что обусловлено необходимостью реализации алгоритма постоянного угла опережения и запрета по разности частот. В результате при включении устройства в работу в зоне допустимых .для включения углов сдвига фаз (разности фаз) в ряде случаев возможен пропуск целого периода напряжения биения прежде чем будет выдана команда на включение, что затягивает процесс синхронизации на несколько секунд.

Целью изобретения является повышение быстродействия устройства синхронизации.

983892

Эта цель достигается тем, что устройство для синхронизации генераторов переменного..тока, содержащее формирователи импульсов с выхОдами для подключения на напряжения генераторов, причем выходы формирователей подключены к блоку логики, счетчик импульсов со счетным входом, подключенным к выходу двухвходовой схемы совпадения, первый вход которой подключен к блоку логики, а второй вход - к генератору высокочастотных импульсов, дешифратор с входами, подключенными к соответствующим разрядам счетчика имнульсов„ блоки запрета по разности частот и разности на1 пряжений и формирователь выходного импульса, снабжено схемой определения начала измерения угла включения, содержащей два статических триггера, первые входы которых объединены и 20 подключены к выходу переполнения счетчика импульсов, первый элемент задержки, выход которого подключен к входу второго элемента задержки и к установленному входу счетчика 25 импульсов, выход второго элемента задержки подключен к второму входу второго статического триггера, схемой установки нуля, выход которой подключен к второму входу первого ста- ЗО тического триггера и второму входу дополнительно введенной схемы ИЛИ, первый вход которой подключен к выходу дополнительно введенного инвертора со входом, подключенным к выходу блока логики, н выход схемы ИЛИ под" ключен к входу первого элемента за-.. держки, выходной схемой совпадения, входы которой подключены к. выходам блоков запрета по разности частот и напряжений, дешифратора„ статичес- 4О ких триггеров; инвертора, а выходк входу формирователя выходного импульса.

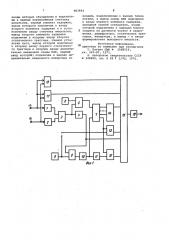

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 временные диаграммы, поясняющие работу устройства.

Устройство cocToèò из формирователей 1 и 2 импульсов, к входам которых подключены напряжения синхронизируемых генераторов U и 0, а их выходы подключены к соответствующим входам блока З.логики, выход которого подключен к входу инвертора 4 и ко второму входу схемы 5 совпадения„

55 первый вход которой подключен к выходу генератора б высокочастотных.импульсов. Выход схемы .5 совпадения подключен к счетному входу двоичного счетчика 7, а выход инвертора 4 @ подключен к первому входу схемы

ИЛИ 8, второй вход которой подключен к выходу схемы 9 установки нуля. Выход схемы ИЛИ 8 через первый элемент задержки 10-подключен к установоч- 45 ному входу счетчика 7 и одновременно к входу второго элемента задержки 11, выход которого подключен к второму входу триггера 12 текущего переполнейия, первый вход которого объединен с первым входом триггера 13 начального переполнения и подключен к выходу переполнения счетчика 7. Второй вход триггера 13 подключен к выходу схемы 9 нулевой установки. Выходы -разрядов счетчика 7 подключены к дешифратору 14, выход которого подключен к третьему входу схемы 15 совпадения, четвертый вход которой подключен к выходу инвертора 4, пятый вход — к прямому выходу .триггера 13, шестой вход — к инверсному выходу триггера 12, первый вход — к выходу блока запрета по разности напряжений 1б, а второй вход— к выходу блока запрета по разности частот 17. Выход схемы 15 совпадения подключен к формирователю 18 выходного импульса.

Устройство работает следующим образом.

При включении питания узел 9 установки нуля вырабатывает короткий импульс, устанавливающий счетчик 7 и триггеры 12 и 13 в положение "0".

При этом сигнал на выходе выходной схемы 15 совпадения отсутствует, так как íà ее пятом входе, соединенном с прямым выходом триггера 13,, имеет место логический "0". Синусоидальные напряжения работающего и подключаемого генератора поступают соответственно на входы формирователей 1 и 2 и на входы схем запрета по разности напряжений 1б и разности частот 17, На выходах формирователей .

1 -и 2 имеют место последовательности импульсов, которые условно можно обозначить а и Ь, периоды. повторения которых равны периодам входных напряжений, а длительности — их полупериодам. На выходе блока 3 логики имеет место исходная последовательность импульсов, описываемая логичес ким уравнением :Q «» «а Ъ ч QQ, длительностЬ каждого из которых соответствует углу сдвига фаз между на- . пряжениями. При этом, максимальная длительность импульса указанной последовательности имеет место, когда входные напряжения находятся в противофазе. Затем с уменьшением угла сдвига фаз длительность импульсов уменьшается. С возникновением очередного импульса на выходе блока 3 логики через схему 5 совпадения на вход счетчика 7 начинают поступать высокочастотные импульсы генератора 6, т.е. начинается измерение длительности импульса (угла сдвига фаз ). Одновременно на выходе инвертора 4 возникает

983892 логический "0", обеспечивающий отсутствие выходного сигнала на время .измерения.

Р

С окончанием импульса на счетчике 7 оказывается записанным число, соответствующее его длительности.

С помощью дешифратора 14 определяется соответствие этого числа заданной уставке. Если угол сдвига фаз находится в допустимых для включения пределах, то на выходе дешифра- 10 тора 14 образуется логическая "1", в противном случае — логический "0".

Триггеры 12 и 13 служат для защиты от.ложных. выходных сигналов. Емкость счетчика 7 несколько превышает максимально допустимое число, соответствующее норме. Длительность измеряемых импульсов,разности фаз и заполняющая частота высокочастотных импульсов таковы, что исключая неболь- QQ шой. интервал в окрестности точки сов адения фаз, счетчик 7 переполняется. Поскольку включение синхронизатора производится в произвольный мо- . мент, то может произойти ложное.сра- 15 батывание, если включение устройства произойдет непосредственно за нулевым значением разности фаз. .Чтобы избежать этого, служит триггер 13 начального переполнения. При включении он устанавливается в "0" и логический "0" с его прямого выхода дает запрет на срабатывание cxe-.

nba 15 совпадения до тех пор, пока нет цикла с переполнением счетчика 7.

В любом цикле,где имеет место переполнение счетчика 7, возможна ситуация, когда на выходе дешифратора 14 есть логическая "1", соответствующая углу сдвига фаз, находящемуся в норме. Чтобы избежать ложного выходного

Формула изобретения сигнала в этом случае, введен триггер

12 текущего переполнения, который при переполнении счетчика 7 устанавливается в положение "1" и с его инверсного выхода поступает запрет на срабатывание схемы 15 совпадения в виде логического "0". По окончании каждого цикла триггер 12 текущего переполнения устанавливается в "0". и,,если в очередном цикле нет переполнения счетчика 7, то .триггер 12 остается в "0" и запрет на срабатывание устройства снимается.

С окончанием измеряемого импульса разности фаз на выходе блока 3 логики возникает логический "0", запрещающий доступ высокочастотных импульсов на вход счетчика 7. В то же время на выходе инвертора,4 возникает логическая "1", разрешающая выработку выходного сигнала. При наличии логических "1" на всех пяти входах схемы 15 совпадения, т.е., при соблюдении всех необходимых yc" ловий, на выходе образуется выходной

65 сигнал также в виде логической

"1"., который расширяется и усилива«тся схемой 18.

В то же время логическая "1", возникающая на выходе инвертбра.4, через схему ИЛИ 8 и элемент задержки 10 установит счетчик 7 в "О", приводя устройство. в исходное состояние и подготавливая его к следую;ему циклу работы, который начинается с приходом очередного импульса последовательности с . Наличие элемента задержки 10 обеспе:..ивает установку счетчика 7 в "0" после начала вы- работки выходного сигнала. Элемент .задержки 11 обеспечивает в конце цикла установку в "0" триггера 12 текущего переполнения после установки в

"0" счетчика 7, что исключает воэможность ложного срабатывания устройства в цикле с переполнением счетчика 7, поскольку сначала появляется запрет (логический,"0") на выходе ,дешифратора 14 и лишь зарем разрешение (логическая "1") на инверсном выходе триггера 12 текущего переполнения. !

Таким образом, устройство вырабатывает команду на включение в первом же периоде напряжения при условии, что включение устройства проИзошло в любой момент до наступления допустимого угла опережения совпадения фаэ синхронизируемых напряжений, или в следующем периоде напряжения биения, если включение устройства произошло в весьма узкой зоне допустимых углов. Все это определяет повышение быстродействия предлагаемого, устройства.

Устройство для синхронизации генераторов переменного тока, содержащее формирователи импульсов с выходами для подключения на напряжения генераторов, причем выходы формирователей подключены к блоку логики, счетчик импульсов со счетным входом, подключенным к выходу двухвходовой схемы совпадения, первый вход которой подключен к блоку логики, а второй вход — к генератору высокочастотных импульсов, дешифратор с входами, подключенными к .соответствующим разрядам счетчика импульсов, блоки запрета по разности частот и разности напряжений и формирователь выходного импульса, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия устройства, -оно снабжено схемой определения начала измерения угла включения, содержащий два статических триггера, первые

983892 входы которых объединены и подключены к выходу переполнения счетчика импульсов, первый элемент задержки, выход которого подключен к входу второго элемента задержки и к установочному входу счетчика импульсов, выход второго элемента задержки подключен к второму входу второго статического триггера, схемой установки нуля, выход которой подключен к второму входу первого статического триггера и второму входу дополнительно введенной схемы ИЛИ, первый вход которой подключен к выходу дополнительно введенного инвертора со входом, Подключенным к выходу блока логики, а выход схемы ИЛИ подключен к входу первого элемента задержки, выходной схемой совпадения, входы которой подключены к выходам блоков

5 запрета по разности частот и напряжения, дешифратора, статических триггеров, инвертора, а выход . — к входу формирователя выходного импульса.

Источники информации, принятые во внимание при экспертизе

1. Патент США 9 3588519, кл. 307-87, 1971.

2. Авторское свидетельство СССР

Р 349890, кл. Н 02 У 3/42, 1976.

983892

Угол ол оезкенцг яг в уорде

7- Иереиолияетщ

Угол олергжания не в иоргие

7-не лерегвлняется

Угол олереже ".я е норше ФдЮ

РР1 ЩЙЙИЙВ юк ИЮИИИ аюМ Лмюд мрюык имберсмьй Йуо Ьла5 4

Ф/хаУ17

8eNd4

ФмгоР Ю

Составитель К.Фотина

ТехредМ.гладь Корректор М.Демчик

Редактор Н.Бобкова

Эаказ 9945/68 Тираж 669 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. ПРоектная, 4