Устройство для обнаружения потери импульса

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Саевтских

Социалистических

Ресттубник >984018

/ (61) Дополнительное к авт. свид-ву

}фф}-М К и 3 (22) Заявлено 31. 07. 81 (21) 32б 5492/18-21 с присоединением заявки HP— (23) Приоритет

Н 0.3 К 5/153

Н 03 1(5/19

Государственный комитет

СССР ио делам изобретений и открытий

1.вЗ} УДК 621. 374 (088.8) Опубликовано 23.12.82. Бюллетень HP 47

Дата опубликования описания 231282

H.A. Рагимов, М.Н. Ганкин, Э.К. Тагк|Ъ,«т „ и P.Ñ. Бабаев „., " - "- д, -

"-.а:,.:=", I

Азербайджанский институт нефти - -"."" ««1 / им. М. Азизбекова (72) Авторы изобретения (713 Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ПОТЕРИ

ИМПУЛЬСА

Изобретение относится к импульсной технике и может использоватьсят например, для обнаружения потери импульсов в последовательности импульсов.

Известно устройство для обнаружения потери импульса, содержащее триггер, квазиселекторы, элементы

И, элемент НЕ, ИЛИ (1).

Недостатками этого устройства являются его сложность и низкая достоверность результатов работы.

Наиболее близким по технической сущности к изобретению является устройство для обнаружения потери импульсов, содержащее квазиселектор, вход которого подключен к входам устройства и элемента задержки, а вы.ход — к.первому входу элемента И, а выход элемента задержки соединен с

S-входом RS-триггера, R-вход которого подключен к выходам элемента И устройства, а выход RS-триггера сое-. динен с вторым входом элемента И f2), Однако известное устрОйство будет работать неверно при потере подряд двух следующих друг за другом импуль сов последовательности, так как формирует сигнал лишь только о первом потерянном импульсе из последовательности, что снижает надежность обнаружения потери импульсов.

Цель изобретения — повьыение надежности обнаружения потери импульCOB °

Поставленная цель достигается тем, что в устройство для обнаружения потери импульса, содержащее квазиселектор, первый вход которого подключен к входу устройства, а выход - к первому входу элемента И, элемент задержки, выход которого подключен к S-входу RS-триггера, выход которого соединен с вторым входом элемента

И, введен элемент ИЛИ, первый вход которого подключен к входу устройст эа и к R-входу RS-триггера, а, выход элемента ИЛИ подсоединен к второму входу квазиселектора, выход которого соединен с выходом устройства и с входом элемента задержки, при этом выход элемента И подключен к второму входу элемента ИЛИ.

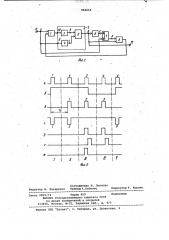

На фиг. 1 показана функциональная схема устройства, на фиг. 2временные диаграммы его работы.

Устройство для обнаружения потери импульса состоит из элемента 1

ИЛИ, квазиселектора 2, состоящего из элемента 3 задержки, элемента НЕ

984018 4 запирание второго входа элемента И 8 только после прохождения импульса через его первый вход. В то же время импульс, поступивший на вход 10 квазиселектора, задерживается в элементе

5 3 и через время Т> появляется на первом входе элемента И 5 (фиг. 2, поз.

17.ф ). Если в зто время появится на . входе 11 четвертый импульс из контролируемой последовательности, то

10 на выходе элемента И 5 .и выходе 12 устройства не формируется сигнал.

Если же четвертый импульс отсутствует, то на выходе элемента И 5 и выходе 12 и устройства (фиг. 2, поз.

15 IV P ) формируется сигнал, сигнализирующий о пропадании импульса в контролируемой последовательности. Сигнал с выхода элемента И 5 не проходит через элемент И 8 на вход эле20 мента ИЛИ 1. При появлении на входе

11 пятого импульса из контролируенмой последовательности последний перебрасывает RS-триггер 7 в исходное сосТояние и устройство продол25 жает работать по описанномУ процессу, Таким образом, введение элемента

ИЛИ, подключенного первым входом ко входу устройства и к Й-входу К$-триггера, а выходом ко второму входу квазиселектора, выход которого соединен с выходом устройства и входом элемента задержки, а выход элемента

И подключен ко второму входу элемента ИЛИ позволило в предлагаемом устройстве повысить надежность обнаружения потери импульса, что.выгодно отличает его от известных устройств подобного типа.

Формула изобретения

4, элемента И 5, элемента 6 задержки, RS-триггера 7, элемента И 8, первый 9 и второй 10 входы квазиселектора 2.

Контролируемая импульсная последовательность поступает на вход 11 устройства, а сигнал потери импульса возникает на выходе, 12 устройства.

В исходном состоянии.при отсутствии импульсов на входе 11 устройства, на выходах элементов ИЛИ 1, И. 5, И 8, рлементов 3,6 задержек — нулевые

Уровни, а на выходе элемента НЕ 4 — . единичный уровень.

Первый импульс из контролируемой импульсной последовательности поступает через элемент ИЛИ 1 на вход 10 квазиселектора, где затем задерживается элементом 3 задержки на время

Т, равное периоду следования импуль сов (фиг. 2 8 ). Одновременно с этим этот импульс поступает на вход элеме та HE u R. — вход RS-триггера 7, уста навливая последний в нулевое состояние (фиг. 2, поз. 1,").

При этом на втором входе элемента

И 8 начинает действовать разрешающий потенциал. Через время Т на выходе элемента 3 задержки появляется первый задержанный импульс (фиг. 2, поз

II 8 ) и поступает на первый вход элемента И 5, а на входе 11:.Устройства — второй импульс из контролируе мой последовательности (фиг. 2, поз.

II Q ). Последний инвертируется элементОм НЕ 4 (фиг. 2, поз. II 2.) и поступает на второй вход элемента И

5, запрещая на время его действия ,прохождение первого импульса с выхода элемента 3 задержки через элемент

И 5, В результате этого нулевой уро- 4р вень на выходе элемента И 5 не меняется (фиг. 2, поз. I I д ) . Второй импульс также. задерживается в элементе 3 и через время Т появляется на первом входе элемента И 5. В то 45 же время на входе 11 должен был по.ступить третий импульс из .контролируемой последовательности (фиг. 2, поз. IIIg ) . .Иэ-за его отсутствия на выходе элемента EE 4 действует единичный уровень (фиг. 2, поз. IIIZ) и второй импульс проходит через элемент И 5 на выход квазиселектора 2 и выход 12 устройства (фиг. 2, поз.

III Д ), сигнализируя о пропадании импульса. в контролируемой последовательности. Импульс с выхода элемента И 5 проходит через элемент И 8 (фиг. 2, поз. III ) и второй вход элемента ИЛИ 1 на вход 10 квазиселектора 2 и одновременно с этим че- <0 рез элемент б задержки (фиг. 2, поз. III 8 ) на вход триггера 7 (фиг. 2, поз. IIIД ). Элемент б обеспечивает установку. триггера 7 в единичное состояние, а следовательно, 65

Устройство для обнаружения потери импульса, содержащее квазиселектор, первый вход которого подключен к входу устройства, а выход — к первому входу элемента И, элемент задержки, выход которого подключен к

S-входу RS- òðèããåðà, выход которого соединен с вторым входом элемента

И, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности обнаружения потери импульса, в него введен элемент ИЛИ, первый вход ко- торого подключен к входу устройства и к R-входу RS-триггера, а выход элемента ИЛИ подсоединен к второму входу кваэиселектора, выход которого соединен с выходом устройства и с входом элемента задержки, при этом выход элемента И подключен к второму входу элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 399057, кл. Н 03 К 5j18, 1973.

2. Авторское свидетельство СССР

9 621081, кл. Н 03 К 5/18, 24 ° 02 77 °

-984018

Составитель М. Леонова

Редактор В. Лазаренко Техред A.Áàáèíåö

Корректор Н. Король;

Филиал ППП "Патент", г. Ужгород, Ул. Проектная, 4

Заказ, 9955/74 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Жг35 Раушская наб., д. 4/5