Делитель частоты следования импульсов с переменным коэффициентом деления

Иллюстрации

Показать всеРеферат

(7l ) Заявитель (54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

С ПЕРЕМЕННЫИ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

Изобретение относится к радиосвязи и предназначено для использования в цифровых синтезаторах частоты, По основному авт. св. в" 940315 известен делитель частоты следования импульсов, содержащий делитель часто- ты с управляемым коэффициентом деления, информационный вход которого соединен с входной шиной, а входы управления подключены к выходам параллельного регистра, первый вход которого соединен с шиной сигнала разрешения записи, а остальные входы подключены к выходам последовательного регистра, первый вход которого соединен с шиной тактового сигнала, элемент И, элемент 1

ИЛИ, первый вход которого соединен с шиной информационного сигнала, второй вход подключен к выходу элемента И, а выход соединен Со вторым входом последовательного регистра, последний выход которого соединен с первым входом элемента И, второй вход которого сое динен с шиной управляющего сигнала,, а

2 первый выход последовательного регистра соединен с дополнительным входом управления делителя частоты с управляемым коэффициентом деления (1 ).

Однако известное устройство имеет недостаточно высокую точность умно::ения.

Цель изобретения - повышение точности деления путем снижения амплитуды и периода фазовой девиации выходной импульсной последовательности.

Поставленная цель достигается тем, что в делитель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель частоты с ynpasляемым коэффициентом деления, информационный вход которого соединен с входной шиной, а входы управления подключены к выходам параллельного регистра, первый вход которого соединен с шиной сигнала разрешения записи, а остальные входы подключены к выходам последовательного регистра, первый вход которого соединен с шиной тактового

Т а б л и ц а 1

Двоичная последовательность

Номера разряда регистра 3

1 2 3 " 5 6 7 а о о о о о

9 10 и/10

1/10

0 0 О

1 0 0 1 О 0 О О 0 0

0 1 а 1 0 0 0 о -0

1 О 1 1 1 0 0 О 0 О

1 1 1 1 I О О 0 0 О

1 1 1 O 0 0 0

1 1 1 1 1 1 О 1 О 0

1 1 1 1 1 1 О 1 О, 1

1 1 1 1 1 1 1 0 1 1

2/10

3/10

4/1 О

5/10

6/10

7/10

8/10

9/10

3 984055 сигнала, элемент И и элемент ИЛИ, первый вход которого соединен с шиной информационного сигнала, второй вход подключен к выходу элемента И, а выход соединен со вторым входом после5 довательного регистра, последний выход которого соединен с первым входом элемента И, второй вход которого соединен с шиной управляющего сигнала, введены элемент И-НЕ и дополнительные 1 элементы ИЛИ и И, первые входы которых соединены с выходом первого разряда последовательного регистра, вторые входы - с выходом (0,5И+1.)-ro разряда последовательного регистра, а вы-15 ходы - с входами элемента И-НЕ, при этом первый и второй дополнительные входы управления делителя частоты с управляемым коэффициентом деления соединены с выходами соответственно дополнительного элемента И и элемента

И-НЕ 31 3.

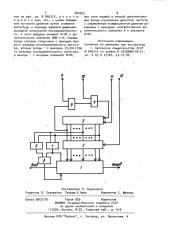

На чертеже представлена структурная схема предлагаемого устройства.

На шине 9 делителя присутствует сигнал, разрешающий поступление информации с соответствующего выхода регистра 3 на его информационный вход через элементы 6 и 4. 55

Каждый импул ь с опорной частоты, .поступая на тактовый вход"регистра.7, замкнутого в кольцо, сдвигает занесен4

Оно содержит делитель 1 частоты с управляемым коэффициентом деления, параллельный регистр 2, последовательный регистр 3, элементы ИЛИ 4 и 5, элементы И 6 и 7, элемент И-HE 8, шину 9 управляющего сигнала, шину 10 информационного сигнала, шину 11 тактового сигнала, шину 12 сигнала разрешения. записи. !

Устройство работает следующим об-. разом.

В режиме деления частоты по шине.

11 на первый вход регистра,3 поступают импульсы опорной частоты, которая численно равна выходной частоте делителя частоты. В регистре 2 записан код целой части коэффициента деления

К. В регистре 3 занесена двоичная последовательность, соответствующая дробной части коэффициента деления

n/È, где М для десятичной дроби равна I0. Данные приведены в табл. l. ный в него код на один разряд. Если при этом в первом или в шестом разряде регистра 3 присутствует логическая единица, то элемент 5 будет находиться в единичном состоянии и сигнал с его выхода поступит через элемент 8 на вход переключения с коэффициента деления К на коэффициент К+0,5 дели5 . 984055 6 теля 1. Если же логическая единица ключит делитель 1 с коэффициента деприсутствует и.в первом и в шестом ления К на коэффициент К+1, разряде регистра 3, то в единичном В соответствии с логикой работы состоянии будет находиться и элемент элементов 5-8 на переключающие входы

7. Соответствующий логический уровень, делителя 1 будут поступать сигналы, присутствующий на входе элемента 7, изменяющие его коэффициент деления запретит возникновение сигнала на вы- на величину 1 или 0,5. Данные привеходе элемента 8 в свою очередь, пере- дены в табл. 2.

Т а б л и ц а 2

Двоичная посЛ довательность

Номер цикла деления

I)1t1t t t1

1 2 3 4 5 6 7 8 9 10 и/10

0,5 0 0

1/10

0,5 0 0 0

05 0 05 0

05 0 05 0

05 0 05 0 0

2/10

0,5 0,5 0 0,5 0 0 5

3/10

4/1О

0 5 0 0 5 0 5 0 5 0 5 0 0 5 0,5 0,5

0,5 0,5 0,5 0,5 0,5 0,5 0,5 0,5 0,5 0,5

1 0,5 0,5 0 5 0,5 1 0,5 0 5 0,5 0 5

5/10

6/10

05 1 05 05 1 05 1

7/10

05 05

1 0 5

8/10

05 1 05

1 0,5 1

0,5 1

9/10

1 0 5 1 1

Из табл. 2 видно, что дробный коэффициент деления реализуется за время в течение любых пяти полных циклов деления входной частоты.

После принятия решения о изменении коэффициента деления на шину 9 поступает логический уровень, запрещающий поступление информации через элемен» ты 4 и 6 с выхода на вход регистра 3.

За время в течение 10 периодов такто- вой частоты в регистр 3 вводится код целой части нового коэффициента деления, затем осуществляется его перепись в регистр 2 сигналом, поступающим по.шине 12. После чего в течение .

10 периодов опорной частоты осуществляется заполнение регистра 3 последовательным соответствующим дробной части коэффициентом деления, а затем регистр запирается в кольцо сигналом, поступающим по шине 9., Через пять циклов, начиная с момента заполнения последовательного регистра кодом дробной части коэффициента деления,. делитель частоты следования импульсов выполняет функцию делителя с дробным коэффициентом деления.

Таким образом, в предлагаемом делителе частоты следования импульсов с переменным коэффициентом деления последовательный регистр выполняет не только функцию преобразователя последовательного кода в параллельный, но и функцию блока дробных разрядов. При этом достигается минимальная величина амплитуды и периода фазовой девиации выходной импульсной последовательности за счет равномерного распределения управляющих воздействий на управляющие входы делителя 1 за число циклов деления входной частоты, в два раза меньшее величины знаменателя дробных разрядов.

Формула изобретения

Делитель частоты следования импульсов с переменным коэффициентом делеСоставитель О. Кружилина

Редактор В. Лазаренко Техред О.Неце Корректор С. Шекмар

Заказ 9957/76

Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

7 984055 8 ния по авт. св. У 940315, о т л и ч а- при этом первый и второй дополнителью шийся тем, что, с целью повыше- ные входы управления делителя частоты ния точности деления путем снижения с управляемым коэффициентом деления соамплитуды и периода фавовой- девиации единены с выходами соответственно довыходной импульсной последовательнос- полнительного элемента И и элемента ти, в него введены элемент И-НЕ и до" И-НЕ. полнительные элементы ИЛИ и И, первые входы которых соединены с выходом пер- Источники информации, вого разряда последовательного регист- принятые во внимание при экспертиз ра, вторые входы - с выходом (0,5M+1 )- о 1. Авторское свидетельство СССР го разряда последовательного регистра, У 940315 по заявке У 3220698/18-21, а выходы - с входами элемента И-НЕ, кл. Н 03 К 23/02, 23. 12.80. !