Сумматор в коде "м из n

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социапистнческик рес убл

< >985?81 (61) Дополнительное к авт. свид-ву(22) Заявлено I 07,81 (21) 3315867/18«24 с присоединением заявки М (23) Приоритет (sl jN. Кл.

G 06 F 7/49

3Ьоудароткнны6 комитвт

СССР кв лолам кзоорвтекий и открытки

Опубликовано 30, 12,82. Бюллетень ¹ 48

Дата опубликования описания 30, 12.82 (53) УДК 681.325 (088. 8) (72) Авторы изобретения

Е, И, Брюхович и В.А. Гуменюк

Киевский ордена Трудового Красного Знамени индтиФ т инженеров гражданской авиации — — " Д - -: —:: (71) Заявитель (54) суннАтор в кодк "И из н"

Устройство относится к вычислительной технике и предназначено для сложения чисел, представленнйх в коде "И из Н", Известен сумматор, работающий в пятерично-двоичном коде, содержащий первую и вторую группы входов для подачи первой и второй групп параллельных сигналов, представляющих десятичные цифры в соответствии с нормальной числовой формой .записи.

Преобразующее устройство состоит иэ большого числа элементов И и ИЛИ и осуществляет преобразование сигналов с первой и второй групп входов из

35 двоично-десятичной системы в пятерично-двоичную. Матрица сумматора, содержащая емкостные элементы для селективной связи выходов элементов

И и ИЛИ, предназначена для получения сигналов суммы (1 ).

Недостатком данного устройства является большое количество оборудо- ; вания.

Известен десятичный двухразрядный сумматор в коде "2 из 5", содержащий блок местного управления, преобразователи кодов операндов младшего и старшего разрядов, матрицы сложения младшего и старшего разрядов, блок коррекции младшего и старшего, разрядов, блоки переносов младшего и старшего разрядов соответственно, шифратор младшего разряда, 6локи выдачи старшего разряда суммы Г2).

Недостатком укаэанного сумматора является малое быстродействие.

Наиболее близким к предлагаемому является двухразрядный сумматор в коде "И из Й", младший разряд ко-. торого содержит блок выдачи суммы, шифратор, блок контроля, матрицу сложения, блок переноса, причем выходы блока выдачи суммы соединены с выходными шинами устройства, первый и второй выходы блока контроля соединены с первым и вторым входами блока выдачи суммы соответственно, выходы шиф985781

1о го

3 ратора соединены. с третьей группой входов блока выдачи суммы, первая и вторая группы входов матрицы сложения соединены с входными шинами устройства, первая и вторая группы входов блока контроля соединены с входными шинами, выходы матрицы сложения соединены с входами шифратора и блока переноса, выходы блока переноса соединены с выходными. шинами устройства (3 ).

Недостатком известного сумматора является невысокое быстродействие вследствие необходимости прохождения входных сигналов последовательно через три блока до образования кодового слова результата на выходных шинах устройства, Цель изобретения - повышение быстродействия сумматора в коде "И из из М", Поставленная цель достигается тем, что в сумматоре в коде "М из М", содержащем матрицу сложения, блок кон.г5 троля и блок выдачи суммы, причем первая и вторая группы входов матрицы сложения соединены соответственно .с шинами первого и второго слагаемых устройства, первая и вторая групзо пы входов блока контроля соединены соответственно с первой и второй шинами контроля устройства, а первый и второй выходы блока контроля подключены соответственно к первому и второму управляющим входам блока выдачи суммы, выходы которого являются группой выходов суммы устройства, первая группа выходов матрицы сложения соединена с первой группой информационных входов блока выдачи сум- "о мы, а вторая группа выходов матрицы сложения является группой выходов переноса устройства, причем матрица сложения состоит из многовходовых элементов И, имеющих по .М+1 идентич- 4s ных, но гальванически независимых выходов, i-е выходы элементов И матрицы сложения (!.4 i $ М), которые соответствуют одинаковым разрядам кодовых слов результатов, содержащим 5о

"единицы", соединены с соответствующими i-ми выходами первой группы выходов матрицы сложения, (М+1)-е выходы элементов И матрицы сложения, которые соответствуют одинаковым пе-. ss реносам в старший разряд, соединены с соответствующими выходами второй группы выходов матрицы сложения, 4

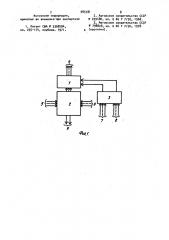

На фиг, 1 представлена блок-схема сумматора в коде "Миз М"; на фиг, 2 - схема матрицы сложения для кода "2 и 4" при основании системы счисления р=4.

Устройство..содержит блок 1 выдачи суммы, матрицу 2 сложения и блок 3 контроля .

Выходы блока 1 соединены с выходами суммы 4, первый и второй выходы блока 3 соединены с первым и вторым управляющими входами блока 1 соответственно, первая .группа выходов блока 2 соединена с первой группой ин" формационных входов блока 1, первая и вторая группы входов блока 2 соединены с шинами 5 и 6 первого и второго слагаемых устройства, первая и вторая группы входов блока 3 соеди нены с шинами 7 и 8 контроля устройства, вторая группа выходов блока 2 является группой выходов переноса 9 устройства. Устройство также содержит элемент И 10.

Блок 1 выдачи суммы представляет собой группу из М трехвходовых элементов И, где М - количество разрядов кодового слова. Входы каждого элемента И подключены к соответствующим входам блока 1. Выходы элементов И являются выходами блока 1.

Матрица 2 сложения представляет собой матрицу многовходовых эле.ментов И, Количество входов элемента М равно 2 М. Входы элементов И матрицы 2 соединены с определенными шинами кодов слагаемых согласно выбранному алфавиту, Шины кодов слагаемых соединены с вхсдами матрицы 2. Каждый элемент И матрицы 2 имеет по И+1 идентичных, но гальванически независимых выходов. Такой элемент может представлять, например, группу из М+! многоэииттерных транзисторов, i-e выходы элементов

И матрицы 2 (1 4 i < М), которые соответствуют одинаковым разрядам кодовых слов результатов, содержащим

"единицы", соединены шинами с соответствующими 1-ми -выходами первой группы выходов матрицы 2, образуя при этом так называемый "проводной шифратор" .в коде "M из М". В качестве примера на фиг. 2 показана коммутация выходов элементов И матрицы

2, позволяющая получить на выходах первой группы выходов этого блока

985781 сигналы, соответствующие следующему алфавиту:

0 0011 1 0101 ю 2 1001 ю 3 0110в где 0-й разряд кодового слова- S крайний справа.

М+1-е выходы элементов И матрицы 2, которые соответствуют одинаковым переносам в старший разряд, соединены шинами с соответствующими (ПО или П1) выходами второй группы выходов матрицы 2, Значения слагаемых, которые в виде кодовых слов поступают на входы элементов И, находящихся на пересечении соответ- 15 ствующих координат, приведены в квадратных .скобках (сами входы не показаны). блок 3 контроля представляет собой схему контроля для кода "М из 20

М" (полный дешифратор или пороговую схему), на входы которой подаются кодовые слова, представляющие собой обратные коды слагаемых.

Устройство работает следующим об- 25 разом, Слагаемые в коде "М из М" поступают на матрицу 2 сложения. Одновременно обратные коды слагаемых поступают на блок 3 контроля, Появление Зв нескомпенсированной ошибки приводит или к появлению сигналов на выходах сразу нескольких элементов И матрицы 2 сложения, или к отсутствию сигналов на их выходах. В первом случае 35 отсутствует разрешающий сигнал на выходе соответствующей схемы контроля (входящей в состав блока 3 кон роля)

В обоих случаях на выходах сумматора сигналы результата отсутствуют.

Если в кодовых словах слагаемых длиной М будет точно М ."единиц", то с выходов матрицы 2 сложения сигналы поступают на соответствующие входы первой группы информационных входов блока 1 выдачи суммы, одно временно на первый и второй управляющие входы этого блока поступают сигналы с выходов блока 3 контроля, C выходов блока 1 выдачи суммы сиг50 налы, "оответствующие результату (закодированному матрицей 2 сложения в коде "М" из М") сложения, поступают на выходы суммы устройства.

Рассмотрим работу матрицы, изоб55 раженной на фиг. 2, на конкретном примере, При сложении чисел 1 (код

0101) и 2 (код 1001) срабатывает, например, элемент 10. Сигналы с выходов этого элемента поступает на выходы первой группы выходов матрицы сложения, соответствующие 1-му и 2-му разрядам кодового слова суммы в данном разряде, и на выход второй группы выходов матрицы сложения, соответствуаций переносу нуля в стар ший разряд.

Положительный эффект от внедрения предлагаемого устройства заключается в повышении быстродействия, так как в данном устройстве сигналы до получения результата сложения проходят через два блока, а в прототипечерез три блока.

Формула изобретения

Сумматор в коде "М из М", содержащий матрицу сложения, блок контро" ля и блок выдачи суммы, причем первая и вторая группы входов матрицы сложения соединены соответственно с шинами первого и второго слагаемых устройства, первая и вторая групяы входов блока контроля соединены соответственно с первой и второй шинами контроля устройства, а первый и второй выходы блока контроля подключены соответственно к первому и второму управляющим входам блока выдачи суммы, выходы которого являются группой выходов суммы устройства, отличающийся тем, что, с целью повышения быстродействия сумматора, первая группа выходов матрицы сложения соединена с первой группой информационных входов блока выдачи суммы,.;а вторая группа выходов матрицы сложения является группой выходов переноса устройства, причем матрица сложения состоит из многовходовых элементов И, имеющих по

М+1 идентичных, но гальванически независимых выходов, i-e выходы элементов И матрицы сложения (1 <

< i < M) которые соответствуют одинаковым разрядам кодовых слов ре" зультатов, содержащим "единицы", соединены с соответствующими i-ми выходами первой группы выходов мат" рицы сложения, (М+1) -е выходы элементов И матрицы сложения, которые соответствуют одинаковым, переносам в старший разряд, соединены с соответствующими выходами второй группы выходов матрицы сложения, 7, Источники информации, прйнятые во внимание-: при экспертизе

1. Патент США N 3308284, кл. 235-174, опублик. 1971.

985781 8

2, Авторское свидетельство СССР и 259480, кл, G 06 F 7/50 1968.

3 Авторское свидетельство СССР 798828, кл, G 06 F 7/50, 1978 (прототип).

985781 ираж 3 одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, N-35, Рауаская наб,, д, 4/5

Заказ 101

Филиал ПП атент, г. жгород, ул. роектная, Составитель Н. Захаревич

Редактор Н.Стащищина Техред N.Êàñòåëåâè÷ . Корректор 0 ° » "