Цифровой фильтр

Иллюстрации

Показать всеРеферат

А. N. Павельев, Л, A. Рябини и В. А. Новичихин " - .: .: (1 (72) Авторы изобретения (7I) Заявитель (54) БИФРОВОЙ ФИЛЬТР

Изобретение относится к цифровой обработке сигналов, в частности к цифровой фильтрации, н может быть использовано в различных цифровых комплексах.

Известен цифровой фильтр, содержаший элемент И-НЕ, дифференцнриуюший элемент и одновибратор 1 J .

Недостатком этого устройства являются ограниченные функциональные возможности, что связано с невозможностью уп- равления полосой пропускания. 1О

Известен также цифровой фильтр, содержащий элемент И -НЕ, дифференцирую ший элемент, формирователь импульсов, генератор импульсов, три элемента И, элемент ИЛИ и два делителя частоты с переменным коэффициентом деления (ДПКД) г .

Однако этот фильтр имеет недостаточно высокую надежность вследствие нера ботоспособности при частотах на входе фильтра, в два и более раза выше нижней граничной частоты полосы пропускания, Кроме того, данное устройство имеет огра2 .ниченную область применения так как может работать только в режиме полосового пропускающего фильтра.

Бель изобретения — повышение надежности работы устройства и расширение функциональных возможностей.

Для этого в цифровой фильтр, содержаший делители частоты с переменным ко эффициентом деления, счетный вход каждого из которых через соответствуюший элемент И подключен к выходу генератора импульсов, второй вход каждого элемента

И подключен к прямому выходу соответствующего делителя частоты и формирователь импульсов, вход которого подключен к входной шине, а выход к первому входу элемента H-HE, второй вход которого соединен с прямым выходом первого делителя частоты, включены дополнительные элементы И-НЕ, первые входы которых соединены с входом разре1иения записи первого делителя частоты и входом сбро са второго делителя частоты и подключе ны к выходу формирователя импульсов, вто

3 9859 рые входы первого и второго дополнитель ных элементов И-НЕ объединены и подключены к инверсному выходу второго делителя частоты, второй вход третьего дополнительногоэлемента И-НЕ- к прямому

5 выходу второго делителя частоты, а третий р вход первого дополнительного элемента

И-НЕ объединен с входом разрешения записи второго делителя частоты и подключен к инверсному входу первого делителя частоты.

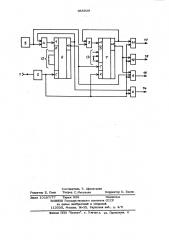

На чертеже представлена структурная электрическая схема цифрового фильтра.

Цифровой фильтр содержит входную шину 1, формирователь 2 импульсов, генератор 3 импульсов, элементы И 4 и 5„ делителей частоты с переменным коэффициентом деления (ДПКД) 6 и 7, элемент

И-НЕ 8, дополнительные элементы И-НЕ

9- 11, входы 12 и 13 установки кодов соответственно ДПКД 6 и 7, выходы 1417 фильтра.

Е1ифровой фильтр работает следующим образом.

Генератор 3 импульсов выдает прямоугольные импульсы с периодом То, которые поступают на первые входы элементов И 4 и 5. При отсутствии импульсов входного сигнала прямые выходы ДПКД

6 и 7 должны находиться в состоянии логического нуля, а инверсные в состоянии логической единицы. Если прямые выходы любого из ДПКД 6 и 7 находятся в состоянии логической единицы, через соответствующий элемент И 4 или 5 раз решается прохождение импульсов с гене- З ратора 3 импульсов на счетный вход соответствующего QIIKQ до тех пор, пока на прямом выходе данного ДПКД не уста новится сигнал логического нуля, запре46 щающий прохождение этих импульсов. На выходах 14 - 17 фильтра при отсутствии импульсов входного сигнала — сигнал ло;гической единицы, на входах 12 и 13 „

ДПКД 6 и 7 подаются коды чисел К и

К„, определяющие соответственно верх45 нюю граничную частоту и полосу пропускания. Входной сигнал подается на вход формирователя 2 импульсов, который выдает импульсы, соответствующие заднему фронту импульсов входного сигнала. Эти импульсы записывают число К в ДПКД

6 и устанавливают ДПКД 7 в нулевое состояние.

Поскольку EtnKQ 7 - в нулевомсостоянии, (снгнал логического нуля на его прямом выходе блокирует прохождение импульсов с генератора 3 импульсов через элемент И 5 на его счетный вход), а

39 4

ДПКД 6 в состоянии k<, то сигнал ло гической единицы на прямом выходе данного QKHQ разрешает прохождение импульсов с генератора 3 импульсов через элемент

И 4 на его счетный вход, и через время 1„

К -Т на прямом выходе ДКПД 6 появится сигнал логического нуля, который блокирует прохождение импульсов на его счетный вход, а на его инверсном выходе появится сигнал логической единицы, который, поступая на вход разрешения записи, записывает число, Кп в ДПКД 7. Так как

ДПКД 7 в состоянии К„,, то сигнал логической единицы на его прямом выходе разрешает прохождение импульсов с генератора 3 импульсов через элемент И 5. на счетный вход данного делителя, и через время 4 =Кп- Т0 на прямом выходе

ДПКД 7 появится сигнал логического нуля, который блокирует прохождение импульсов с генератора 3 импульсов на его счетный вход.

Таким образом, если период входных импульсов Т„v (К + К„) То, то к приходу очередного входного импульса на прямых выходах ДПКД 6 и 7 будет сигнал логического нуля, так как сигнал логической единицы на прямом выходе

ДПКД 6 будет в течение времени „ =

= К -1, а на прямом выходе ЛПКД 7в течение вРемени t2 = Кп ц, Если период входных импульсов К,Т <

<Т, < (К + К,„)-Т,, то к периоду очередйого входного импульса на прямом выходе ДПКД 6 будет сигнал логического нуля, а на прямом выходе ДПКД 7 будет сигнал логической единицы, так как сигнал логической единицы на прямом выходе ДПКД 6 будет в течение времени „=

= К .То, а на прямом выходе ДПКД 7 сигнал логической единипы будет через время 4 Ê . Тяи в течение времени

1 = (Тх - К -ф,, поскольку каждым им» пульсом с формирователя 2 импульсов

ДПКД 7 сбрасывается в нулевое состояние.

Если период входных импульсов т„<

< К - То; то к приходу очередного входного импульса на прямом выходе ДПКД 6 будет сигнал логической единицы, а на прямом выходе ДПКД 7 - сигнал логического нули, поскольку каждым импульсом с формирователя 2 импульсов ДПКД

6 будет устанавливаться в состояние К а ДПКД 7 в нулевое состояние, а сигнал логического нуля на прямом выходе ДПКД

6 и сигнал логической единицы на прямом выходе ДПКД 6 и сигнал логической единипы на прямом выходе ДПКД 7 могут

5 9859 быть через время < = к, т„. Следовательно, на выходе 14 элемента -HE 8

1 будут импульсы с частотой >< - nof u сколЬку на его первь|й вход поступают импульсы с формирователя 2, соответствующие входному сигналу, à íà его второй вход — сигнал с прямого выхода

ДПКД 6.

На выходе 15 элемента И-НЕ 9 будут импульсы с частотой ((y х по скольку на его первыи вход поступают импульсы с формирователя 2 импульсов, соответствующие входному сигналу, а на

I5 второй и третий его входы — сигналы с инверсных выходов ДПКД 6 н 7.

HB выходе 16 элемента И-НЕ 1 0 будут

1 1 М импульсыс частотой р +g iy fg g y 2y

f ufo fo поскольку на его первый вход поступают импульсы с формирователя импульсов 2, соответствующие входному сигналу, а на его второй вход — сигнал с инверсного выхода ДПКД 7.

На выходе 17 элемента И-HE 11 будут импульсы с частотой fg +y f п>о fо поскольку на его первый вход поступают щ импульсы с формирователя 2, соответсч вующие входному сигналу, а на его второй вход - сигнал с прямого выхода ДПКД 7.

Изменяя коды на. входах 12 и 13 можно обеспечить независимую регулировку 35 верхней граничной частоты и полосы пропускания, а изменяя частоту генератора 3 импульсов можно обеспечить перестройку частоты пропускания с обеспечением процентно-постоянной полосы пропускания, т. е. постоянного отношения ширины полосы пропускания к верхней граничной часто те э

Таким образом, предлагаемый цифровый фильтр обладает более высокой надежностью, так как частота входного сигнала не влияет на работоспособность устройс пза.

Кроме того, в устройстве значительно расширена область применения благодаря

39 6 обеспечению работы фильтра в любых режимах, т. е. фильтра низких частот, фильтра верхних частот, полосового пропускаю» щего и полосового загражда1ощего филы4. ров.

Формула изобретения цифровой фильтр, содержащий делители частоты с переменным коэффициентом деления, счетный вход каждого из которых через соответствующий элемент И подключен к выходу генератора импульсов, второй вход каждого элемента И подключен к прямому выходу соответствующего делителя частоты с переменным коэффициентом деления, и формирователь импуль сов, вход которого подключен к входной шине. а выход к первому входу элемента

И-НЕ, второй вход которого соединен с прямым выходом первого делителя частоты, о т л и ч а ю ш и и с я тем, что, с целью повышения надежности работы устройства и расширения функциональных возможностей, в него включены дополнительные элементы И-НЕ, первые входы которых объединены с входом разрешения записи первого делителя частоты и входом сброса второго делителя частоты и подключены к выходу формирователя импульсов, вторые входы первого и второго дополнительных элементов И-НЕ объединены и подключены к инверсному выходу второго делителя частоты, второй вход третьего дополнительного элемента И-НЕ— к прямому выходу второго делителя частоты, а третий вход первого дополнительного элемента И-НЕ объединен с входом разрешения записи второго делителя частоты и подключен к инверсному входу пер вого делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Электроника, 1973, % 4, с. 71, рис. 6.

2. Авторское свидетельство СССР

% 691871, кл. Я 06 F 15/36, 1977 (прототип).

985939

Составитель Т. Афанасьева

Редактор Е. Папп Техред С.Мигунова Корректор О. Билак .

Заказ 10187/77 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаа наб., д. 4/5

Филиал ППП "Патент", г. Ужгорсд, ул. Проектная, 4