Синтезатор частот

Иллюстрации

Показать всеРеферат

3 ч

Д. Г. Нисневнч, В. Л. Гусев и Л. К. Максф ченйова -„.,-- з

1 (72) Авторы изобретения

1 (71) Заявитель (54) СИНТЕЗАТОР ЧАСТОТ

Ф 1

Изобретение относится к радиотехнике и может быть использовано в технике связи, радиолокации и импульсной технике.

Известен синтезатор частот, содержаший соединенные в кольцо управляемый генератор, делитель частоты с переменным g коэффициентом деления, фазовый детектор, сумматор и фильтр нижних частот, последовательно соединенные частотный дискриминатор и блок предварительной настройки, первый выход которого подключен к другому входу сумматора, последовательно соединенные опорный генератор и делитель опорной частоты, при этом первый вход частотного дискриминатора подключен к выходу делителя частоты с перемен- ным коэффициентом .деления, а вторые входы фазового детектора и частотного дискриминатора. объединены и подключены к выходу делителя опорной частоты, и фор20 мирова тель кодов коэффициентов деления, первый выход которого соединен с управляющим входом делителя частоты с переменным коэффициентом деления Ã1 1.

Недостатком известного синтезатора частот является малое быстродействие, определяемое номиналом частоты сравнения и количеством циклов регулирования при настройке на требуемую частоту.

Бель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в синтезатор частот, содержащий со- . единенные в кольцо управляемый генератор, делитель частоты с переменным коэффициентом деления, фазовый детектор, сумматор и фильтр нижних частот, последовательно соединенные частотный дискриминатор н блок предварительной настройки, первый выход которого подключен к другому входу сумматора, последовательно соединенные опорный генератор и делитель опорной частоты, прн этом первый вход частотного дискриминатора подключен к выходу делителя частоты с переменным коэффициентом деления, а вторые входы,, фазового детектора и частотного дискриминатора объединены и подключены к вы

3 9859 ходу делителя опорной частоты, и формирователь кодов коэффициентов деления, первый выход которого соединен с управляющим входом делителя частоты с переменным коэффициентом деления, между

5 другим выходом блока предварительной настройки и входом формирователя кодов коэффициентов деления введены последовательно соединенные индикатор настройки и задатчик коэффициентов деления, а меж- О ду вторым выходом формирователя кодов коэффициентов деления и другим входом задатчика коэффициентов деления введен анализатор точности установки частоты, другой вход индикатора настройки соединен с третьим выходом формирователя кодов коэффициентов деления, а делитель опорной частоты выполнен в виде делителя частоты с переменным коэффициентом деления и его управляющий вход подключен к четвертому выходу формирователя кодов коэффициентов деления.

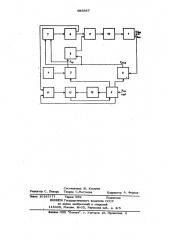

На чертеже приведена структурная. электрическая схема синтезатора частот.

Синтезатор частот содержит управляе- мый генератор 1, делитель частоты с переменным коэффициентом деления (ДПКД)

2, фазовый детектор (ФД) 3, опорный генератор 4„делитель 5 опорной частоты, формирователь 6 кодов коэффициентов де..- @ ления, частотный дискриминатор 7, блок

8 предварительной настройки, сумматор

9, фильтр нижних частот (ФНЧ) 10, индикатор 11 настройки, анализатор 12 точности установки частоты и задатчик

13 коэффициентов деления.

Синтезатор частот работает следующим образом.

Процедура настройки синтезатора состоит из двух этапов, Первый этап — предварительная грубая настройка, осушествляеюо мая блоком 8 предварительной настройки по сигналам частотного дискриминатора 7.

Блок 8 предварительной настройки осуществляет сканирование управляющего

15 напряжения, запоминает уровень напряжения настройки, вырабатывает сигнал окончания этапа. Частота управляемого генератора

1 вводится в полосу синхронизации контура фазовой автоподстройки частоты, в состав которого входит ДПКД 2, ФД 3, сумматор 9 и ФНЧ 10.

На втором этапе настройки по сигналу

ФД 3 производится точная настройка управляемого генератора 1 на требуемуто частоту. При этом возможны два режима работы, выбор которых осуществляется задатчиком 13 коэффициентов деления по сигналу анализатора 12.

Задатчик 13 коэффициентов деления принимает решение о; режиме работы формирователя 6 кодов коэффициентов деления

ДПКД 2 и делителя 5 опорной частотьь

Алгоритм принятия решения можно описать следующим образом: с= с b с = с Ь з где С - выходной сигнал задатчика 13 коэффициентов деления, задающий режим работы формирователя 6 кодов с коэффициентами деления и „„и и с — выходной сигнала задатчика 13 коэффициентов деления, задающий режим работы формирователя 6 кодов с коэффициентами деления Р г,„„и ио — выходной сигнал индикатора 11 настройки, соответствующий этапу точной 1 нас тройки — выходной сигнал индикатора 11 настройки, соответствующий этапу предварительной настройки; и,, и - коэффициенты деления ДПКД

2 соответственно на этапе точной и предварительной настройки; иог, и „„- коэффициенты деления делителя 5 опорной частоты соответственно на этапе точной и предварительной настройки; с — сигнал с выхода анализатора 12, если точность настройки синтезатора на номинал частоты m < ит Зс, <, 5 — сигнал с выхода анализатора 12, если m w тз,„ ти — точность установки частоты, заданная для данного синтезатора.

Задатчик 13 коэффициентов деления может быть реализован с помощью комбинационной логической схемы.

Формирователь 6 кодов выполняет следующие операции: вычисляет значения коэффициентов и п„„и и и запоминает их, при помощи айпарата ценных дробей вьгчисляет значения ип „и и о и запоминает их; на этапе предварительной настройки по команде с задатчика 13 коэффициентов деления подает на управляющие входы QI1KQ 2 и делителя 5 опорной частоты коды коэффициентов деления и „„ и и а на этапе точной настройки коды ид„„ пог или идикд и г ог вычисляет отн:о1 сительную точность m полученного приближения подходящей дроби и выдает значение ит на один из входов анализатора 12 точнос ти.

Функции формирователя 6 кодов могут быть реализованы микро-ЭВМ с соответст вуюшими характерис тиками.

Анализатор 12 точности запоминает значение точности настройки rn д, за5 985947 а данной для данного синтезатора, сравни- м вает значение tn> с п, поступившим от формирователя 6 кодов и вырабатывает следующие сигналы для задатчика 13 ко- п эффициентов деления а или а. S r

Анализатор 12 точности может быть с реализован с помощью запоминающего уст- on ройства и комбинационной логической схе- ча мы. в

Начало и конец первого этапа опреде- 1э ко ляются индикатором 11 настройки, кото- фа рый подает соответствующий сигнал на м задатчик 13 коэффициентов деления. хо

Алгоритм определения этапа можно опи- ро сать следующим образом 15 пе

Ь=ае, Ъ= е °

35 где d - сигнал начала этапа предварительной настройки с выхода формирователя 6 кодов; 20

e — сигнал окончания этапа предварительной настройки с выхода блока 8 предварительной настройки. Кроме того, инди катор 11 настройки запоминает факт выработки сигналов Ь и Ь на время соответствующего этапа.

Предлагаемый синтезатор частот дает возможность повысить быстродействие, - так как в нем сокращается наиболее продолжительный этап- этап предварительной 30 настройки на любую частоту из дискретного множества. При этом сохраняется высокая точность установки требуемого номинала выходной частоты.

Формула изобретения

Синтезатор частот, содержащий соединенные в кольцо управляемый генератор, io делитель частоты с переменным коэффициентом деления, фазовый детектор, суматор и фильтр нижних частот, последовательно соединенные частотный дискриминатор и блок предварительной настройки, ервый выход которого подключен к дру ому входу сумматора, последовательно оединенные опорный генератор и делитель орной частоты, Iпри этом первый, вход! Ф стотного дискриМинатора подключен к

ыходу делителя частоты с переменным эффициентом деления, а вторые входы зового детектора и частотного дискриинатора объединены и подключены к выду делителя опорной частоты, и формиватель кодов коэффициентов деления, рвый выход которого соединен с управляющим входом делителя частоты с переменным коэффициентом деления, о тл и ч а ю ш и и с я тем, что, с целью повышения быстродействия, между дру км выходом блока предварительной настройки и входом формирователя кодов коэффициентов деления введены последовательно соединенные индикатор настройки и задатчик коэффициентов деления, а между вторым выходом формирователя кодов коэффициентов деления и другим входом задатчика коэффициентов деления введен анализатор точности установки частоты, другой вход индикатора настройки соединен с третьим выходом формирователя кодов коэффициентов деления, а делитель опорной частоты выполнен в виде делителя частоты с переменным коэффициентом деления и его управляющий вход подключен к четвертому выходу формирователя кодов коэффициентов деления.

Источники информации, принятые во внимание при экспертизе

1. Зарецкий М. М. и др. Синтезаторы частоты с кольцом фазовой автоподстройки. Л., Энергия, 1974, с. 205 — 211 (прототип) .

986947

Составитель Ю. Ковалев

Редактор С. Пекарь Техред С.Мигунова Корректор А. Ференд.

Заказ 10187/77 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4