Последовательное множительное устройство

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

<„>987620

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (И) Дополнительное к авт. свид-ву (22) Заявлено 1296.81 (21) 3317357/18-24 с присоединением заявки Йо рц м.к.

G 06 F 7/52 (23) Приоритет

Государственный комитет

СССР ио делам изобретений и открытий (53) УДЫ 681. 325 (088. 8) Опубликовано 07.0183. Бюллетень М 1

Дата опубликования описания 070133

A.В. AHHKees, Е.В. Кильчицкий, В.И. Корннйчук,-.В.П. Тарасенко и Я.И. Торошанко (72) Авторы изобретения

Киевский ордена Ленина политехнический ннотитут .= : им.50-летия Великой Октябрьской социалистическоФ =-.. революции (71) Заявитель (54) ПОСЛЕДОВАТЕЛЬНО МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычислительных машин последовательного действия.

Известно устройство для умножения последовательного типа, содержащее регистры множителя, множимого и произведения, одноразрядный сумматор последовательного действия, блок управления, логические элементы И, (1 ).

Однако принцип работы такого уст- ройства не позволяет использовать в нем динамические регистры с большой степенью интеграции, что ограничивает область.его применения.

Известно также последовательное множительное устройство с умножени- ем на k разрядов множителя, содержа- . щее динамические регистры множимого, . частных произведений;,: k.ïîñëåäoâà-

:тельных сумматоров (2 4% <. n ., где.

n — разрядность сомножителей ),.k-элементов И (2 g.

Недостатки известного устройства заключаются в невозможности реализации в нем динамического принципа работы, что сужает область его применения, и сложности устройства.

Наиболее близким к предлагаемому является последовательное множительное устройство с умножением на % разрядов множителя (3), содержащее динамические регистры множимого, частичных произведений, k последовательных сумматоров (2 <к и, где л — разрядность сомножителей), k элементов

И, причем выходы элементов И соответственно подключены к первым входам последовательных сумматоров, динамический регистр множителя, (k+1) элемент И, два элемента запрета, элемент ИЛИ, причем второй. вход первого последовательного сумматора сое динен..с выходом первого элемента запрета,. выход каждого последовательного сумматора соединен с вторым входом следующего последовательного сумматора, выход k-ro последовательного сумматора соединен с .входом динамического регистра частичных произведений, выход. которого подключен к первому входу (k+1)-ro элемента И, а

25 также к прямому входу первого элемента запрета, вход динамического регистра множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход вто30 poro элемента запрета подключен к

9< 7620 второму входу (к+1)-го элемента и и к инверсному входу первого элемента запрета, а также к перной управляющей тактовой шине устройства, выходы (k+1)-го элемента И и второго элемен-, та запрета соединены со нходами элемента ИЛИ (3 .

К недостаткам этого устройства относятся большие аппаратурные затраты и большое число внешних связей, Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройство, содержащее динамические регистры множимого, множителя и частичных произведений, последовательных сумматоров (2 - 1«п, где n — разрядность сомножителей ), дна элемента запрета, элемент. ИЛИ, (к+1) элементов И,причем выходы элементов И с первого по )<-й подключены к первым входам соответствующих последовательных сумматоров, динамический регистр множителя, второй вход первого последо- вательного сумматора соединен с выходом перного элемента запрета, выход каждого последовательного сумматора соединен с вторым входом последующего последовательного сумматора, выход 1<-ro последовательного сумматора соединен с входом динамического ЗО регистра частичных произведений, выход которого подключен к первому входу (к+1) -го элемента И, а также к прямому входу первого элемента за-. прета, вход динамического регистра 35 множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход второго элемента запрета подключен к второму нходу (f<+1)-го элемента И,.к инверс- 4() ному входу первого элемента запрета и к первой управляющей. тактовой шине устройства, выходы (%+1)-го элемента И и второго элемента запрета соединены с входами элемента ИЛИ, ! введены статический вспомогательный регистр, входы к-х разрядов которого подключены к выходам соответствующих разрядов динамического регистра . множителя, выход пеРвого Разряда динамического регистра множителя подключен к прямому входу второго элемента запрета, выход элемента ИЛИ соединен с входом динамического реги стра множителя, выходы разрядов статического вспомогательного регистра соединены с первыми входами элементов И с первого no f<-й, выходы разрядов динамического регистра множимого с (n+f<)-ro по (n+2)-й соединены соответственно с вторыми входами эле--Я) ментов И с второго по 1<-й, управляющий вход статического вспомогательного регистра подключен к второй. управляющей тактовой шине устройства, 65.

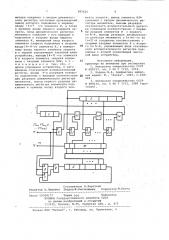

На чертеже представлена функциональная схема последовательного мно,жительного устройства.

Устройство содержит. % последовательных сумматоров 1.1; 1 .2;...,1.%

k элементов И 2.1; 2. 2;...,2.%,(п+*) вЂ, разрядный динамический регистр 3 множимого (и — разрядность сомножителей), и-разрядный динамический регистр 4 частичных произведений, празрядный динамический регистр 5 множителя, элемент 6 запрета, элемент

7 запрета,элементИ 8,элемент ИЛИ 9

;k-разрядный статический регистр

IO„ первую управляющую тактовую шину

11 и вторую управляющую тактовую шину 12.. Выходы элементов И 2,1; 2.2g...

2, f< первым входам последовательных суммато,ров 1.1; 1.2;...1.%. Второй вход первого последовательного сумматора

1.1 соединен с выходом элемента 6 запрета, выход каждого последовательного сумматора соединен с вторым входом следующего последовательного сумматора. Выход f<-ro последовательного сумматора 1.% соединен с входом динамического регистра 4 частичных произведений, выход которого подключен к первому входу элемента И 8, а также к прямому входу элемента 6 запрета. Вход динамического регистра 3 множимого соединен с его выходом и с вторым входом элемента И 2.1. Инверсный вход элемента 7 запрета подключен к второму входу элемента И 8 и к инверсному входу элемента 6 запрета, а также к управляющей тактовой шине 11. Выходы элемента И 8 и эле-мента 7 запрета соединены с входами элемента ИЛИ 9.f< информационных .входов статического вспомогательного регистра 10 подключены к соответствующим выходам к разрядов динамического регистра 5 множителя, à (f<+1) — и выход динамического регистра 5 множителя подключен к прямому входу элемента 7 запрета, Выход элемента ИЛИ 9 связан с входом динамического регистра 5 множителя.й выходов статического вспомогательного регистра 10 связаны соответственно с первыми входами элементов И 2.1; 2.2;...;2.f<.

Выходы разрядов с (и+%)-го по (n+2)-й включительно динамического регистра

3 множимого связаны соответственно с вторыми входами элементов И 2.2, 2.3;...2.f<.

Управляющий вход статического вспомогательного регистра 10 подсоединен к управляющей тактовой шине 12.

Устройство работает по циклам.

Длительность каждого цикла равна (n+f<) тактам, так как при умножении п-разрядного множимого на к очередных. цифр множителя получается частичное произведение, имеющее разрядность (n+f<), а для получения одной

987620 6 цифры частичного произведения нужен один такт.

Считаем, что, когда на выходах первых разрядов динамических регистров в режиме хранения находятся первые разряды записанных в.них чисел, на управляющей тактовой шине 12 появляется сигнал "1", соответствующий началу цикла.

В исходном состоянии (такт Т1 первого цикла) в и первых разрядах регистра 3 находится множимое, а в регистре 5 — множитель. В регистре 10 записаны младшие fc цифр множителя. В остальных разрядах регистра 3 и в регистре 4 записаны нули. !5

Рассмотрим цикл работы устройства. В такте Т1 каждого цикла в регистр 10 записываются % очередных разрядов множителя, на,которых в данном цикле будет производиться умно жение. Цикл циркуляции динамических регистров 5 и 4 меньше длительности циклов циркуляции всего устройства, равной. (n+k) тактов, и обеспечивает в каждом цикле. сдвиг содержимого регистров 5 и 4 на Й разрядов вправо.

Цикл циркуляции регистра 3 равен циклу циркуляции устройства.

На сумматоре 1.1 в каждом цикле осуществляется сложение сформированной в предыдущих циклах и сдвинутой на к разрядов вправо суммы частичных произведений и кода множимого, умно„женного на младший из k очередных разрядов множителя. На сумматоре 35

1.2 осуществляется сложение сформированного на выходе сумматора 1.1 числа и сдвинутого на один разряд влево множимого,умноженногона вторую цифру группы разрядов множителя. Аналогичным образом осуществляется сложение на остальных сумматорах,Сдвиги множимого влево обеспечиваются выдачей задержанного кода множимого с соответствующего выхода регистра

3 и подачей его на выходы сумматоров 1.2,...1.%.

Управление подачей кода множимого на входы сумматоров 1.1;...1.к через элементы И 2.1;...2.tc (умножение на цифру множителя) осуществляется разрядами с первого по к-й регистра 10, На выходе сумматора 1.% за (n+х) тактов формируется очередная сумма частичных произведений, при.чем в первых к тактах определяются

% очередных (начиная с младших) цифр произведения. В последниХ тактах формируется текущая ta --разрядная сумма частичных произведений. к концу такта предыдущая сумма 6ы частичных произведений полностью выдвинется из регистра 4, а в его tc младших разрядах будет находиться к очередных цифр произведения. Поэтому, начиная с такта Т„ „ -rо, по сиг- 65 налу на управляющей .тактовой шине

11 выдача кода из регистра 4 на сумматор 1.1 через элемент 6 запрета блокчруется, разрывается цепь циркуляции регистра 5 с выхода первого разряда и открывается цепь циркуляции регистра 5 через элемент И 8 и . в течение тактов Т„+1,...,Т„+» в регистр 5 принимаются к очередных разрядов произведения.

После последнего(п+»)-го такта каждого цикла состояние регистров устройства следующее. Регистр 3 мно- жимого находится в исходном состоянии. В регистре 4 находятся и старших разрядов очередного частичного произведения. В старших (i-i)"к разрядах регистра 5 находятся полученные (где 1 в номер цикла) младшие разряды произведения, а в младших и †(1 -1) tc разрядах регистра 5 — те цифры множителя, котбрые еще не принимают участия в умножении. В регистре 10 находятся k очередных цифр множителя,После последнего такта последнего цикла в регистре 5 находятся старшие цифры произведения, а в регистре 5 — младшие .разряды произведения.

По сравнению с известным устройством, содержащим два (n+ic) -разрядных регистра, один и -разрядный регистр и.один (к-1)-разрядный регистр, предлагаемое устройство содержит один (n+k)-разрядный регистр, два п -разрядных регистра. Если считать, что затраты на реализацию k триггеров в известном устройстве и (c-разрядного статического регистра в предлагаемом одинаковы,.то выигрыш в оборудовании в предлагаемом устройстве составит (2 k-1) разрядов. упрощение предлагаемого устройства достигается тем, что в известном устройстве число внешних связей равно (1+1), в предлагаемом 2.

Формула изобретения

Последовательно множительное устройство, содержащее динамические регистры множимого, множителя и частичных произведений, % последовательных сумматоров (2 < М «

Составитель B.Áåðåýêèí

Редактор А.Лежнина Техред Ж.Кастелевич . Корректор М.Коста

Эаказ 10304/37 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 матора соединен с входом динамического регистра частичных произведений, выход которого подключен к первому входу (4 4) -го элемента И, а также к прямому входу первого элемента запрета, вход динамического регистра множимого соединен с его выходом и подключен к второму входу первого элемента И, инверсный вход второго элемента запрета подключен к второму входу (%+ )-ro элемента И, к инверсному входу первого элемента запрета и к первой управляющей тактовой шине устройства, выходы (1+4) -го элемента

И и второго элемента запрета-соединены с входами Элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены статический вспомогательный регистр, входы Й-х разрядов которого подключены к выходам соответствующих разрядов динамического регистра множителя, выход первого разряда динамического регистра множителя подключен к прямому входу второго элемента запрета, выход элемента ИЛИ соединен с входом динамического регистра множителя, выходы разрядов статического вспомогательного регистра соединены соответственно с первыми входами элементов И с первого по k-й, выходы разрядов динамического регистра множимого c (n +k) -го по (n+2) é соединены соответственно с вторыми входами элементов И с второ10 го по k-й, управляющий вход статического вспомогательного регистра подключен к второй управляющей трактовой .шине устройства.

15 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 608157, кл, С 06 F 7/52., 1974.

2. Карцев N.À. Арифметика цифро7О вых машин. М,, 1969, с.458464.

3. Авторское свидетельство СССР

9 888110, K . G 06 F 7/52, 1980 (прототип).