Устройство для вычисления корней приведенного квадратного уравнения

Иллюстрации

Показать всеРеферат

О ll И С А H И Е ()987635

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. спид-ву (5!)М. Кл. (22) Заявлено 12.0980 (21) 2982461/18 — 24

G 0B G 7/36 с присоединением заявки М

3Ьоуйоротоеей комитвт

СССР

lo аолом изобретений и открытий (23) Приоритет

Опубликовано 07.01.83. Бюллетень М 1

Дата опубликования описанмя 07.01. 83 (53) УДК 681.3 (088.8) (72) Авторы изобретения

А. Ф. Гришков, И. Г. Дорух и А. В. Маргелов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРНЕЙ ПРИВЕДЕННОГО

КВАДРАТНОГО УРАВНЕНИЯ

Изобретение относится к электрическим вычислительным устройствам и может быть использовано B аналоговых вычислительных машинах.

Известно устройство для вычисления корней приведенного квадратного уравнения содержащее операционные усилители, сумматор, . функциональные потенциометры (11 ..

Недостатком известного устройства является значительная инерционность.

Наиболее близким к предлагаемому является устройство для вычисления корней приведенного квадратного уравнения, содержащее согласующие усилители, квадраторы, сумматоры (21

Это устройство характеризуется сравнительно невысоким быстродействием.

Цель изобретения — повышение быстродействия.

Указанная цель достигается тем, что устройство для вычисления корней приведенного квадратного уравнения, содержащем соединенные последовательно первый согласующий усилитель и первый квадратор, соединенные пос2 ледовательно второй согласующий усилитель и второй квадратор, входы первого .и второго согласующих усилителей являются соответственно первым и вторым входами устройства, первый сумматор, выход которого подключен к входу третьего квадратора, второй сумматор, выходы первого и второго согласующих усилителей соединены соответственно с первым и вторым входами первого сумматора, выходы первого, второго н третьего квадраторов подключены соответственно к первому, второму и третьему входам второго сумматора, четвертый вход второго сумматора соединен с его выходом, выход второго сумматора является выходом устройства и подключен к третьему входу первого сумматора.

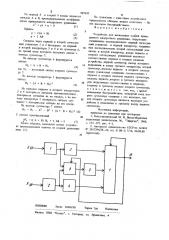

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит первый и второй согласующие усилители 1 и 2, первый, второй и третий квадраторы 3, 4 и 5, первый и второй сумматоры 6 и 7, первый 8 и второй 9 входы устройства и его выход 10.

Устройство работает следующим образом.

Причем р=2(А+ В) р=2АВ

Р) (3) С учетом преобразований

ВНИИПИ Заказ 10306/38 Тираж 704 Подписное

Филиал ППП "Патент", r. Ужтород, ул. Проектная, 4

3 987635

На первый 8 и второй 9 входы подаются сигналы А и В, пропорциональные коэффициентам приведенного квадратного уравнения х- +px+q =0 (1) Сигналы через первый и второй согласующие усилители 1 и 2 поступают на.дервый и второй квадраторы 3 и 4 и на сумматор 6, на третий вход которого поступает сигнал с выхода сумматора 7.

На выходе сумматора 6 формируется сигнал

И =А+В+И„ (4) где И, — выходной сигнал второго сумматора 7„

На выходе квадратора 5 формируется сигнал 2О

И, =(А+В+И,) (5) На выходах первого и второго квадраторов

3 и 4 полярность сигналов противоположная полярности сигналов на их входах, а на вы25 ходе квадратора 5 полярность сигнала совпадает с полярностью сигнала на его входе.

На выходе сумматора 7 ийеем

И =И, — А — В + (А+ В+Из) (6) И, < 2(А + В) И + 2 АВ = 0 (7)

Таким образом, выходной сигнал устройства пропорционален одному из корней уравнения вида (1).

По сравнению с известным устройством предлагаемое обладает новым качеством — бо лее высоким быстродействием.

Формула изобретения

Устройство для вычисления корйей приведенного квадратного уравнения, содержащее соединенные последовательно первый согласующий усилитель и первый квадратор, соединенные последовательно второй согласующий усилитель и второй квадратор, входы первого и второго согласующих усилителей являются соответственно первым и вторым входами устройства, первый сумматор, выход которого подключен к входу третьего квадратора, второй сумматор, .выходы первого и второго согласующих усилителей соединены соответственно с первым и вторым входами первого сумматора, выходы первого, второго и третьего квадраторов подключены соответственно к первому, второму и третьему входам второго сумматора, о т л и ч а ю щ е е с я тем, что, с -целью повышения быстродействия, четвертый вход второго сумматора соединен с его выходом, выход второго сумматора является выходом устройства и подключен к третьему входу первого сумматора.

Источники информации, принятые во внимание при экспертизе

1. Константиновский М. И. Малогабаритные аналоговые вычислители. М., "Энергия", 1966, с. 122 — 127, рис. 4 — 1.

2. Авторское свидетельство СССРпо заявке

Я 2967294/18 — 24, кл. G 06 G 7/16, 04.08;80 (прототип) .