Регенератор цифрового сигнала

Иллюстрации

Показать всеРеферат

Сбюз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ н1987838 (61) Дополнительное к авт. свид-ву— (22) Заявлено 29.07. 81 (21) 3328091/18-09

И11М. Ки.

И 04 L, 25/00 с присоединением заявки М

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 070 183. Бюллетень N9 1

Дата опубликования описания 070183 (53) УДК 621. 395. . 387(088. 8) A.Þ. Лев, Д.A. Сирбиладзе и Г.С. Иаркарян

« --».

Одесский электротехнический институт связи им. A.С. Попова

{72) Авторы изобретения (74) Заявитель (54) РЕГЕНЕРАТОР ЦИФРОВОГО СИГНАЛА

Изобретение относится к технике связи, в частности к цифровым системам передачи.

Известно устройство регенерации цифрового сигнала, содержащее последовательно соединенные усилителькорректор, блок вычитания, другой вход. которого соединен с первым входом компаратора и выходом блока ана- 0 лиза и формирования ступенчатого напряжения, первый вход которого соединен с вторым входом компаратора, выходом решающего блока, входом выходного блока, а второй вход блока анализа и формирования ступенчатого напряжения соединен с выходом компаратора, выход блока вычитания соединен с третьим входом компаратора и первым входом решающего блока, второй вход которого соединен с выходом блока синхронизации (1 1.

Известное устройство имеет низкую помехоустойчивость вследствие несовершенства схемы формирования опорного напряжения..

Цель изобретения — повышение поме-. хоустойчивости цифрового сигнала.

Для достижения поставленной цели в регенератор цифрового сигнала, содержащий усилитель-корректор, выход которого подключен к первому входу блока вычитания и к входу блока синхронизации, выход которого соединен с первым входом решающего блока, выход которого соединен с входом входного блока и с первым входом блока анализа и формирования ступенчатого напряжения, выход которого соединен с вторым входом блока вычитания и, с первым входом компаратора, выход которого соединен с вторым входом блока анализа и формирования ступенчатого напряжения, введены пиковый . детектор, линия задержки и дифференцирующая цепь, вход которой подключен к выходу входного блока, а выход соединен с первым входом пикового детектора, второй вход которого соединен с вторым входом решающего блока, который подключен к выходу блока вычитания, выход пикового детектора соединен с вторым входом компарато ра, третий вход которого соединен с выходом линии задержки, вход которой соединен с выходом решающего блока.

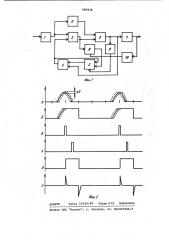

На фиг. 1 приведена структурная электрическая схема регенератора цифровых сигналов; на фиг. 2 диаграммы работы отдельных блоков устройства.

987.838

Регенератор цифрового сигнала содержит усилитель-корректор 1, блок

2 вычитания, компаратор 3, блок 4 анализа и формирования ступенчатого напряжения, решающий блок 5, блок 6 синхронизации, входной блок 7, пиковый детектор, 8, линию 9 задержки, 1дифференцирующую цепь 10.

Устройствб работает следующим образом.

Искаженные линией и помехами импульсы цифрового сигнала с выхода усилителя-корректора 1 со значительным дрожанием фазы поступают на вход блока 6 синхронизации и первый вход блока 2 вычитания. На второй вход ко- 35 торого подается опорное напряжение с выхода блока 4 анализа и формирования ступенчатого напряжения. На фиг. 2а показана одна иэ возможных реализаций цифрового сигнала на выходе пикового детектора 8, где пунктиром показаны пределы, в которых могут находиться фронты неизменных по амплитуде цифровых сигналов вследствие фа- зовых искажений, д 0 — предел изменения напряжения на информационном 25 входе компаратора 3 в регенераторе прототипа в момент стробирования.

На фиг. 2 б показан сигнал на выходе пикового детектора 8, где заштрихованная область означает пределы 30 смещения фронта входного цифрового сигнала вследствие дрожания фазы.

Сигнал с выхода пикового детектора 8 поступает на второй вход компаратора 3, на первый вход которого 35 поступает опорное напряжение с выхода блока 4 анализа и формирования ступенчатого напряжения. На третий вход компаратора 3 поступает импульс стробирования с выхода линии 9 задерж40 ки, задержанный примерно на четверть тактового интервала (фиг. 2г) по сравнению с импульсами на выходе ре-. шающего блока 5 (фиг. 2в ), которые формируются при одновременном воздействии импульса с выхода блока

2 вычитания на второй вход решающего блока 5, на первый вход которого воздействует импульс с выхода блока б синхронизации. 1<омпаратор 3 имеет большое входное сопротивление и поэтому на выходе пикового детектора

8 сохраняются амплитудные значения поступивших на его вход импульсов после их прекращения (фиг. 2б ) доо момента действия на первый вход пикового детектора 8 импульса, который каждый раз приводит его в исходное состояние, поступающего с выхода дифференцирующей цепи 10 (фиг. 2е ), на вход которой поступает. импульс щ с выхода входного блока 7 (фиг. 2д ).

Таким образом, на выходе пикового детектора 8 запоминаются истинные значения амплитуды импульсов и эти значения сравниваются с опорным напряжением в момент стробирования компаратора 3 импульсами с выхода линии

9 задержки, при этом на выходе ком паратора формируется более точное решение об изменении амплитуды входного сигнала регенератора, так как дрожание фазы у входных импульсов уже не будет вызывать изменения напряжения на информационном. входе компаратора 3 в момент стробирования при неизменной амплитуде входных импульсов, что приводит к увеличению точности формирования опорного на)пряжения и,,как следствие, к повышению помехоустойчивости регенератора цифрового сигнала.

Использование изобретения позволяет за счет уменьшения влияния дрожания фазы информационных импульсов, достигаемого предварительным запоминанием амплитудных значений информационных импульсов для дальнейшего иХ анализа повысить помехоустойчивость регенератора.

Формула изобретения

Регенератор цифрового сигнала, содержащий усилитель-корректор, выход которого подключен к первому входу блока вычитания и к входу блока синхронизации, выход которого соединен с первым входом решающего блока, выход которого соединен с входом входного блока и с первым входом блока анализа и формирования ступенчатого напряжения, выход которого соединен с вторым входом блока вычитания и с первым входом компаратора, выход которого соединен с вторым входом блока анализа и формирования ступенчатого напряжения, о т л и ч а ю— шийся тем, что, с целью повышения помехоустойчивости, в него введены пиковый детектор, линия задержки и дифференцирующая цепь, вход которой подключен к выходу входного блока, а выход соединен с первым входом пикового детектора, второй вход которого соединен с вторым входом решающего блока, который подключен к выходу блока вычитания, выход пикового детектора соединен с вторым входом компаратора, третий вход которого соединен с выходом линии задержки, вход которой соединен с выходом решающего блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке Р 2964479/09, кл ° Н 04 L 25/06, 1980.

987838

Фюв l

ВНИИПИ Заказ 10329/48 тираж б Т5 Подписное

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4