Устройство для ввода информации

Иллюстрации

Показать всеРеферат

иА. М. изобретения (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ BBOLIA ИНФОРМАБИИ

Изобретение относится к вычислительной технике и. может быть использовано для обработки цифровой информации, записанной на магнитной ленте и других носителях информации, а также для устройства обработки информации при рабо5 те в реальном времени.

Известно устройство для вжща информации, содержащее блок совпадения, блок формирования тактовых импульсов, регистр строки, дешифратор четности, блок контроля, блок перезаписи информации и блок связи. В данном устройстве информация считывается с магнитной ленты и вводится в ЭВМ. построчно Р 1) .

Однако данное устройство характеризуется недостаточно эффективным исполь зованием процессора ЭВМ из-за загрузки его в течение всего време и -считывания информациие го

Наиболее близким к изобретению является устройство для. ввода информации, содержащее входной регистр, буферный блок памяти, вычислительный блок, два

Ф

1 с

2 счетчика, элементы И и ИЛИ, два дещифpampa и блок местного управления, состоящий из блоков местного управления записи и считывания, схемы пуска и останова P2) .

Недостатком данного устройства является то, что ввод информации из буферного бпока памяти начинается лишь после того, как заполнена его половина, что очень неэффективно при работе в реальном времени, так как при этом сокра щается время обработки и затрудняется реализация программ реального времени.

Целью. изобретения является увеличение быстродействия устройства..

Поставленная цель достигается тем, что в устройство, содержащее регистр, вход которого является первым входом устройства, выход регистра соединен с первым входом блока памяти, выход которого является выходом устройства, блок управления, первый и второй входы кото рого соединены соответственно с входами первого и второго счетчиков и с первь1ми

3 9895 входами первого и второго элементов И, вторые входы которых соединены с первыми входами первого и второго счетчиков, выходы первого и второго элементов,И соединены с входами первого элемента

ИЛИ, выход которого соединен с вторым входом блока памяти, третий и четвертый входы которого соединены с входами блока управления, введены второй элемент ИЛИ, первый, второй, третий, чеч 16 вертый и пятый триггеры, третий, четвертый и пятый элементы И и блок сравнения, входы которого соединены с первыми выходами первого и второго счет-! чиков, вторые выходы которых соединены с входами третьего триггера, первый выход которого. соединен с первым входом пятого элемента И, второй. вход которого соединен с выходом блока сравнения, выход пятого элемента И соединен

26 с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым выходом третьего триггера, третий и четвертый входы блока памяти соедине25 ны с первыми входами четвертого и пя-. того триггеров и с первыми входами первого и второго триггеров, вторые входы которых являются соответственно вторым и третьим входами устройства, выходы первого и второго триггеров соединены с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с первыми выходами пятого и четвертого триггеров, вторые выходы которых сое- З5 динены соответственно с входами второго и первого счетчиков, выход второго эле» мента ИЛИ соединен с третьим входом четвертого элемента И, выход которого соединен с вторым входом пятого триг - © гера, выход третьего элемента И соединен с вторым входом четвертого триггеpG

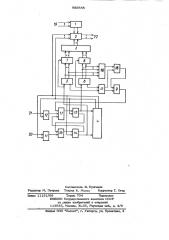

На чертеже представлена функШюнальная схема устройства. 45

Устройство содержит регистр 1, блок памяти 2, первый элемент ИЛИ 3, блок управления 4, первый и второй счетчики 5 и 6, первый и второй элементы И 7 и 8, второй элемент ИЛИ 9, блок сравне-50 ния 10, первый, второй, третий, четвертый и пятый триггеры 11, 12, 13, 14 и 15, третий, четвертый и пятый элементы И 16, 17 и 18, входные шины 19, первую управляюшую шину 20, вторую 55 управляюшую шину 21, выходную шину 22.

Устройство работает следуюшим образом.

Входная информация поступает по umнам 19, записывается в регистр 1 и хранится в нем до окончания записи ее в блок памяти 2. Одновременно импуль сом сопровождения информационного слова по первой управляюшей шине 20 триго

rep 11 устанавливается в «1», сигнал с выхода первого триггера 11 проходит через третий элемент И 16 и устанавливает четвертый триггер 14 в "1 .

Сигналом с инверсного выходе четвертого триггера 14 закрывается четвертый элемент И 17 и открывается первый элемент И 7, а выходы первого счетчика 5 через первый элеменг И 7 и первый элемент ИЛИ 3 подключается к адресным входам блока памяти 2. Одновременно по сигналу с выхода четвертого триггера 14 в блоке управления 4 формируются импульсы, которыми производится запись в блок памяти 2. После записи каждого информационного слова первый и четвертъй триггеры 11 и 14 устанавливаются в О, а показания первого счетчика 5 увеличиваются на единицу. При переполнении первого счетчика

5 третий триггер 13 устанавливается в

1 . Считывание из блока памяти 2 производится по импульсу запроса информации, который поступает по второй управляюшей шине 21 и устанавливает второй триггер 12 в «1». Если в блоке памяти

2 имеется несчитанная информация и в этот момент не ведется запись, то пятый триггер 15 устанавливается в»1", если же запись ведется, то пятый триггер 15 устанавливается в «1» только после окончания записи, когда четвертый триг гер 14 устайавливается в 0 и с его выхода на вход четвертого элемента

И 17 поступает разрешаюший сигнал.

Сигналом с выхода пятого триггера 15 закрывается третий элемент И 16, тем самым запрешается формирование сигналов записи во время считывания Одновременно открывается второй элемент

И 8 и выходы второго счетчика 6 через второй элемент И 8 и через первый элемент ИЛИ 3 подключаются к адресным входам блока памяти 2. В блоке управления 4 формируются сигналы, необходимые для считывания информации из блока памяти, и считанное информационное слово поступает на выходную шину 22. После счигывания каждого слова второй и пятый триггеры 12 и 15 ус ся в О, а второй счетчик 6 изменяет свои показании на 1 . При переполнении

5 0805 второго счетчика 6 третий триггер 13 и второй счетчик 6.устанавливается в

"О». Контроль наличия несчитанной информации производимся при помощи схемы, состоящей из третьего триггера 13, блока сравнения 10, пятого элемента

И 18 и второго элемента HIIH 9. Сигнал разрешения считывания формируется в следующих случаях: при неполном заполнении блока памя- 16 ти 2 в случае, когда показаний первого счетчика 5 больше показания второго счетчика 6, сигнал.с блока сравнения

10 открывает пятый элемент И 18 и сигнал разрешения считывания с ее выхода проходит через второй элемент

ИЛИ 9 на вход четвертого элемента

И 17; после переполнения первого счетчика

5 сигнал, разрешающий считывание, с выхода третьего триггера 13 проходит через второй элемент ИЛИ 9 на вход четвертого элемента И 17.

Изобретение позволяет повысить бы стродействие устройства в 1,5 раза и исключить задержку начала обработки информации на ЭВМ за счет того, что считывание информашж может производиться сразу после начала поступления информации на устройство, что особенно важно нри обработке информации на ЭВМв реальном времени. Предлагаемое устройство целесообразно использовать для ввода информнции тогда, когда среднее время обработки массива информации И меньше времени ввода массива.

Формула.изо бретения

46 стройство для ввода информашхи содержащее регистр, вход которого является первым входом устройства, выход регистра соединен с первым входом блока памяти, выход которого является вы- 43 ходом устройства, блок управления, нервый и второй входы которого соединены соответственно с входами первого и второго счетчиков и с первыми входами первого. и второго элементов И, вторые зф входы кэмрых соединены с первыми выходами первого и второго счетчиков, выходы первого и второго элементов И соединены с входами первого. элемента

ИЛИ, выход которого соединен с вторым входом блока памяти, третий и четвертый входы которого соединены с выходами блока управления, о т л и ч а ющ е е с s тем, что, с целью увеличения быстродействия устройства, s него введены второй элемент ИЛИ, первый, второй, третий, четвертый и пятый триггеры, третий, четвертый и шпгый элема ты И и блок сравнения, входы которого соединены с первыми выходами первого и второго счетчиков, вторые выходы которых соединены с входами третьего триггера, первый выход которого соединен с нервым входом пятого элемента И, второй вход которого соединен с выходом блока сравнения, выход питого элемента И соединен с первым входом второго эле мента ИЛИ, второй вход которого соединен с вторым выходом третьего триггера, третий и четвертый входы блока памяти соединены с первыми входами четвертого и пятого триггеров и с первыми входами первого и второго триггеров, вторые входы которых являются соответственно вторым и третьим входами устройства, выходы первого и второго триг геров соединены с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соот ветственно с первыми выходами пятого и четвертого триггеров, вторые выходы которых соединены соответственно с входами второго и первого счетчиков, выход второго элемента ИЛИ соединен с третьим входом четвертого элемента

И, выход которого соединен с вторым входом пятого триггера, выход третьего элемента И соединнн с вторым входом четвертого триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

K 369562в zn. 606 F 3/04т 1970.

2. Авторское свидетельство СССР

34 378832, ют. 606F 3/04, 1970 (прототип).

21

Составитель В. Булганин

Редактор М, Петрова Техред К. Иыцьо Корректор Г. Огар

Заказ 11131/68 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35, Раушская наб., д. 4/5 филиал ППП Патент, г. Ужгород, ул. Проектная, 4