Вычислительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (п)989556

Союз Советских

Социалистических

Республик (6! ) Дополнительное к авт. саид-ву (22) Заявлено 04.09.80 {21) 2999S52/18-24 с присоединением заявки № (23) П риоритет

Опубликовано 15.01.83. Бюллетень № 2 (51)М. Кл.

G06F 7/52

Гевударствееый кеттктет

СССР тЮ лехам изобретений и открытий (5Ç) УДК681, ° 325 (088.8) Дата опубликования описания 15.01.83 (72) Авторы изобретения

1 .А. И. Стасюк, Ф. E.. Лисник и А. И. Гузенко :

6 .

В

Киевский ордена Трудового Красного Знамени ийститут-инженеров гражданской авиации (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к пнфровой вычислительной технике и может быть применено в составе универсальных или специализированных вычислительных машин для оперативного вычисления арифметических операций умножения и деления.

Известны устройства для выполнения .арифметических операштй умножения и деления, включающие матрицу И-ти од1О норазрядных сумматоров, rn цифровых функциональных преобразователей, Иразрядный регистр (11 и (2) .

Однако в этих устройствах не выполняется одновременно операция умножения и деления и, соответственно, не осушеств. ляется контроль вычислительного процес са - умножения делением и наоборот, в связи с чем в устройствах ограничены функциональные возможности и точность щ вычислений.

Наиболее близким к предлагаемому является вычислительное устройство, содержащее блок умножения, выиитатель, 2 узел определения знака частного, входные шины и выходную шину, причем группа выходов вычитателя, соответствующие входы которого соединены с выходами блока умножения, подключена к выходной шине устройства $3) .

Недостатками известного устройства являются ограниченные функциональные возможности и невысокая точность из- за того, что в нем не организован контроль вычислительного процесса.

Бель изобретения - расширение функе циональных воэможностей эа счет выполнения как операции деления, так и операции умножения и повышение точности за счет осуществления параллелт ного контроля вычисления.

Указанная цель достигается тем, что

s вычислительное устройство, содержащее блок умножения и вычитатель, выходы которого соединены с первой группой выходов результата устройства, дополнительно введено два коммутатора, две схемы сравнения, первый. второй и.тпетий сдвигатели и узел приоритета,. причем входы первого операнда устройства соединены с первой группой входов первой схемы сравнения и первой группой информапионньи входов первого коммутатора, вторая группа информационных входов которого соединена с второй группой входов первой схемы сравнения и выходами вычитателя, входы второго операнда устройства соединены с входами 1и узла приоритета и информационными входами первого сдвигателя, управляющие входы которого подключены к выходам узла приоритета, выходы первого сдвига-, теля соединены с первой группой входов блока умножения, вторая группа входов которого соединена с выходами первого коммутатора, вьиоды результата умножения блока умножения соединены с информационными входами второго сдвигателя, первой группой входов второй схемы сравнения и первой группой информационных входов второго коммутатора, вторая группа информационных входов которого соединена с второй группой входов второй схемы сравнения, и выходами третьего сдвигателя, информационные входы которого соединены с входами третьего операнда устройства, управляющие входы второго и третьего сдвигателей соединены с выходами узла приоритета, вьиоды второго коммутатора соединены с первой группой входов вычитателя, вторая группа входов которого соединена- с вьиодами промежуточной суммы частичных произведений блока умножения, управляющие

3$ входы первого н второго коммутаторов соединены с управииюпщм входом устройства, выходы второго сдвигателя соединены со второй группой выходов результата устройства, выходы первой и второй ао схем сравнения соединены с вьиодами контроля устройства.

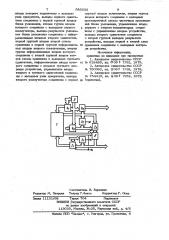

На чертеже представлена схема предлагаемого устройства.

Устройство содержит блок умножения

1, два коммутатора 2„и 2, две схе мы сравнения З„и З, первый, второй и третий сдвигатели 4, 4 и 4>, узел приоритета 5 и вычитатель 6. Входы первого операнда устройства соединены с первой группой входов первой схемы сравнения Ç„и первой группой информаmo bK дов пер K0 ampa 2 вторая группа информационньи входов которого соединена со второй группой входов первой схемы сравнения 3 и выходаыи вычитателя 6. Входы второго операнда устройства соединены со входами узла приоритета 5 и информационнымм входами первого сдвигателя 4, управляющие входы которого подключены к вьиодам узла приоритета 5. Выходы пер. вого сдвигателя 4„соединены с первой группой входов бпока умножении 1, втоpas группа входов которого соединена с выходами первого коммутатора 2 . Выходы результата умножения блока умножения 1 соединены с информационными входами второго сдвигателя 4, первой группой входов второй схемы сравнении

3 и первой группой информационных вхо. дов второго коммутатора 2, вторая группа информационньи входов которого соединена со второй группой входов второй схемы сравнения З и вьиодами третьего сдвигателя 4, информационные ,входы которого соединены со входами третьего операнда устройства. Управляющие входы второго и третьего сдвигателей 4 и 4 соединены с выходами узла приорйтета 5, вьиоды второго коммутатора

2 соединены с первой группой входов вычитателя 6, вторая группа входов которого соединена с выходами промежуточной суммы частичных произведений блока умно. жения 1. Управляющие входы первого и второго коммутаторов 2, и 2 < соединены с управляющим входом устройства. Выходи второго сдвигателя 4 соединены со втсь- . рой группой выходов результата устройсьва. Выходы первой и второй схем сравнения З„и 3 соединены с вьиодами контpoas устройства, а выходы вычитателя 6 подключены к первой группе выходов результата устройства.

Oaepamm умножения Q Х. = Ъ для случая, когда младший разряд 5 вектора

6 1, может быть записана

Ь=.Х 50 Х или соответственно j p )(" > и- Е=и-i-

О и-М (,Р (Z) =-" и-1 и-1+Р ) = + а-х " (q) где 4 =0,4> ", и-1 :--.

Операция деления в соответствии с (3)

Ич Ь-j Ь1И.Р М+Р

Х=Ь вЂ” KoX . () е=

Qns случая, когда один или младших

Ф . разрядов вектора О равны нулю, тогда выражения (2)-(4) могут быть записаны

И- - и Е=м-е-1 „.,„„.

Ъ = r. а "х, (5) . Ы4ю „,, Е=" И-Е- „° »Р

Ь=a x+a.с х (6) 48М56, 6 рандов на выходе первого сдвигателя образуется вектор 5, сдвинутый в сторону младших разрядов на число щ, равное количеству нулей в младших -paapsggtx едуц вектора. На выходе третьего сдвигателя

4g образуется вектор 2 g, сдвищр йй, реходпого процесса в устройстве на выходе вычитателя 6 по выражению (7) o образуется значение искомого вектора Х, а на выходе результата умножения блока умножения 1 - соответственно вектор

, поступающий на первую группу че„входов второй схемы сравнения 3, ка вторую группу входов которой поступает значение вектора 2:+ ® со -.входа третьего операнда, Если операхкя деления выпол сдвиг нека правильцо, то на выходе второй схемы сравнения появляется сигнал, характе» 1 теризуюпжй правильность ее выполнения ! рших и конец переходного процесса в устройстве.

Таким образом," в устройстве реализует. оде ся парраллельный контроль вычислитель ного процесса и фиксация момента окончания переходного процесса при умно1 суточ- жении всевозможных чисел и делении оот- для класса чисел, делящихся без остаъ ка, при цифровой точности получаемого результата, что в совокупности расширяет функциональные возможности устройства и. повышает его точность.

Вычислительное устройство, содержащее блок умножения и вычитатель, выходы которого осоединены с первой группой: выходов результата устройства, о т л и ч а ю ш е е с я тем, что, с целью расширения фунпшкональных возможностей за счет выполнения как оцерации деления, так к операции умножения и повышения точности за счет осуществления параллельного контроля вычисления, ус ьройства содержит два коммутатора, две схемы сравнения, первьш, второй и треmR сдвигатели и узел приоритета, причем входы первого - операнда устройства соединены с первой группой входов пер вой схемы сравнения и первой группой информацконных входов первого коммутатора, вторая группа информационных входов которого соединена с второй группой входов первой схемы сравнения и вы ходамк вычитателя, входы второго операнда устройства соединены с входами, узла приоритета и информационными вхо дами первого сдвигателя, управляюшие

5 и операция деления соответственно - -1-в С= ng-w n-1-(Х =Ь X. 0 1(. (7 а=

Работа устройства происходит сл шкм образом.

Операция умножения. На вход устройства подае,вся значение «0», при -этом вход первого операнда подкл чается к второй группе входов биока умножения 3. и запрещается подключенк входов третьего операнда устройства к выходу коммутатора 2 . При подаче на входы первого и второго операндов зна кий «(и 5 соответственно в узле приор тета определяется количество ненулев младших разрядов 6, благодаря чему в первом сдвигателе 4, реализуется вектора а на число нулевых младших разрядов вектора ee., во .втором сдвига ле реализуется сдвиг в сторону ста а в третьем - в сторону младших разря дов на число vn. После окончания переходного процесса в устройстве йа вых результата умножения блока, умножения

1:по выражерию (5) и (6) образуется вектор 2 "" ф, а на выходе ромеи алых сумм частичйых произведений - с

I : - м

Йетственно значение X.0 к - -«, к

e=1 рое поступает на вторую группу входов ви итателя 6. Вектор 2 g(m - число

«фмщшкх разрядов вектора $ равньк йщщф) через второй коммутатор 2 посту ;4ii первую группу входов вычнтателя

:6, чю выходе которого по выражений (7) З образуется вектор х, поступающий йа вторую группу входов первой схемы срав кения 3 „на первую группу входов которой поступает вектор Х со входа.первого операнда. Если умножение выполне- щ но правильно, на выходе первой схемы сравнения З появляется сигнал, характеризуюшкй конец переходного процесса и правильность вычисления вектора g значение которого образуется на выходе второго сдвигателя 4 (сдвинуть и в сто.рону старших разрядов на число N), Операция деления. На управляющий вход устройства подается значение .«1 .

Деление возможно для класса чисел ® и

Q,. делящихся нацело. При этом группа входов третьего операнда пщрицачается через второй коммутатор к первой группе входов вычктателя 6. Выход вьяитатела

6 через первый коммутатор 2 подклю чается к второй группе входов блока умножения 1.

После подачи значений ф и О соответ ственно на входы третьего, второго one-

Формула изобретения входы которого подключены к выходам узла приоритета, выходь первого сдвигателя соединены с первой группой входов блока умножения, вторая группа входов которого соединена с выходами первого коммутатора, выходы результата умножения блока умножения соединены с информационными входами второго сдвигателя, первой группой входов второй схемы сравнения и первой группой информапнон- to ных входов второго коммутатора, вторая группа информационных входов которого соединена с второй группой входов второй схемы сравнения и выходами третьего сдвигателя, информапионные входы кото- 15 рого соединены с входами третьего операнда устройства, управляющие входы второго и третЬего сдвигателей соединены с выходами узла приоритета, выходы второго коммутатора соединены с первой щ

Ц 8 группой Входов вычитателя Вторая группа входов которого соединена с выходами промежуточной суммы частичных произвед ний блока умножения, управляющие входы ,первого и. второго коммутаторов соедивыходы второго сдвигателя соединены с второй группой выходов результата устройства, выходы первой и второй схем сравнения соедйнены с выходами контрс ля устройства.

Источники информании, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 628489, кл. ОО6 F 7/52, 1979.

2. Авторское свидетельство СССР № 760092, кл, GO6F 7/38, 1978, 3. Авторское свидетельство СССР

¹ 754415, кл. 506F 7/52, 1978 (прототип) . l

Составитель В. Березкин

Редактор М. Петрова Техред Т.Фанта Корректор Г. Огар Заказ 11131/68 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент«, г. Ужгород, ул. Проектная, 4