Устройство для синхронизации цифровых систем управления тиристорными выпрямителями

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (»I989741

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

-Республитт (6l ) Дополнительное к.авт. с вид-ву (22) Заявлено 28.05.81 (2l ) 3293174/24-07 с присоединением заявки М (23) Приоритет

Опубликовано 15.01.83. Бюллетень М 2

Дата опубликования описания 15.01.83 (5!)М. Кл.

Н 02 Р 13/16

Гес дарстаепвй камнтвт

СССР пе Евам нэабретеннй н нтхрмтнй (53) УДК621. .3 16.727 (088.8) В. Ю. Верещагин, В. Л. Грузов и В.<А Ч иидовсктй" »

/ -,, " т((М

; т

Вологодский политехнический институФ-- „

4 (72) Авторы изобретения (7I ) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ЦИФРОВЫХ

СИСТЕМ УПРАВЛЕНИЯ ТИРИСТОРНЫМИ

ВЫПРЯМИТЕЛЯМИ

Изобретение относится к электротехнике, а именно к цифровым системам управления тиристорными выпрямителями, и может быть особенно эффективно в установках с широким диапазоном регу5 лировання углов открытия силовых вентилей.

Известны цифровые устройства управления тиристорными выпрямителями, содержащие устройство синхронизаиии, ге- то нератор тактовых импульсов, счетчик, дешифратор и формирователи импульсов . .L1 ), (2 j, (3 ) и (4 I

В этих устройствах угловой эквивалент тактовых интервалов не зависит от интервалов между импульсами синхрониза таи, что приводит к снижению точности, а при больших углах открытия вентилей может привести и к потере работоспособ- 20 ности всей системы, Так, например, при

«абссапотно" стабильном генераторе так» товых имнульсов с тактовым интервалом о

Э

:соответствующим 1 „при уходе частоты .

2 сети, предусмотренном ГОСТом, ошибка

3 6î

Наиболее близким к предлагаемому по технической сущности является устройство для синхронизации цифровых систем управления тиристорными вьптрямителями, содержащее генератор импульсов, выход которого подключен к одному из входов блока суммирования, выход которого подключен ко входу делителя, фазовый дискриминатор и три выходных триг ð Г53.

Недостатком этого устройства sansется невысокая точность и быстродейст вне. Невысокая точность объясняется тем, что коррекпня происходит один раз за период или полупериод входных импульсов. Это же приводит и к снижению быстродействия, так как большие ошибки корректируются несколько периодов.

Кроме того, включение генератора тактовых импульсов и подача входных сигналов в устройстве происходит автономно, что заранее закладывает фазовую

35 ошибку между фазой напряжения и импульсами синхронизации, т.е. устройство предварительно выбирает ошибку включения.

В устройстве в конце каждого периода частоты образуются "сгустки" импульсов корре кшви.

Целью изобретения является повышение точности синхронизации и быстродействия при коррекции фазовых ошибок импульсов синхронизации в цифровых системах управ-,i 0 ления тиристорными выпрямителями.

Поставленная цель достигается тем что устройство для синхронизации цифровых, систем управления тиристорными выпрями телями, содержашее генератор импуль- сов, вьход которого подключен к одному из входов блока суммирования, выход которого подклпбчен ко входу делителя, фазовый дискриминатор и три выходкых триггера, снабжено формирователем импульсов перехода, сетевого напряжения через ноль, двумя сумматорами с однополярной характеристикой, счетчиком и блоком памяти, причем входы вышеуказанного формирователя предназначены для под- 25

/ ключения питающей трехфазной сети, выходы подключены ко входам первого вышеуказанного сумматора, выход которого подключен к одному из входов фазового дискриминатора, на другой вход фазового ЗО дискриминатора подключен выход второго выше казанного сумматора, тремя своими входами подключенного к выходам счетчика и входам выходных триггеров, выход фазового дискриминатора подключен через блок памяти ко второму входу бпока суммирования, выход делителя подключен к счетному входу фазового дискриминатора и к первому входу счетчика и одновременно является выходом ,40 канала тактовых импульсов устройства, один из выходов вышеуказанного формирователя подключен ко второму входу счетчика.

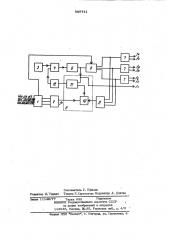

На чертеже приведена схема устрой-.

,45 ства, Устройство содержит формирователь 1, первый сумматор 2, генератор импульсов 3, блок суммирования 4, делитель 5, счетчик 6, выходные триггеры 7, второй сумматор 8, цифровой фазовый дис, криминатор 9, сумматор фазового дискрь минатора 10, реверсивный счетчик фазового дискриминатора ll, блок памяти 12.

Устройство работает следующим образом.

Фазные напряжения сети подаются на вход формирователя 1, на выходе которого формируются 3 последоватеш ности двухполярных прямоугольных импульсов, сдвинутых друг относительно друга на 1200 эл. по частоте сети.

Эти последовательности поступают на входы первого сумматора 2, на выходе . которого вырабатываются прямоугольные импульсы с частотой Ес (для мостовой трехфазной схемы). Одновременно от генератора импульсов 3 через блок суммирования 4 импульсы поступают в делитель 5, выполненный на счетчике. На выходе делителя вырабатывается последовательность тактовых импульсов для системы управления выпрямителем.

Кроме того, эти импульсы поступают на вход счетчика 6, на выходе которого формируются 3 последовательности импульсов синхронизации, .сдвинутые друг относительно друга на 120 эл. по частоте сети, что обеспечивается подбором частоты генератора импульсов и коэффи- циентами деления делителя 5 и счетчика 6. В случае нулевой схемы эти mvrпульс ы непосредственно передаются на входы синхронизации системы управления.

Для мостовой схемы в каждом канале включаются генераторы 7 со счетным входом, обеспечивая 6 последовательнос гей cî oсдвигом на 60 an. (Ед

Три последователь» ности ймпульсов с выхода счетчика поступают на входы второго сумматора 8, на выходе которого формируется прямо угольное напряжение с частотой, соответствующей частоте напряжения на выходе первого сумматора (a случае отсутствия ошибки, но сдвинутое по фазе на 180 эл. Оба эти напряжения пою.гупают на входы фазового дискриминатора

9, построенного по схеме сумматора 10 и реверсивного счетчика 11. Если расхождения по фазе (частоте) в сформированных на выходе устройства импульсах синхронизации относительно напряжений сети нет, то на выходе фазового дискриминатора сигналы отсутствуют и коррек- ции фазы не происходит. В случае наличия ошибки на выходе. сумматора 10 фазового дискриминатора на каждом интервале дискретности выпрямителя появляются импульсы, длительнос.гь которых пропорциональна величине ошибки по фазе. В течение этих импульсов реверсивный счет.чик 11 с частотой f записывает в блок памяти 12 код числа, соответствующего величине и знаку ошибки. Это число счи, тывается блоком суммирования, который на интервале дискретности выпрямителя добавляет или собирает" импульсы генера, -6м тора 3 на входе делителя 5. Если ошибка компенсирована за время, меньшее интервала дискретности, то коррекции прекращается. При больших ошибках с приходом очередного импульса с фазового 5 дискриминатора бпок памяти обнуляется, и в него записывается код числа, соот ветствуюшего нескорректированной ошибке.

- Таким образом, использование сумма- 1О торов обеспечивает формирование информа-,. ции об ошибке по фазе импульсов синхро низапии относительно напряжений сети через каждый интервал дискретности ти» ристорного выпрямителя, оргышзапия 1 структуры фазового дискриминатора на пифровой основе, т.е. ha полусумматоре и реверсивном счетчике с выходом на блок «добавления-вычитания" через блок памяти обеспечивает, в случае записи в 2î память ошибки, .равномерное добавление (или вычитание) импульсов блоком сум мирования на всем интервале дискрежости выпрямителя пока существует инфор мания об ошибке,. «разравнивая" скоррек 2s тированную последователнность импульсов, поступающую на вход делителя. До олнительная связь - вькода формирователя со входом счетчика обеспечивает синхро)низацию начала работы устройства. Уст- ур

Ьойство обеспечивает одновременно пс стояеиую кратность тактовой частоты и яастоты синхронизапии и одновременнуй фазовую коррекшпо иМпульсов синхрони зации и тактовых импульсов, передаваемъи фазового управления выпрямителем. Пе речисленняя совокупность отличительных признаков обеспечивает достижение .поставленной пели.

Формула изобретения

Устройство для синхронизации пифро вьк систем управления тиристорными 41 6, выпрямителями, содержащее генератор импульсов, вькод которогр подключен к одному из входов блока суммиро, выход которого подключен ко входу делителя, фазовый дискриминатор и три вькодных триггера, о т л и ч а ю ш ее с я тем, что, с. целью повъапения точности синхронизации и быстродейст:вия, оно снабжено формирователем иМпульсов перехода сетевого напряжения через ноль, двумя с жматорами с одно полярной характеристикой, счетчиком

:и блоком памяти, причем входы вышеуказанного формирователя предназначены для подключения питающей трехфазной сети, выводы подключены ко axogaM первого вышеуказанного сумматора, вькод которого подключен к одному из входов фазового дискриь инатора, на другой вход фазового дискриминатора подключен выход второго выпеуказанного сумматора, тремя своими входами цодключенного к выходам счетчика и входам вькодных триггеров, вькод фазового дискриминатора подключен через блок памяти ко второму входу блока суммирования, выход делителя подклюйн к счетному входу фазового дискриминатора и к первому входу счетчика и одновременно является вькодом устройства, один из выходов възиеуказанного формирователя подключен ко второму, входу счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 605305, кл. Н 02 Р 13/21, 1978.

2. Авторское свидетельство СССР

¹ 629621, кл. Н 02 Р-13/16, 1978.

3. Авторское свидетельство СССР № 647833, za. Н 02 Р 13/16, 1979.

4. Авторское свидетельство СССР

¹ 748779 кл. Н 02 Р 13/16, 1980.

5. Авторское свидетельство CCCP

% 611309, кл. Н 02 P 13И.6, 1978 (прототип).

Составитель Г. Ефимов

Редактор Н. Горват Техред E.Õàðèòîí÷èê Корректор А. Дэятко

Заказ 11148/77 . Тираж 685 Подписное

ВНИИПИ Государсч венного комитета СССР по делам изобретений и открытий

113035, Москва, 5, Раушская наб., д. 4/5

Филиал ППП Патент», r. Ужгород, ул. Проектная, 4