Балансировочное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 07. 07. 81 (21) 3318449/25-28 )$1) М. Ка.>

Союз Советскик

Социалистических республик с присоединением заявки М— (23) Приоритет—

С .01 И 1/22

Государственный комитет

СССР по делам изобретений и открытий

РИУДК 620.1.05!

: 531. 24 (088. 8) Опубликовано 2301.83. Бюллетень Йо 3

Дата опубликования описания 2301.83 (72) Авторы иэобретеии я

:Л.В.Завадский,. Г.A.Øèãàëåâ и М.Б.Пальчук (71) Заявитель (54) ВАЛАНСИРОВОЧНОЕ УСТРОЙСТВО

Йэобретение относится к балансирб= вочной технике и может быть использовано в балансировочных станках — автоматах с разделенными измерительной и корректирующей системами.

Известно балансировочное устройство, содержащее блок измерения с датчиками дисбаланса; связанный с ним блок устранения влияния плоскостей коррекции и блок обработки сигнала, к выходу которого подключен указар тель дисбаланса t1 j.

Недостатком устройства является отсутствие блоков промежуточной памяти, что исключает их применение в балансировочиых автоматах с разделенными измерительной и корректирующей системами.

Наиболее близким по технической сущности к изобретению является балансировочное устройство, содержащее последовательно соединенные двухканальные бЛок иэмеревия ДИСбаланса, в который входят датчики, опорный. генератор, усилитель, демодулятор и преобразователь, блок промежуточной памяти, каждый канал которого состоит иэ соединенных последовательно аналогового ключа и запоминающего блока, входы блока соединены с выходами блока измерения через блок памяти, и блок управления, предназначенный для формирования системы команд управления блоком измерения и механизмом корректировки, который содержит механизма отсчета глубины сверления и механизма ориентации ротора по углу. По параметрам дисбаланса, хранящимся в блоке промежуточной памяти, последний управляет работой сверлильных головок.

Устройство позволяет произвести замер параметров дисбаланса ротора по двум плоскостям одновременно, запомнить эти параметры, передать их в блок промежуточной памяти, количество каналов которого зависит от количества запоминаемах параметров.

Цикл работы устройства позволяет производить одновременно замер пара" метров дисбаланса одного ротора и коррекцию дисбаланса другого по данным замера в предыдущем цикле, результаты которого передаются в промежуточную память вместе с перемещением ротора с измерительного блока на механизм коррекции f 2), Недостаток устройства заключается в том, что оно не обеспечивает тре-буемой точности балансировки, так

991207 как отсутствует контроль за передачей измеренных параметров в блок промежуточной памяти. В случае нарушения контактов в аналоговых ключах или неисправностей запоминающего блока каналов блока промежуточной памяти измеренные параметры будут переданы с искажениями, что приведет к ошибочной коррекции дисбаланса ротора, и, как следствие, к снижению точности балансировки ротора. !О

Целью изобретения является повышение точности балансировки.

Поставленная цель достигается тем, что балансировочное устройство, содержащее последовательно соединенные двухканальные блок измерения дисбаланса, блок памяти и блок промежуточной памяти, а. также блок управления, снабжено формирователем сигнала, выполненным в виде последовательно соединенных формирователя импульсов, вход которого соединен с выходом блока управления, вибратора и инвертора, а также триггера, выход которого связан с входом блока управления, а первый вход — с выходом формирователя импульсов, и логического элемента 4И, выход которого соединен с вторым входом триггера, а каждый канал блока промежуточной памяти имеет две цепи, каждая иэ которых выполне- ЗО на в виде последовательно соединенных аналогового ключа, вход которого связан с выходом вибратора, запоминающего блока, компаратора, второй вход

° которого связан с одним из выходов блока памяти, и логического элемента

ЗИ, второй вход которого связан с выходом инвертора, третий вход - с выходом блока управления, а выходс одним иэ входов логического эле- 4О мента 4И.

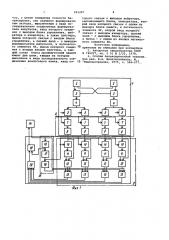

На фиг. 1 изображена структурная схема балансировочного устройства; на фиг. 2 - временная диаграмма работы блока промежуточной памяти.

Устройство содержит блок 1 измерения, разделенный на два измерительных канала, каждый из которых состоит иэ соединенных последовательно датчика 2 дисбаланса, сумматора 3 схемы разделения плоскостей коррекции, усилителя 4 сигнала датчика 2 дисбаланса и двух, связанных между собой и с выходом усилителя 4 синхрон- 55 ных . дете кторов 5, при этом второй выход датчика 2 дисбаланса одного канала связан с вторым входом сумматора 3 другого канала, блок 6 памяти, состоящий из двух каналов, каждыйбО из которых содержит две цепи, состоящие иэ последовательно соединенных аналогового ключа 7, связанного с выходом, соответствующего синхронного детектора 5 блока 1 измерения и запоминающего блока 8,блок 9 промежуточной памяти, состоящий иэ двух одинаковых каналов, а каждый канал в свою очередь имеет две цепи, каждая иэ которых выполнена в виде последовательно соединенных аналогового ключа 10, вход которого связан с выходом соответствующего запоминающего блока 8 блока 6 памяти, запоминающего блока 11, компаратора 12, второй вход которого связан с одним иэ выходов блока 6 памяти, и логического элемента ЗИ 13. Устройство содержит также блок 14 управления и формирователь 15 сигнала, который выполнен в виде последовательно соединенных формирователя 16 импульсов, вход которого соединен с выходом блока 14 управления, вибратора 17 и инвертора 18, а также триггера 19, выход которого связан с вхолом блока 14 управления, а первый вход - с выходом формирователя 16 импульсов, и логического элемента 4И

20, выход которого соединен с вторым входом триггера 19, при этом выход вибратора 17 связан с входом аналогового ключа 10 каждого канала и каждой цепи блока 9 промежуточной памяти, второй вход логического элемента ЗИ

13 каждого канала каждой цепи блока связан с выходом инвертора 18, третий вход — с выходом блока 14 управления, а выход - с одним входом логического элемента 4И 20.

Устройство работает следующим образом.

Колебания опор станка (не показан), пропорциональные дисбалансу ротора. (не показан), воспринимаются и преобразовываются в электрический сигнал датчиками 2 дисбаланса, расположенными в блоке 1 измерения. Так как блок 1 измерения содержит два идентичных канала, то рассмотрим работу одного из них, например левого.

Сигналы датчика 2 дисбаланса поступают на входы сумматоров 3 схемы разделения плоскостей коррекции, с помощью которых сигналы датчиков 2 приводятся к заданным плоскостям коррекции. Приведенный сигнал с выхо« да сумматора 3 поступает на вход уси« лителя 4 сигнала датчика 2 дисбаланса, затем на входы синхронных детекторов 5, управляемях от генератора (не показан) опорных сигналов, На выходе синхронных детекторов 5 получим постоянные напряжения,, пропорцио" нальные проекциям вектора дисбаланса на заданные оси коррекции. Эти напря жения через аналоговый ключ 7 поступают на вход запоминающего блока 8, представляющий собой аналоговый запоминающий блок компараторного типа.

После окончания измерения командой иэ блока 14 управления (связи на

991207 структурной схеме не указаны) закрывается аналоговый ключ 7 и вся информация о дисбалансе ротора в левой плоскости коррекции хранится в запоминающих блоках 8, В высокопроизводительных балансировочных автоматах измерительная и корректирующая позиции обычно разделены, и в обработке на автомате находятся сразу два ротора: у одного дисбаланс измеряется, а у второго — корректируется. При этом информация о дисбалансе ротора привязывается к положению ротора на автомате« если ротор находится на измерительной позиции, то информация

o его дисбалансе находится в запомиt0 нающих блоках Б блока 6 памяти (после окойчания цикла измерения) . При перепульсов приходит сигнал, и на его seходе формируется-отрицательный им пульс, длительность которого должна быть больше времени установления

35 триггера 19 в нулевое состояние.Формирователь 16 импульса может быть реализован на двух интегральных микросхемах К 511ЛА1 и цепочке RC, за40 дающей длительность импульса. Импульс с выхода формирователя 16 поступает на К-вход триггера 19 R-типа и устанавливает его в нулевое состояние.

Одновременно этот импульс поступает на вход вибратора 17, который формирует импульс передачи информации, длительность которого выбирается по постоянной времени запоминающего блока 11. Схема вибратора 17 может быть реализована с помощью трех эле45

50 ментов 2И-НЕ., в качестве которых применены интегральные микросхемы

К 511JIA1. Вибратор 17 запускается по переднему фронту отрицательного импульса, и длительность формируемого им импульса определяется только внутренней RC-цепочкой. Так как блок

9 промежуточной памяти содержит идентичные цепи, количество которых зависит от количества запоминаеьих параметров дисбаланса ротора, Рассмотрим работу одной из цепей. Выходной импульс вибратора 17 открывает аналоговый ключ 10 и тем самим разрешает передачу информации из блока 1 а> мещении ротора с измерительной позиции на корректирующую информация о

его дисбалансе должна также передви- 2О нуться в запоминающий блок 11 блока

9 промежуточной памяти и хранится там до окончания коррекции дисбаланса этого ротора. Эта информация используется для отсчета перемещений 25

-корректирующих головОк (не показаны). и ориентации ротора по углу при коррекции. Задача передачи информации решается следующим образом. При поступлении команды.из блока 14 30 управления на разрешение передачи информации в блок 9 промежуточной памяти на вход формирователя 16 имизмерения в запоминающий блок 11. .Время передачи определяется длительностью выходного импульса вибратора ,17. В момент времени t когда значения напряжений на входе аналогового ключа 10 и на выходе запоминающего блока 11 сравниваются или их разность не превысит значений уровней компаратора 12, на выходе последнего сформируется высокий уровень напряжения. Компаратор 12 представляет собой два Однопороговых компаратора, .разнополярные входы которых соединены между собой. Порог срабатывания компаратора 12 от нуля (эа нуль принимается разность двух сравниваемых и одинаковых по величине напряжений на входе компаратора 12) в обе стороны настраивается одинаковым и выбирается по величине разрешенной ошибки в передаче информации.

Сигнал с выхода компаратора 12 посту пает на вход логического элемента 3Н

13. Так как второй вход элемента ЗИ

13 соединен с выходом блока 14 управления, а третий через инвертор 18с выходом вибратора .17, то в момент времени tz на выходе элемента 13 сформируется сигнал, соответствующий состоянию выхода компаратора 12.Этот сигнал поступит на один из входов логического элемента 4И 20. При наличии на всех входах элемента 20 одно= временно высоких уровней, на его выходе формируется высокий уровень, который поступит на $-вход триггера

19 и установит его в единичное состояние. С выхода триггера 19 в блок 14 управления поступит команда об окончании передачи информации из блока 1 измерения в блок 9 промежуточной памяти. Если хотя бы в одной из цепей за время tg не произойдет полной передачи информации, команда об окончании передачи информации в блок 14 управления не поступит и разрешения на коррекцию дисбаланса этого ротора не будет получено.

Таким образом, устройство обеспечивает автоматический контроль эа передачей измеренных параметров в блок промежуточной памяти, а наличие в каждой нз цепей блока промежуточной памяти элементов, контролирующих полученную информацию, позволяет.осуществлять диагностику неисправностей секций, что повышает точность балан,сировки.

Формула изобретения

Балансировочное устройство, содержащее последовательно соединенные двухканальные блоки измерения дисбаланса, блок памяти и блок промежуточной памяти, а также блок управления, о т л и ч а ю щ е е с я тем, 991207 что, с целью повьвения точности балансировки, оно снабжено формирователем сигнала, выполненным и виде последовательно соединенных формирователя импульсов, вход которого соединен с выходом блока управления, вибратора и инвертора, а также триггера, выход которого связан с входом блока управления, а первый вход - с выходом формирователя импульсов, и логического элемента 4И, выход которого соединен с вторым входом -триггера, а каждый. канал блока промежуточной памяти имеет две цепи, каждая из которых выполнена в виде последовательно соединенных аналогового ключа, вход которого связан с выходом вибратора, запоминающего блока, компаратора, второй вход которого связан с одним из выходов блока памяти, и логического элемента ЗИ, второй вход которого связан с выходом инвертора, третий вход — с выходом блока управления, а выход - с одним из входов логического элемента 4И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 746227, кл. G 01 N 1/22, 1978.

2. Основы балансировочной техники.

Под ред. В.А. Щепетильникова. И., 15 "Машиностроение, 1975, с. 566-577.

991207

Составитель P. Гайнутдинова

Редактор Н. Лазаренко Техред И.Коштура Корректор О.Билак

Заказ 111/5á Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауiаская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4