Двухканальный фазовый компаратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<>991327 (61) Дополнительное к авт. сеид-ву 1. 900214 (22) Заявлено 09.02.81 (21) 3236557/18-21

)ggj g+ з. с присоединением заявки ¹â€”

G 01 R 25/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 2301,83. Бюллетень № 3

53) УДК 621, 317, 3 (088 . 8) Дата. опубликования описания 230183

A.Ñ.Ãëèí÷åHêo, E.Ä.Êoëòèê, В.И.Ко

С.В.Чепурных, М.К.Чмйх и М.С.Г

1 (72) Авторы изобретения авченко, т (71) Заявитель (5 4 ) ДВУХ КАНАЛЬНЬЯ ФЛЗОВЬ1Й KONIIAPATOP

Изобретение относится к радиоиэмерительной технике, По основному авт.св. Р 900214 известен двухканальный фазовый компаратор, содержащий в каждом канале последовательно соединенные преобразователь фазового сдвига в интервал времени, выходы которого являются входами устройства, блок квантования, формирователь кодов, вычислительный блок, общий для обоих каналов генератор импульсов, выход которого соединен с вторыми входами первого и второго блоков квантования и с вторыми входами первого и второго времязадающих блоков, первые входы времязадающих блоков соединены сост ветственно с выходами первого и вто- . рого преобразователей сдвига- фаэ в интервалы времени, первые выходы времязадающих блоков соединены с третьими входами блоков квантования, а вторые с вторыми входами вычислительных блоков, выходы вычислительных блоков соединены с входами блока сравнения кодов, выход которого соединен с входом блока управления, выходы блока управления соединены соответственно с вторыми входами формирователей кодов и третьими вхоцами времязадающих и вычислительных блоков (1 3.

Недостатком устройства является низкая точность измерения.

Цель изобретения - повышение точ,ности измерения.

Эта цель достигается тем, что в двухканальный фазовый компаратор ввецен блок синхронизации каналов, соединенный первым и вторым, третьим и четвертым входами соответственно с первыми и третьими выходами первого и .второго времязадающих блоков, пятым и шестым входами — соответственно с выходами первого и второго пре.образователей сдвига фаз в интервалы времени, седьмым входом - с выходом блока управления, выход блока синхронизации каналов соединен с четвертыми входами первого и второго времязадающих блоков, причем блок синхронизации каналов содержит два элемента совпадения, четыре RS-триггера, общий для обоих каналов третий элемент совпадения, выход которого соединен с четвертыми входами первого и второго времязадающих блоков, а входы соединены с выходами первого, второго, третьего и четвертого

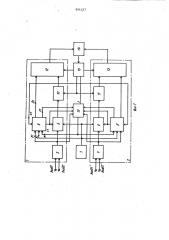

RS-триггеров, R-входы четырех RS991327 нены по структурным схемам, описанным в известном устройстве, и содержат последовательно -соединенные соответственно RS-триггеры 24 и 25, D-триггеры 26 и 27, элементы 28 и 29, времяэадающие счетчики 30 и 31.

Компаратор фазы работает следую- ° 0, щим образом.

На входы канала 1 поступают два сигнала с частотой F< и заданным сдвигом фаэ Ч1, на входы канала

2 поступают сигналы с частотой Г2 и фазовым сдвигом «, которые нужно сравнить. Преобразователи 3 и 4 формируют эквивалентные временные интервалы (фиг.3 5„, 52),которые в блоках

5 и б заполняются счетными импульса- 0 ми частоты Г = — от генератора 7.

ij

Образующиеся пачки импульсов регист-. рируют ся формирователями 10 и 11 .

Времязадающие блоки 8 и 9 и блок 16 формируют для каждого канала время триггеров соедИнены с выходом блока управления, S-входы третьего и чет.вертого RS-триггеров соединены соответственно с третьими выходами первого и второго времязадающих блоков, S-входы первого и второго RS-тригге- 5 ров соединены с выходами соответственно первого и второго элементов совпадения, первые входы которых соединены с первыми выходами соответственно первого и второго времязадаю-10 щих блоков, а вторые входы - с выходами первого и второго преобразователей сдвига фаз в интервалы времени.

На фиг.1 приведена структурная схема компаратора фазы1 на фиг.2 структурная схема блока синхронизации каналов, связанного с времязадающими блокамир на фиг.3 — временные диаграммы, иллюстрирующие работу компаратора фазы.

Структурная схема компаратора фа- . зы (фиг.1) содержит два измерительных канала 1 и 2, содержащих последовательно соединенные преобразователи 3 и 4 сдвига фаэ в интервалы времени, блоки 5 и б квантования с подключенным к ним генератором 7 импульсов, времяэадающие блоки 8 и 9, формирователи 10 и 11 кодов, вычислительные блоки 12 и 13, связанный с ними блок 14 сравнения кодов, блок

15 управления, связанный с блоками

8-14; 16, блок 16 синхронизации каналов преобразователями 3 и 4 и соединенный с блоками 8 и 9. 35

Структурная схема блока 16 (фиг.2) содержит два элемента 17 и 18 совпадения, четыре RS-триггера.19-22, общий элемент 23 совпадения, входы которого соединены с выходами четырех 40 .RS-триггеров. Блок 16 связан с идентичными блоками 8 и 9, которые выпол измерения, равное целому числу пери.одов сигнала. В диапазоне частот 1

1 1 1 1

F — ) т 2 т иэм„ т время измерения для каждого канала определяется из условия сиам = (tè / изм изб

/T ) -Т+Т=п Т, где Т вЂ” период сигнала, (й,« /Т) - целая часть отношения и мo иэмо /Т

На частотах выше F= — время иЬмц измерения изменяется в прецелах изм виэм виэм +Т, для частот

1 о

F <

t время измерения определяиэм« ется периодом сигнала Т (фиг. 3. г2 ) .

Если период входного сигнала одного канала меньше базового времени измерения, например Т„< t„(фиг.36„), имэмо а период входного сигнала другого канала больше базового времени измере..ия, например Т2 v t» (Фиг.3б2), тогда время измерения для каждого канала определяется из условий:

t„ „= (Т2/2TÄ ) ° Т1+Т„(фиг. Зг ) виэм = иэм2

=T> (фиг Зг2 ), где т /2Т«Д -. целая часть отношения Т2/2Т.1. При этом на

1 частотах выше F= время измерения . виэм одного канала изменяется в пределах виэм

Благодаря увеличению времени измерения одного канала, уменьшается погрЕшность дискретного преобразования в области верхних частот, повышается точность сравнения измеряемых фазовых сдвигов без увеличения измерительного цикла компаратора фазы.

За время измерения в <рормировател

10.и 11 формируются кодый п2 «1е1 1j и я = 1 <О во времязадающих

2 .1=1 21 блоках 8 и 9 формируются коды

П1 2

4т = т„. о, 1 )т = 12 . Да.ные

Т1 11 1 О Т2 1 1 21 коды вводятся в вычислительные блоки

12 и 13, rye выполняется деление кодов . и -" и их умножение на масш"1 1% . Ч NT Г табный множитель 360.

Результаты вычислений соответству3ЬО 11, ют сдвигам фаз в градусах:

Ъьо М .1

2 q< т2

В блоке 14 сравнения кодов проис-ходит вычитание кодов Ч„и Ч 2, полученный код а O = Ч,-Ч соответствует отклонению сравниваемого сдвига фаэ от заданного. Блок 15 обеспечивает функционирование отдельных блоков компаратора фазы.

991327

Блок 16 работает следующим образом.

В исходном состоянии RS-триггеры

19-22 установлены в нулевые состояния и сигналом с выхода элемента 23 RSтриггеры 24 и 25 установлены в нулевые состояния. По команде с блока 15 (фиг.За) RS-триггеры 24 и 25 по входам S(а„,а ) устанавливаются в единичные состояния. Ближайшими по времени импульсами привязки к одному из нуль-переходов входных сигналов с 10 преобразователей 3 и 4 {;:ôèã.36, б )

0-триггеры. 26 и 27 устанавливаются в единичные состояния (фиг.Зг„,г ).При этом открываются соответственно эле.менты 17, 28 и 18, 29. Через открытые 15 элементы 28 и 29 импульсы частоты

1 от генератора 7 поступают: на

0 to .времязадающие счетчики 30 и 31. К выходу и-го разряда времязадакщего 20 счетчика 30 подключен 5-вход RS-триггера 21 и в момент заполнения этого разряда, соответствующий времени и з =Nt0, RS òðèããåð 21 переключаизмоется в единичное состояние. Выход 25 й-го разряда времязадающего .счетчика

31 соединен с S-входом RS-триггера:

22 и через время с„з„„ -йс RS-триггер

j22 переключается в едйничйое состояние. Ближайшие по времени импульсы привязки.к соответствующим нуль-переходам входных сигналов преобразователей 3 и 4 проходят через открытые элементы 17 и 18 и.переключают RS-триггеры 19 и 20 в единичные состояния. Единичные состояния на выходах RS-триггеров 19-22 открывают элемент совпадения 23, сигнал с выхо-. да которого переключает RS-триггеры

24 и 25 в нулевые состояния (фиг.Зж).

Ближайшими импульсами привязки с преобразователей 3 и 4 фазовых сдвиговв интервалы времени 0-трйггеры 26 и

27 устанавливаются в нулевые состоя ния, закрывают элементы 28 и 29,что соответствует окончанию времени изме- 45 рения каждого канала (фиг.Зг„,г ), Для управления работой времязадающих блоков 8 и 9 вместо двух RS -триггеI ров 24 и 25 может быть использован один RS-триггер. Коды времязадающих 50 счетчиков 30 и 31, равные соответственно МТ„ и ЙТ, поступают в вычислительные блоки 12 и 13, а импульсы с выходов D-триггеров 26 и 27 длительностью t„ и Т и t и Т иэм (фиг.Зг,r ) управляют блоками 5 и 6.

Введение новых элементов и csaзей повышает точность измерения двухканального фазового компаратора, работающего в диапазоне частот 0,001 Гц2 мГц.

Формула изобретения

Двухканальный фазовый компаратор по авт.св. Р 900214, о т л и ч а юшийся тем, что, с целью повышения точности измерения, в него вве ден блок синхронизации каналов,соединенный первым и вторым, третьим и четвертым входами соответственно с первыми и третьими выходами первого и второго времязадакиаих блоков, пятым и шестым входами — соответственно с выходами первого и второго преобразователей сдвига фаз в интервалы времени, седьмым входом - с выходом блока управления, выход блока синхронизации каналов соединен с четвертыми входами первого и второго времязадающих блоков, причем блок синхронизации каналов содержит два элемента совпадения, четыре RS-триггера, общий для обоих каналов третий элемент совпадения, выход которого соединен с четвертыми входами первого и второго времязадающих блоков, а входы соединены с выходами первого, второго, третьего и четвертого RSтриггеров, R-входы четырех RS-триггеров соединены с выходом блока управления, S-входы третьего и четвертого

RS-триггеров соединены соответственно с третьими выходами первого и второго времязадающнх блоков, 5-входы первого и втОрого RS-триггеров соединены с выходами соответственно первого и второго элементов совпадения, первые входы которых соединены с первыми выходами соответственно первого и второго времязадающих блоков, а вторые входы - с выходами первого и второго преобразователей сдвига фаз в интервалы времени.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 900214 по заявке Р 2931209/18-21, кл. G 0 I R 25/00, 1980 (прототип).

ЕЭ1327

Составитель О.,Кибовская

Редактор A.ÊÎçîðèç Техред Е.Харитончик Корректор М.Коста

Заказ 124/62 Тираж 708 Подписное

ВНИИПИ Государственного комитета СССР

М- по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4