Устройство для обработки информации

Иллюстрации

Показать всеРеферат

<»> 991406

ОЛ ИСАНИЕ

И ЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социаиистичвскнх республик (61) Дополнительное к авт. санд-ву(22)Заявлено 10.07.81 (21)3316758/18-24 (5l)N. Кл.

G 06 F 3/04

I с присоединением заявки Pk

Гесудерстеелеый кеметет

СССР (23) Приоритет

Опубликовано 23.01 ° 83. Бюллетень М 3 (53) УДК681.327 (088.8) ао делам лзебретеняй и открытий

Дата опубликования описания 23.0 1.83

М. Д, Генки н, 8, È. Tàðàðû÷êèí, О.Б. Скворцов, В. C. Ãîëóáåâ —: =:, u В,И.Шагурин

Ю (72) Авторы изобретения

lf

Государственный научно-исследовательский институТ--мак>иноведения им. акад, А.А, Благонравова

1 (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ

Изобретение относится к вычисли-тельной технике и может быть использовано в системах технической диагностики, Известно устройство для обработки информации, содержащее входной блок, блок управления, многоканальный накопитель и коммутатор, выходы и входы которого соединены соответственно с выходами устройства и выходами многоканального накопителя, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с управляющим входом коммутатора, а вход входного блока соединен с входом устройства 1 3, Недостатками этого устройства являются его сравнительно узкие функциональные возможности, низкое -быст20 родействие и ограниченная точность.

Наиболее близким к изобретению по технической сущности является устройство для обработки информации, со-.

2 держащее входной блок, блок управления, первый и второй коммутаторы и блок памяти, выходная и входная шины которого соединены соответственно с первой группой входов первого коммутатора и выходом второго коммутатора, управляющий вход которого соединен с выходом блока управления и управляющим входом первого коммутатора, вспомогательный выход и вход блока управления соединены соответственно с тактовым входом блока и управляющим входом устройства для предварительной обработки информации, информационный, вход которого соединен с входом входного блока (2 3.

Недостатком этого устройства является ограниченная область примене ния в связи с тем, что оно не позволяет обеспечить ввод. данных в стан.дартные вычислительные устройства, которые обычно ориентированы на ввод данных, равномерно распределенных во времени

991406

3

Целью изобретения является расширение области применения устройства за счет равномерного распределения выходных данных во времени.

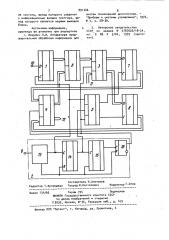

Указанная цель достигается тем, что в устройство для ввода информации,содержащее первый коммутатор, .первый выход которого соединен с ïåðвым входом блока памяти, выход которого подключен к первому входу:второго коммутатора, второй вход которого объединен с первым входом первого коммутатора и соединен с первым выходом блока управления, второй вы" ход которого подключен к первому входу блока сопряжения, второй вход которого является информационным вхоф второй и третий коммутаторы 3-, сумматор 6, первый и второй блоки 7 и 8 памяти, управляющий информационный и сигнальный входы 9- ll устройства, выход устройства,12, формирователь 13 тактовых сигналов, первый и второй делители 14 и 1 частоты, триггер 16.

Устройство работает следующим образом, В исходном состоянии по сигналу формирователя 13 и блока 2 обеспечивается установка всех узлов в "0".

При этом первый вход сумматора 6 через коммутатор 4 соединен с выходом блока 7, вход которого через коммутатор 3 соединен с выходом сумматора

6, входные данные с входа 10 через дом устройства, введены сумматор, вто рой блок памяти и третий коммутатор, первый, второй и третий входы котОрого соединены с вторым, третьим и. первым выходами блока управления соответственно, первый и второй выходы коммутатора с вторым входом первого блока памяти и с первым входом второго блока памяти соответственно, выход второго блока памяти подключен к третьему входу второго коммутатора, первый выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу блока сопряжения, а выход " к второму входу первого коммутатора, третий вход которого является сигнальным входом устройства, выход коммутатора соединен с вторым входом второго блока памя55, ти, второй выход второго коммутатора является выходом устройстза, блок управления содержит первый и второй делители частоты, триггер и формирователь тактовых сигналов, 40 вход которого является управляющим входом блока, первый выход соединен с информационным входом первого делителя частоты и явпяется вторым вы" блока второй вход подсоединен к установочным входам первого и вто- . рого делителя частоты и триггера, выход первого делителя частоты является третьим выходом блока и соединен с информационным входом второго делителя частоты,. выход которого соединен с информационным входом триггера, выход которого является первым выходом блока.

На чертеже изображена схема уст- 55 ройства, Устройство содержит блок 1 сопряжения., блок 2 управления, первый, . блок 1 синхронно с управляющими импульсами с вспомогательного выхода блока управления поступают на сумматор 6, который совместно с блоком 7 обеспечивает синхронное накопление сумм 5.1. где S - накопленная в i-ой ячейке

1 блока памяти сумма; число усредняемых реализаций; и - число выборок в одной реализации, Результирующая последовательность может рассматриваться как полученная из входного сигнала путем фильтрации через фильтр с передаточной функцией т,е, фильтр с единичным коэффицие -

Я.Й том пропускания на частотах w =1 —

AT где Т - период формиРования выборокпериод импульсов на вспомогательном выходе блока 2, На этих частотах устройство не вносит также дополнительного фазового сдвига. На остальных частотах составляющие входного сигнала подавляются, Благодаря этому, после накопления k входных реализаций обеспечивается подавление юумов и "вредных" составляющих сложного входного сигнала. Деление íà k в (2) может быть заменено считыванием сумм S со сдвигом разрядов на m=log>k, что эквивалентно делению на 2п, в том случае, если k есть целая степень числа два.

06 формула изобретения .

1, Устройство для обработки информации, содержащее первый коммутатор, первый выход которого соединен с первым входом блока памяти, выход которого подключен к первому входу второго коммутатора, второй вход которого и первый вход первого коммутатора соединены с первым выходам: блока управления, второй выход которого подключен к первому входу блока сопряжения, второй вход которого является информационным входом устройства, о т л и ч а ю щ е е с я тем, что, сцелью расширения области применения устройства путем равномерного распределения выходных дан- ных во времени, в него введены сумматор, второй блок. памяти и третий коммутатор, первый, второй и третий входы которого соединены с вторым, тре-. тьим и первым выходами блока управле" ния соответственно, первый и второй выходы коммутатора соединены с вторым входом первого блока памяти и с первым входом второго блока памяти соответственно, выход второго блока памяти подключен к третьему входу второго коммутатора, первый выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу блока сопряжения, а выход - к второму входу первого коммутатора, третий вход которого является сигнальным входом устройства, выход коммутатора соединен с вторым входом второго блока памяти, второй выход второго коммутатора является выходом устройства, 2. Устройство по и. 1, о т л ич а ю щ е е с.я тем, что блок управления содержит первый и второй делители частоты, триггер и формиро-. ватель тактовых сигналов, вход которого является управляющим входом блока, первый вход соединен с инфор" . мационным входом первого делителя частоты и является вторым выходом блока, второй вход подсоединен к установочным входам первого и второго делителя частоты и триггера, выход первого делителя частоты является третьим выходом блока и соединен с информационным входом второго делите5 9914

После того как пройдет k циклов суммирования сигналом с выхода делителя 15 переключается триггер 16, выходной сигнал которого переключает коммуI татор 3, в результате чего суммы S. начинают накапливаться в блоке 8, а ранее накопленные суммы 5; считывают ся иэ блока 7 йа выход 12, причем, если вход ll соединен с шиной, имеющей. нулевой потенциал, происходит од-1О новременно и очистка блока 7. После завершения очередного цикла усреднения k реализаций происходит возврат иэ исходной коммутации, Суммы S; выдаются на выход с периодом, определяемым периодом импульсов на соответствующем выходе блока 2. Таким . образом, целесообразно выбрать коэффициент деления первого делителя 14 равным k, а коэффициент второго делителя 15 равным N. Синхронизация выборок может осуществляться с помощью управляющего сигнала, подаваемого на вход 9.

В описанном режиме выдача М выход->> ных выборок осуществляется равномерно эа время, равное МТ, т.е. за Nk входных выборок, т.е. осуществляется масштабирование выходных сигналов в

k раз, что существенно снижает тре- 30 бования по быстродействию последующей аппаратуры, Возможна также выдача выходных сумм.

5 и в том же темпе, что и формирование входных выборок. В этом случае частота импульсов на дополнительном выходе должна быть равна частоте импульсов на выходе блока 2, при этом вход 11 и выход 12 объединенй. В этом случае выходная последователь- ю ность S1 повторяется в течение цикла накопления, пока формируются суммы

S, k раз, т.е. выходная последовательI ность представляет собой последовательность входных данных после фильтрации и подавления случайных шумов со сдвигом во времени íà kNT. Если вход 12 не соединять с выходом 12, который, как и в рассмотренном ранее случае, соединить с шиной нулеаого логического сигнала, то выходная последовательность будет выдана в темпе поступления, входных .данных одной реализации, т.е. также как и в известном. устройстве.

Таким образом, совокупность существеных отличительных признаков изобретения обеспечивает расширение функциональных воэможностей известного устройства за счет равномерного распределения выходных даннмх..

Составитель И,Алексеев

Редактор Т,Кугрыщева Техред Ж.Кастелевич Корректор Г.Огар

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Заказ 134/66 филиал ППП "Патент", r, Ужгород, уа, Проектная, 4

7 . 991406 8 ля частоты, выход которого соединен систем технической диагностики. с информационным входом триггера, вы- "Приборы и системы управления", 1974, ход которого является первым выходом N 4, с. 28-30, блока, Источники информации, 2. Авторское свидетельство принятые во внимание при экспертизе СССР по заявке 1г 2787626/18-24, 1. Микулич Л.И. Аппаратура пред- кл. G 06 F 3/04, 1979 (протоварительной обработки информации для тип) °