Устройство для сопряжения

Иллюстрации

Показать всеРеферат

Союз Советсник

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<ц,991407

{61) Дополнительное к авт. саид-ву

{22)Заявлено 28.07.81 (2l) 3342810/18-24 (5! )М. Кл.

G 06 F 3/04 с присоединением заявки М

ГВс7юьрстееккый кемвтет

СССР

{23) ПриоритетОпубликовано 23.01.83. бюллетень М 3 дв делам втейретеввй и етарытий (53) УДК 681.327 (088.8) Дата опубликования описания 25 .01.83

А.П. 6олтков, С.Н. Хлевной и Н.И. Червяков (72} Авторы изобретения

/ с. с с

i «»

-(71) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано для сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (СОК ), а также в устройствах передачи данных, использующих коды СОК.

Известно устройство для декодирования кодов, представленных в СОК, ю содержащее вычитающие счетчики, вы« ходы которых подключены к входам пер" вого логического элемента И, выход ко» торого подключен к первому входу триггера выход которого подключен

Ф т5 к первому входу второго логического элемента.И, генератор тактовых импульсов, соединенный с вторым входом второго логического элемента И, выход которого соединен с тактовыми входа- 2о ми вычитающего счетчика и входом суммирующего счетчика, второй вход триггера соединен с шиной подачи импуль-. са записи 11.

Однако это устройство обладает малым быстродействием, так как велико время перевода кода, представленного в СОК в позиционный код.

Наиболее близким к изобретению по технической сущности является устройство, содержащее суммирующий декадный счетчик, выходы переноса декад которого через элементы запоминания переноса и элементы И/И подключены к счетным входам последующей декады суммирующего декадного счетчика, вы" ходы каждой декады которого соединены с соответствующими дешифраторами индикации, дешифрвторы, а также декад" ные счетчики и элементы И с запоми" нанием (2 .

Недостатками известного устройст" ва являются пониженное быстродействие и .сложность °

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее первый

991407 ф ны результата выполнения операции („В„, е- которая выполняется дешифратором 9 ий наибольшего по величине Основания.

Дешифратор 9 преобразует код остатка в коды разрядов десятичного числа,которые получаются при выполнении one" рации о -„Вв.

Пример 1. Пусть выбрана система оснований Р = 3, P g 5, Pg 7.

10 Тогда величина константы, соответствующея наибольшему по величине основахс- нию Р 7, равна В з = 15, в зависимости от кода остатка на выходе дешифратора 9 должны появиться коды, 1s представленные в табл. 1, которые записываются в декады 2 счетчика 1 B начальный момент времени.

Таблица 1

2 0

3 0

5 0

9 0

Остальные слагаемые выражения (1 J преобразовываются в число-импульсн«й код с дальнейшим последовательным порязрадным суммированием в счетчике 1.

Преобразование в число-импульсный код осуществляется следующим образом.

К входам всех дешифраторов 10 подключаются шины подачи кодов всех оставшихся остатков (первоначально на всех шинах 13 управления присутствуют нулевые потенциалы } при выполнении операции о пВп. На \п-1}-й шине 13 появляется единичный потейциал, а на выходных шинах дешифраторов 10 появляются коды, которые cooTâåòcòâóют разрядам десятичного числа выпол" нения операции К „1В„1. Причем коды на выходе дешифраторов 10 представле3 дешифратор, вхОды кОтОрОГО пОдключе к информационной шине устройства, д шифраторы первой группы и суммирующ счетчик, выходы которого подкпючены к входам соответствующих дешифрато" ров второй группы, выходы которых являются соответствующими. выходами устройства, введены блоки элемен-! тов совпадения и распределитель импульсов, вход которого является ши" ной синхронизации устройства, а выходы подключены к соответствующим в дам блоков элементов совпадения, вн ходы которых соответственно соедине ны с входами суммирующего счетчика, другие входы которого подключены к соответствующим выходам первого дешифратора, одни входы дешифраторов первой группы являются шиной управ,ления устройства, другие - его инфор- гр мационной шиной, выходы цашифраторов первой группы подключены соответственно к другим входам блоков элементов совпадения.

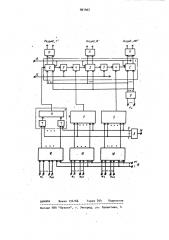

На чертеже представлена функцио- . 2$ нальная схема устройства.

Устройство содержит суммирующий счетчик 1, декаду 2, элементы 3 запоминания ереноса, первые элементы

ИЛИ 4, блоки 5 элементов совпадения, 3о вторые элементы ИЛИ 6, элементы И 7, распределитель В импульсов, первый дешифратор 9, дешифраторы 10 первой группы, дешифраторы. 11 второй группы, шину 12 переноса, шину 13 управ" 3$ ления, шину .14 синхронизации, шину 15 установки, Устройство работает следующим ofi» разом.

Для преобразования числа А =(с(., a2,+,..., d, 1 из СОК необходимо a«" полнить операцию

А = о(В1 + о(В +...+ КпВ п,(1) где В„- ортогональные базисы, являющиеся константами для выбранной сис-<$ темы СОК.

Устройство преобразует каждый разряд десятичного числа отдельных слагаемых выражения (1 } в число-импульс" ный код с дальнейшим последовательным $в поразрядным суммированием в общем декадном счетчике с учетом переноса импульса переполнения в следующую де" каду °

В начальный момент времени, cooT" $$ ветствующий подаче импульса предварительной записи по шине 15, осуществляется запись в декады 2 счетчика 1

Разряды

В сотен десятков единиц

4 0 6

5 9914 ны таким образом, что возбуждается количество выходных шин, численно равных значению соответствующего десятичного разряда.

Пример 2. Для основания Р„ з

5 В 21.

Количество возбуждаеиих шин на выходе дешифраторов 10 представлено в табл. 2.

Табл ица 2 10

Разряды

° « ° ° единиц сотен . десятков

О О

07 6 устройстве. все члены выражения (1 1 преобразуются в число»импульсный код, поэтому на перевод одного члена вы-ражения (1 ) требуется поступление 10

TBIcToBblx импульсов плюс один импульс переноса„всего для перевода числа известное устройство требует 11т1 так» товых импульсов, где и - "число выбранных оснований СОК. В предлагаемом уст-. ройстве перевод члена Ып Вп выраже.ния. (1 ) осуществляется в один такт дешифратором 9 наибольшего по величине основания. Поэтому предлагаемое устройство на перевод потребует 11п-10 тактовых импульсов, что меньше по сравнению с известным устройством на

10 тактовых импульсов.

0 2 l

О 4

6 3

8 4

О

В это же время на выходах распределителя 8 импульсов, имеющего 9 выходов, поочередно поступают импульсы, которые проходят только через те элементы И 7, на вторых входах кото- за рых присутствует сигналы, поступающие с выходов дешифратора 10.

Таким образом, на выходах блоков 5 совпадения появляются последовательности импульсов, представляющие собой число-импульсные коды. десятичных разрядов результата выполнения операции ...+el, В .

Эти число-импульсные коды поступают через элементы HJN 4 на счетные ав входы декад 2 счетчика I, тем санни к результату eLnBn прибавляется по модулю величина.

По окончании цикла работы распре" делителя 8 импульсов на шине 12 по- ц является импульс переноса, которьй. осуществляет перенос "1" или "0" элемента 3 запоминания в более старшую декаду 2.

В следующий момент времени единич- 0 ный импульс появляется íà (n-2)"й шине 13, и операция преобразования и суммирования повторяется вышеизложен-. ным образом.

Предлагаемое устройство по сравне">>

wo с известным обладает повышенным . быстродействием, так как в известном

Формула изобретения

Устройство для сопряжения, содержащее первый дешифратор, взводы. которого подключены к информационной шине устройства, дешифраторы первой группы и суммирующий счетчик, выходы которого подключены к входам соответ" ствующих дешифраторов второй груп:пы, выходы которых являются соответствующими выходами устройства, о тл и ч а ю щ е е с,я тем, что, с целью повышения быстродействия устро1Ъства, в него введены блоки элемен» тов совпадения и распределитель мм" пульсов, вход которого является шиной синхронизации устройства, а выходы подключены к соответствующим входам блоков элементов совпадения, выходы которых соответственно соединены с входами суммирующего счетчика, дру" гие входы которого подключены к соответствующим выхбдам первого дешифратора, одни входы деаифраторов первой группы являются шиной управления устройства, другие - информационной ши" ной, выходы дешифраторов первой группы подключены соответственно к другим входам блоков элементов совпадения.

Источники информации, принятые во внимание при экспертизе

1. Толстяков В.С, Обнаружение и исправление ошибок в дискретных уст" .ройствах. И.,"Советское радио", 1977, с. 55.

2. Авторское свидетельство СССР

И 506850, кл. G,06 F 3/04,i1971 (прототип ).

991407

ВНИИПИ Заказ 134/66 Тираж 704 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Рарряд„1" у 4и

Разряд„10" (4ty(Рнрп „100"