Устройство для деления

Иллюстрации

Показать всеРеферат

ОП ИСАН ИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советсимк

Социалистических

Республик

tuj991417 (6!) Дополнительное к аит. саид-ву 9 710040 (22) Заявлено 17.07. 81 (21) 3317936/18-24 с присоединением заявки Мо (23) Приоритет—

Опубликовано 230183. Бюллетень М 3

Р1 М К з

G,06 F 7/52

Государственный комитет

СССР ио делам изобретений и открытий (33) УДК 681 ° 325 (088. 8) Дата опубликования описания 23.01. 83 (72) Авторы изобретения

В. К. Велик и В. A. Буяло

Ордена. Ленина институт кибернетики AH Укра (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

Изобретение относится к вычислительной технике, и может быть использовано, в частности, в арифметических устройствах цифровых и комбинированных вычислительных машин.

По основному авт. св. М 710040 известно устройство, содержащее регистр делимого, регистр делителя, матрицу умножения и сумматор, причем и выходов регистра делителя подключены соответственно к первым и входам матрицы умножения, первые n ахо- . дов сумматора подключены к соответствующим и выходам регистра делимого вторые п входов сумматора подклю. чены к соответствующим п выходам матрицы умножения, а п выходов суглматора подключены соответственно к вторым и входам матрицы умножения(11.

Недостатком этого устройства является низкая точность, обусловленная неустойчивой работой при различных допустимых комбинациях делимого и делителя.

Целью изобретения является повы шение точности устройства.

Для достижения поставленной цели в устройстве для деления дополнительные m выходов матрицы умножения (m Ъ 1) соединены с соответствующими дополнительными вторыми входами матрицы умножения.

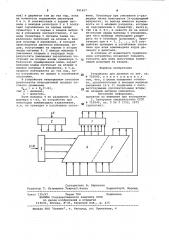

На чертеже показана структурная схема предлагаемого устройства для деления.

Устройство для деления содержит сумматор 1, регистр 2 делимого, регистр 3 делителя, матрицу 4 умножения, расширенную на дополнительную часть 5, и выходов регистра 3 делителя подключены соответственно к первым и входам матрицы 4 умножения, п выходов регистра 2 делимого подключены соответственно к п первым входам сумматора 1, и выходов которого подключены соответственно к вторым и входам матрицы 4 умножения, и выходов которой подключены соответственно к вторым входам сумматора 1, а m вторых входов дополнительной части 5 матрицы 4 умножения и m ee выходов соединены соответственно между собой.

Устройство работае1 следующим образом.

Одновременно подаются на регистры

2 и 3 делимое и делитель соответственно. По истечении переходных процессов в устройстве на выходе сумматора 1 формируется результат (част991417

Формула изобретения

Составитель B. Березкин

Редактор T. Кугрышева ТехредТ.Фанта

Корректор М. Шароши

Заказ 135/67 Тираж 704

BHHNtIH ГосударственногО комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 нов) и держится там до тех пор, пока не изменится содержимое регистров

2 и 3. В соответствии с кодами сигналы с выходов регистров 2 и 3 поступают параллельно на первые входы сумматора 1 и первые и входов матри- 5 цы 4 умножения соответственно. С выхода сумматора 1 сигналы также параллельно поступают на вторые и входов матрицы 4 умножения, в которой производится двоичное умножение ко- 10 дов, поступающих на первые и вторые входы матрицы 4. С выхода матрицы 4 умножения старшие и разрядов кода результата умножения параллельно постУпают на втоРые входы сумматора 1. 15

Результат суммирования вновь парал" лельным кодом поступает на вторые и входов матрицы 4 умножения, и т.д. процесс повторяется до тех пор, пока устройство не придет в устойчивое состояние.

В устройстве непрерывным способом реализуется итерационный процесс согласно уравнению — + Рц(I b), 25 где а — делимое, Ь вЂ” дели тель.

Если матрица 4 не расширена (т.е. размера n s n), то устройство при некоторых комбинациях эацикливает, т.е. не приходит в устойчивое состояние. Поскольку при умножении и-раз рядных чисел получается 2п-разрядный результат, то всегда имеется воэможность иэ и младших разрядов, которые не подсоединены к сумматору, взять m где 1 с m n, и завести их на допол. нительные входы матрицы 4 умножения, для чего матрицу необходимо расширить на m столбцов (разрядов), Практически при m = I, 2, ..., n/2 устройство приходит в устойчивое состояние при всех комбинациях кодов делимого и делителя.

В отличие от известного предлагаемое устройство позволяет повысить точность для всех допустимых комбинаций разрядов на входах.

Устройство для деления по авт. св.

Р 710040, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, дополнительные m выходов матрицы умножения (в ъ 1) соединены с соответствующими дополнительными вторыми входами матрицы умножения.

Источники информации, принятые во внимание при экспертизе .

1. Авторское свидетельство СССР

Р 710040, кл. G 06 F 7/52, 1975 (прототип).