Устройство для запуска цифровых интеграторов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<11 991424 (61) ???????????????????????????? ?? ??????. ????????-???? (22) ???????????????? 13. 03. 81 (21) 3262313>

РЦМ К з с присоединением заявки № (23) Приоритет

G 06 Р 7/64

0 06 0 7/18

Государственный комитет

СССР ио делам изобретеиий и открытий ($3j УДК 681,325 (088.8) Опубликовано 23.01.83. Бюллетень ¹ 3

Дата опубликования описания 23.01,83

1 с

Й с

Р; Ц;;.=1 -..

А ..5,. ° (72) Авторы изобретения

Г.Л.Биланов и A Í.Tèõîíîâ (71) Заявитель (54) УСтРОЙСтВО ДЛЯ ЗЛПУCKA ЦИЫОИЯХ ИНТЕГМтоРОВ

Изобретение относится к электроизмерительной технике и может найти применение при контроле сигналов, содержащих адцитивную помеху в виде переменной или постоянной составляющей, в том числе при помехозащищенных измерениях адаптивными интегральными выборками.

Известно устройство формирования адаптивных к частоте помехи команд . запуска цифрового интегратора, содержащее цепь отделения помехи, триггер Шмидта, фазочувствительный детектор и преобразователь напряжение- чаотота P1).

Однако это устройство имеет недостаточную точность определения моментов запуска при наличии низкочастотной составляющей исходного сигнала, поскольку при отделения ее от постоянной составляющей сигнала неизбежны искажения, обусловленные неравномерностью амплитудно-частотной характеристики и нелинейностью фазо-частотной, характеристики цепи отделения помехи. К тому же триггер

Шмидта обычно обладает гистерезисом.

Наиболее близким к изобретению является устройство для запуска цифровых интеграторов, содержащее пороговую схему, генератор тактовой частоты и синхронную. схему разностной обработки сигнала, выполненную в виде пары. интегрирукщих цепочек, подключенных к входам симметричного дифференциального усилителя непосредственно, а к источнику сигналачерез ключи, управляющие цепи котоных подсоединены к противофаэным выходам генератора прямоугольных им пульсов тактовой частоты со скважностью, равной двум, причем выход дифференциального усилителя связан 15 со входом пороговой схемы f2).

Однако это устройство имеет недостаточную точность определения мо

:ментов запуска при априорной неопределенности относительно характерно; тик переменной составляющей, поскольку оно обеспечивает запуск интегратора при превышении скоростью изменения сигнала заданной величины, в

25 то время как наибольщую точность измерения интегральными выборками сигнала в условиях изменчивости помехи имеют алгоритмы, учитывающие моменты перехода переменной составля30 ющей через свое нулевое значение (3 и

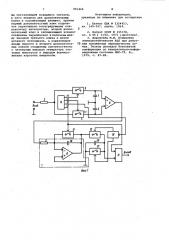

991424 тора 7, выполненного на операционном усилителе 8, резисторе 9 и интегрирующем конденсаторе 10. Цифровой интегратор, запускаемый устройством, на схеме не показан. Его пусковая цепь связана с выходом устройства, являющегося выходом нуль-органа 11, сигнальный вход которого через третий ключ 12 подсоединен к выходу интегратора 7, а управляющий вход подключен к выходу 13 генератора 14 тактовой частоты. Выход 15 генератора 14 через формирователь 16 коюотких сиг-. ,налов импульсов связан с управляющим входом ключа 12, а входы 17-18, на которых в противофазе формируются прямоугольные импульсы со скважностью, равной двум, подсоединены непосредственно к управляющим входам первого и второго ключей 5 и 4. Элементы схемы: дифференциальный усилитель б, конденсаторы 1-2, ключи 4- 5 и резистор 3 образуют схему разностной обработки исходного сигнала. Конденсатор 10 интегратора 7 эащунтирован дополнительным ключом 19, а парал. ,лельно сигнальному входу нуль-органа 11 подключен запоминающий элемент

20, эашунтированный вторым дополнительным ключом 21, причем управляющие входы ключей 19 и 21 соединены соответственно с управляющим входом нуль-органа и вторым выходом формирователя 16.

Устройство работает следующим образом.

Исходный сигнал (фиг. 2), содержащий постоянную 22 и низкочастотную переменную 23 составляющие, подается на вход устройства. Ключи 4-5 поочередно, через равные промежутки времени подают исходный сигнал на конденсаторы 2 и 1 через резистор 3.

Так как усилитель б имеет входной импеданс, во много раз превышающий суммарное сопротивление входной цепи и источника сигнала, переэаряд конденсаторов осуществляется преимущественно током через входную цепь. Постоянная составляющая входного сигнала через конечное время после включения схемы при достаточ" ной симметрии параметров входной цепи заряжает конденсаторы 1 и 2 до равных значений напряжения, являющегося синфаэным для дифференциального входа усилителя б, а потому и подавляемым на выходе этого усилителя. Текущее значение переменной . составляющей попеременно подсоединяется на время полупериода тактовой частоты к конденсаторам 1 и 2, обра- . зуя на них ступени приращения с экспоненциальными участками заряда или разряда. Форма напряжения на конденсаторе 1 (фиг, 2 .а ) показана кривой 24. Для удобства изображения, и анализа работы схемы форма напряЦель изобретения - повышение точности формирования моментов запуска в условиях априорной неопределенности относительно характеристик низкочастотной переменной составляющей исходного сигнала. 5

Поставленная цель достигается тем, что в устройство для запуска цифровых интеграторов,. содержащее симметричный дифференциальный усилитель, входы которого через первый и 10 второй ключи соединены с первым вы- водом резистора интегрирующей RCцепи, второй вывод которого является входом устройства, первый и второй конденааторы интегрирующей RCцепи включены. между соответствующим входом симметричного дифференциального усилителя и шиной нулевого по-. тенциала, генератор тактовых импульсов, первый и второй выходы которого подключены к управляющим входам первого и второго ключей, и нуль-орган, выход которого является выходом устройства, введены интегратор, выполненный на операционном усилителе, в цепь обратной связи которого включен интегрирующИй конденсатор, третий ключ и форь4 рователь коротких импульсов, причей интегратор и третий ключ соединены последовательно .и включены между выходом симметричного дифферен- З0 циальлого усилителя и сигнальным входом нуль-органа, управляющий вход третьего ключа через формирователь ко >отких импульсов соединен с третьим вы<одом генератора тактовых импуль- 350 сов, четвертый выход которого подключен к управляющему входу нуль-органа.

Кроме того, в устройство введены два дополнительных ключа и запоминающий элемент, причем первый дополни- 40 тельный ключ подключен параллельно интегрирующему конденсатору интегратора, второй дополнительный ключ и запоминающий элемент соединенй параллельно и включены между выходом 45 третьего ключа и шиной нулевого потенциала, а управляющие входы первого и второго дополнительных ключей соединены соответственно с четвертым выходом генератора тактовых импульсов и выходом формирователя коротких импульсов.

На фиг. 1 изображена функциональ ная схема устройства формирования запуска цифровых интеграторов, на фиг. 2 — эпюры напряжений в характер- 55 ных точках схемы устройства.

Устройство для запуска цифровых интеграторов (фиг. 1) содержит конденсаторы 1 и 2, образующие совместно с. резистором 3 при поочередном замы- 60 кании ключей 4 и 5 интегрирующие

RC-цепи, включенные между входом устройства и входами симметричного дифференциального усилителя 6. Выход последнего подключен к входу интегра- 65

891424 жения на конденсаторе 2 условно инвертирована, что допустимо, пос-кольку это напряжение приложено к инвертирующему входу усилителя 6.

Усилитель суммирует указанные приращения напряжения, выделяя сигнал пилообразной формы (фиг. 2 б). Огибающая этого сигнала соответствует производной исходного сигнала. При выработке генератором 14 сигналов тактовой частоты (фиг. 2 в) сигнал 10 с выхода уСилителя 6 преобразуется в сигнал на входе нуль-органа 11 фиг. 2 г) следукщим образом: проинтегрированный собранным на усилителе 8 интегратором 7 за период 15 тактовой частоты сигнал с выхода óñèëèòåëÿ 6 запоминается на.конденсаторе 20 на время длительности стро. бирующих импульсов сигнала на выходе 15 генератора 14, для чего ключи 20

1,2 и 21 замыкаются на короткое время импульсами, поступающими с формирователя 16 и соответствующими фронтам стробирующих импульсов. Длительность стробирующих импульсов, перекрывающих 5 моменты срабатывания ключей 4-5, выбирается несколько большей переходных процессов, вызываемых переключением ключа 19, и достаточной для надежного срабатывания нуль-органа 11 при поступлении с выхода 13 генератора 14 коротких тактовых импульсов.

Интегрирование сигнала, снимаемого с выхода усилителя 6 в течение отрезков времени, меньших периода тактовой частоты на половину стробирующего импульса, позволяет сформировать на сигнальном входе нуль-органа 11 импульсы, огибающая которых соответствует переменной составляющей йсходного сигнала. При этом подавляется 40 помеховая постоянная составляющая случайной величины, лежащей в диапазоне от нуля до двойной амплитуды переменной составляющей исходного сигнала, появление которой абуслов- 45 лено несовпадением момента начала восстановления сигнала с одним иэ моментов перехода переменной составляющей через нуль. В случае, когда интервал времени между подключением 50 источника исходного сигнала и моментом запуска цифрового интегратора таков,, что выбором параметров элементов схемы интегратора можно обеспечить центрирование восстанавливае мого сигнала, первый, второй, дополнительные ключи 19 и 21 и запоминающий элемент 20 с соответствующими связями не нужны, Предлагаемое устройство для запуска цифровых интеграторов позволяет повысить, точность определения моментов запуска в условиях априорной неопределенности относительно характеристики низкочастотной переменной составляющей за счет осуществ- 65 ления интегрирования с учетом моментов перехода имзкочастотной динамической составляющей исходного сигнала через нуль, остакщихся стабильными при симметричных и несимметричных искажениях формы этой составлякщей, достигающих 10ОВ. Данный эффект обеспечивает увеличение точности измерения цифровыми интегратора-. ми„ осуществлякщими осреднение исходного сигнала за период помехи, в течение фиксированного интервала времени,. расположенного симметрично относительно перехода помехи через нуль, или за два фиксированных интервала, разделенных паузой переменной длительности, на которой интегральное значение переменной составляющей сигнала равно нулю, нашедших широкое практическое применение.

Формула изобретения

1.устройство для запуска цифровых интеграторов, содержащее симметричный дифференциальный усилитель, входы которого,через первый и второй ключи соединены с первым выводом резистора интегрирукщей RC-цепи, второй вывод которого является входом устройства, первый и второй конденсаторы интегрирукщей RC-цепи включены между соответствующим входом симметричного дифференциального усилителя и шиной нулевого потенциала, генератор тактовых импульсов, первый и второй выходы которого подключены к управляющим входам первого и второго ключей, и нуль-орган, выход которого является выходом устройства, о т л и ч а ю щ e— е с я тем, что, с целью повышения точности формирования моментов за- . пуска в условиях априорной неопределенности относительно характеристик низкочастотной переменной составляющей исходного сигнала, в него введены интегратор, выполненный на операционном усилителе, третий ключ, в цепь обратной связи которого включен интегрирующий конденсатор, и формирователь коротких импульсов, причем интегратор и третий ключ соединены последовательно и включены между выходом симметричного дифферециального усилителя и сигнальным входом, нуль-органа, управляющий вход третьего ключа через формирователь коротких импульсов соединен с третьим выходом генератора тактовых импульсов, четвертый выход которого подключен к управлякщему входу нуль-органа.

2. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что, с целью повышения точности эа счет устранения влияния несимметричности фор991424 мы составляющей исходного сигнала, в него введены два дополнительных ключа и запоминающий элемент, причем первый дополнительный ключ подключен параллельно интегрирующему конденсатору интегратора, второй допол- 5 нительный ключ и запоминающий элемент соединены параллельно и включены между выходом третьего ключа и шиной нулевого потенциала, а управляющие входы первого и второго допалнитель- 10 ных ключей соединены соответственно с четвертым выходом генератора тактовых импульсов и выходом формирователя коротких импульсов.

Источники информации, принятые во внимание при экспертизе

1. Патент США 9 3354453, кл. 340-347, опубл.. 1964.

2. Патент СССР 9 315378, кл. G 06 7 1/02, 1971 (прототип .

3. Дорожовец М.М. Повышение помехоустойчивости АЦП при дейст,вии искаженных периодических помех. Тезисы докладов Всесоюзной конференции по измерительно-информационным системам ИИС-79, Л,, 1979, с. 87. — 88.

991424

С5

Составитель С. Белан

Редактор С. Патрушева ТехредT.Фанта КорректорИ. Шароши

Заказ 135/67

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

И

f7

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-"35, Раушская наб., д. 4/5