Устройство для адресации памяти микро-эвм

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Соцналнстнческнх

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свмд-ву (22) Заявлено 171 130 (21) 32471 1 1/18-24 с присоединением заявки ¹

{23) Приоритет

Опубликовано 230183.Бюллетень No

Р М К з

G 06 Г 9/34

Государственный комитет

СССР по делам изобретений и открытий (Щ УДК 681. 325 (088.8) Дата опубликования описания 2301.83 (»

В.И. Серов и С.Н. Шутова (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ

МИКРО-ЭВМ

Изобретение относится к вычислительной технике .и может быть исполь зовано в вычислительных системах на основе микро-ЭВМ для увеличения максимально адресуемого объема памяти.

Известно устройство адресации памяти микро-ЭВМ, содержащее регистр адреса, один вход которого соединен с адресной шиной центрального процессора, другой вход, с шиной сигнала синхронизации, а одиг иэ выходов с адресной шиной микро-ЭВМ, и дешифратор адреса, вход которого соединен с другим выходом регистра адреса, а выход с шиной управления микро-ЭВМ Г1).

Максимальный объем памяти этого устройства 65536 байт. В этом объеме размещаются как оперативная память, так и управляющая программа. Таким образом для оперативной .памяти может. быть выделено только 32К байт памяти, чего в ряде практических применений оказывается не достаточно.

Наиболее близким к предлагаемому по технической сущности является уст- 25„ ройство для адресации памяти в микроЭВМ, содержащее регистр информации, выходом соединенный с информационньм выходом устройства, схему И, к входам которой подключены входы тактового ЗО сигнала, сигнала .синхронизации устройства, а к выходу — управляющий вход регистра информации, информационный вход которого подключен к шине данных f2) .

В данном устройстве выделена подсистема портов ввода и подсистема пор тов вывода, подсистема оперативной памяти, подсистема стека. Это позво" ляет увеличить объем используемой оперативной памяти, однако при управлении системами отображения с большим числом индикаторных элементов (порядка 2"Я + 2 ), возникает необходимость использовать практически весь объем памяти (65536 байт) для хранения отображаемой информации. При этом объем памяти оказывается не достаточньм для хранения сложных программ обработки поступающей для отображения информации.

Цель изобретения — повышение коэф" фициента испсвльзования оборудования..

Поставленная цель достигается тем, что в устройство для адресации памяти микро-ЭВМ, содержащее регистр информации, выход которого соединен с информационным выходом устройства, первый элемент И, первый и второй входы которого соединены с тактовым и синх991427

В момент времени, когда на шину данных микро-ЭВМ помещается информация о состоянии центрального процессора (ЦП) микро-ЭВМ.при совпадении тактового сигнала и сигнала синхронизации элемент И 2 вырабатывает сигнал записи и регистр 1 информации запоминает информацию о состоянии ЦП и выда. ет ее на информационный выход устройства. Если на входы поступили сигналы Готов, Ждать и Считывание первого байта, то результат анализа первого байта команды, поступающий в это время с выхода ППЗУ 3, на буферный регистр 4 запишется при помощи сигнала записи, выработанного вторым элементом И 6. В результате этого в буферном регистре окажется записанной информация о длине в байтах выполняемой в настоящий момент

ЦП микро-ЭВМ команды. Если выполняемая команда однобайтовая, то на выходе блока 5 контроля обращений, который является управляющим выходом устройства, сигнал обращения к подсистеме программной памяти не вырабатывается. Если команда двух-или трехбайтовая, то в течение одного или двух машинных циклов ЦП микро-ЭВМ, отсчет которых ведется по тактовому сигналу и сигналу синхронизации, поступающих на блок 5 контроля обращений, последняя вырабатывает сигнал обращения к программной памяти, который выдается на управляющий выход устройства. После считывания последнего байта команды блок 5 контроля обращений вырабатывает сигнал сброса, который, поступая на буферный регистр 4, сбрасывает его. Таким образом, устройство оказывается готовым к анализу следую". щей команды. Сброс блока 5 контроля обращений и буферного регистра 4 может осуществляться и с помощью сигнала Сброс, поступакщего на блок 5 контроля обращений. Это необходимо, например, при включении устройства. ровходом устройства, введен второй элемент И, постоянное программируемое запоминающее устройство, буферный.pe"" гистр и схема контроля обращений, при этом группа информационных входов регистра информации соединена с шиной 5 данных микро-ЭВМ, управляющий вход регистра йнформации! соединен с выходом первого элемента И, группа адресных входов постоянного программируемого запоминающего устройства соедине40 на с шиной данных микро-ЭВМ, группа информационных выходов постоянного программируемого запоминающего устрой :ства соединена с группой информационных входов буферного регистра, первый 5 и второй информационные выходы которого соединены с первым и вторым информационными входами схемы контроля обращений, выход второго элемента И соединен с синхровходом буферного регистра, вход сброса которого соединен с первьм выходом схемы контроля обращений, первый, второй и третий входы второго элемента И соединены с входами Ждать, Готов, . читывание первого байта устройства соответственно, третий и четвертый входы схемы контроля обращений соединены с так. товым и синхровходом устройства соответственно, пятый вход схемы контроля обращений соединен с входом сброса устройства, второй выход схемы кон. троля обращений соединен с управляющим выходом устройства.

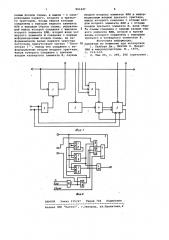

Схема контроля обращений содержит три триггера, четыре элемента И, два 356 элемента ИЛИ, причем первый и второй входы первого элеь.ента И соединены с тактовым и синхровходом схемы, à BbI ход — с первым входом второго элемента И и с первыми входами третьего и 40 четвертого элементов И,второй вход второго элемента И соединен с вторым информационным входом схемы, а выход— с синхровходами первого, второго и третьего триггеров, входы сброса которых 4» соединены с выходом первого элемента ИЛИ и выходом сброса схемы, управляющий выход которой соединен с выходом второго элемента ИЛИ, второй вход четвертого элемента И соединен с пер- О вым информационным входом схемы, на информационном входе первого триггера постоянно присутствует сигнал Ло. гическая 1, выход его соединен с информационным входом второго триггера, выход которого соединен с третьим входом четвертого элемента И, первым входом второго элемента ИЛИ и информационным входом третьего триггера, выход которого соединен с вторым входом второго элемента ИЛИ и с вторьм входом третьего элемента И, вход сброса схемы соединен с первьм входом первого элемента ИЛИ, второй и третий входы которого соединены с выходами третьего и четвертого элементов И. 65

Увеличение объема памяти достигается тем, что при обращении процессора за командой устройство вырабатывает сигнал Считывание команды, который позволяет ввести еще одну подсистему памяти для хранения программ объемом 65536 байт .

Ба фиг. 1 представлена структурная схема Устройства1 на фиг. 2 — схема контроля обращений.

Устройство содержит регистр 1 информации, первый элемент И 2,постоянное программируемое запоминающее устройство (ППЗу} 3, буферный регистр 4, блок 5 контроля обращений, второй эле. мент И 6,элемент И 7,триггеры 8, элемент И 9, первый и второй элементы

ИЛИ 10-11, элементы И 12,13.

Устройство работает следующим образом.

991427

Таким образом, сигнал считывания первого байта команды дополняется сигналом обращения к программной памяти, который вырабатывается при считывании второго и третьего байтов команды. Совокупность этих сигналов позволяет легко выделить подсистему программной памяти. Причем большой ее обьем 65К байт позволяет в некоторых случаях значительно облегчить программирование. Ю

Блок 5 контроля обращений представляет собой простой цифровой автомат, один из вариантов функциональной схеу4ы которого приведен на фиг. 2.

ППЗУ 3 практически может быть pea- )$ лиэована на одной микросхеме К556РЕ4.

ППЗУ (анализатор команд) и блок 5 контроля обращений работают следукицим образом.

В момент считывания центральными 20 процессором с шины данных кода команды на выходах программируемого постоянного запоминающего устройства 3 (ППЗУ) появляются сигналы, соответствующие той команде, код которой нахо- 25 дится в это время на шике данных.

ППЗУ программируется так, что если команда однобайтовая, то сигналы отсутствуют на выходах, если команда двухбайтовая, то появляется сигнал на выходе младшего разряда, если команда 30 трехбайтовая, то сигналы появляются и на выходе старшего разряда и на.вы,ходе младшего разряда . Таким образом, в момент считывания первого байта команды в буферный регистр 4 оказывает- З5 ся записанньм код, содержащий информацию о том будет ли центральный процессор микро-ЭВИ считывать второй и третий байты команды или нет. Если команда однобайтовая, то синхроимпульсы 40 с выхода элемента И 9 не пройдут на синхровходы триггеров 8 и автомат останется в исходном состоянии. Если команда двух- или трехбайтовая, то после приема информации в регистр 4 4 происходит запись единицы в первый триггер 8. Таким образом, при считывании второго байта команды синхросигнал с выхода элемента И 9 поступит снова на синхровходы триггеров 8. и 9Озапишет единицу во второй триггер 8При считывании третьего байта, если команда двухбайтовая, то синхросигнал пройдет через элемент 11 и сбросит все триггеры блока контроля обращений 55

8, а также регистр 4, если команда двухбайтовая, то сброса не произойдет, в третий триггер 8 запищется единица, а сброс триггеров произойдет через элементы И 12-13 и элемент ИЛИ 11 при,О поступлении четвертого синхросигнала.

Сигналы с выхода второго и третьего триггеров B через элемент ИЛИ .10 подаются на управляющий выход устройства и означают, что центральный процессор считывает второй нли третий байты команды. Сброс всех триггеров может быть произведен также общим сигналом Сброс через элемент ИЛИ 11.

Таким образом, введение указанных элементов повышает коэффициент использования оборудования, что позволит удвоить максимально используемый объем оперативкой памяти микро-ЭВИ.

Формула изобретения

1. Устройство для адресации памя ти микро-ЭВИ, содержащее регистр информации, выход которого соединен с информационньи выходом устройства, ервый элемент И, первый к второй входы которого соединены соответственно с тактовиь| входом и синхровходом устройства, о т л и ч а ю щ е е с я тем, . что, с целью повьааенкя коэффициента использования оборудования, в устройство введен второй элемент И, постоянное программируемое запоминающее устройство, буферный регистр к блок контроля обращений, при этом группа информационных входов регистра информации соединена с входом данных устройства, управляющий вход регистра информации соединен с выходом первого элемента

И, группа адресных входов постоянного программируемого запоминающего устройства соединена с входом данных устройства, группа информационных выходов постоянного программируемого запоминающего устройства соединена с группой информационных входов буферного регистра, первый и второй информационные выходы которого соединены с первьае и вторыми информационными входами блока контроля обращений, выход второго элемента И соединен с синхрО входом буферного регистра, вход сбро- . са которого соединен с первым выходОм блока контроля обращений, первый, второй и третий входы второго элемента

И соединены с входами Ждать, Готов, Считывание первого байта устройства соответственно, третий и четвертый входы блока контроля обращений соединены с тактовьм и синхро-. входом устройства соответственно, пятый вход блока контроля обращений соединен с входом сброса устройства, второй выход блока контроля обращений соединен с управляющим выходом устрой-. ства.

2. Устройство но п. 1, о т л и ч а ю щ е е с я тем, что блок контроля обращений содержит три триггера, четыре элемента И, два элемента ИЛИ, причем первый и второй входы первого элемента И соединены с тактовьм и синхровходом схемы, а выход — с первым входом второго элемента И и с первьми входами третьего и четвертого элементов И, второй вход второго элемента И соединен с вторяк информаци991427

ВНИИПИ Заказ 135/67 Тираж 704 Подписное

Филиал ППП "Патент", г.ужгород, ул.Проектная,4 онньм входом схемы, а выход — с синхровходами первого, второго и третьего триггеров, входы сброса которых соединены с выходом первого элемента

ИЛИ и выходом сброса схемы, управляющий выход которой соединен с выходом второго элемента ИЛИ, второй вход чет. вертого элемента И соединен с первич информационным входом схемы, на информационном входе первого триггера постоянно присутствует сигнал Логи- !О ческая 1, выход его соединен с информационным входом второго триггера, выход которого соединен с третьим входом четвертого элемента И, первым входом второго элемента ИЛИ и информационньм входом третьего триггера, выход которого соединен с вторьм входом второго элемента ИЛИ и с вторьм входом третьего элемента И, вход сброса схемы соединен с первым входом пер. вого элемента ИЛИ, второй и третий входы которого соединены с выходами третьего и четвертого элементов И.

Источники информации, принятые во внимание при экспертизе

1. Хилбурн Дж., Джулич П. МикроЭВМ и микропроцессоры. М., 1979, с. 312-314.

2. Там же, с. 295, 296 (прототип),