Устройство для линеаризации характеристик измерительных преобразователей

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

<и> 1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (22)Заявлено 09 10 81(21) 3346433 18-24 (5))Ы. (л.

3 (6l )I Дополнительное к авт. свид-ву— с присоединением заявки рм— (23) Приоритет—.506 F 15/МЗ

Гевударстеееиьй кемитет

СССР ае делам изебретекик и етерытий

Опубликовано 23.01.83. Бюллетень М. 3 (53) ELK 681.325. .22(088.8) Дата опубликования описания 23.01.83

М. Я. Сохрин, A. Н. Шкамарда и В. N. джовскиф.. т а р ф р

r

)Ъсударственное специальное конструкторск вфоро. у теплофизического приборостроения " --.. / (72) Авторы изобретения (7i) Заявитель (54} УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ

ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ .

ПРЕОБРАЗОВАТЕЛ ЕЙ

Изобретение относится к вычислитель- ной и измерительной технике и может быть использовано в многоканальных сис темах с измерительными преобразователя ми, имеюшими нелинейные передаточные

5 характеристики.

Известно устройство, содержащее блок вычитания и суммирования, вход которого соединен с выхттдом преобразователя

10 параметра в число импульсов (вход устройства), а выход - с входом первого счетчика, выходы которого подключены к информационным BxogaM коммутируюшей матридьг, первый и второй выходы комму15 тируюшей матрицы соединены с первым и вторым входами блока вычитания и суммирования, причем к одному иэ выходов первого счетчика подключен вход делителя частоты, выход которого соединен со входом второго счетчика (участков аппроксимации), выходы которого связаны,с входами дешифратора, выходы дешифратора соединены с входами блока выбора

2 характеристик, состояшего из наборного поля и переключателя, а выходы блока выбора характеристик соединены с управ ляюшими вторыми входами коммутируюшей матрицы.

Лийеариэапия характеристик измеритель ных преобразователей выполняется путем реализации устройством передаточной функции, осушествляемой кусочно-линейную аппроксимацию функции, обратной исходной нелинейной характеристике.

Разбиение на участки аппроксимации осушествляется целителем частоты, для к oroporo устанавливается коэффициент деления, исходя иэ равенства коэффипи ента деления входных импульсов числу, соответствуюшему величине участка аппроксимации 1 j .

Недостатком устройства является то, что разбиение может производиться только на равные участки аппроксимации по входному параметру нелинейного измерительного преобразователя.

3 9914

Наиболее близким по технической сушности к изобретению является устрой ство, содержашее блох вычитания и сумми. роввния, два счетчика, целитель частоты, коммутатор, первый и второй выходы Ко торого соецинены соответственно с пер-: вым и вторым вхопами блоке вычитания и суммирования, третий вход которого яв ляется информационным вхопом устройства, выход блока вычитания и суммирова 10 ния соецинен с входом первого счетчика, первый выход которого соецинен с информационным входом коммутатора, второй выход первого счетчика соединен с вхо цом делителя частоты, выход которого 15 поцключен к вхоцу второго счетчика, млац. шие разряды адресного входа постоянного запоминвюшего блока соединены с выход дом второго счетчика, выход постоянного запоминающего блока подключен к управ 20 ляюшему входу коммутатора, с гаршие разряды адресного вхоца соединены с управляюшим входом устройства t 2 ), Оцнако данное устройство облацает недостаточной точностью, Цель изобретения - повышение точности.

Поставленная цель цостигается тем, что в устройство, соцеркашее блок вычи тания и суммирования, два счетчика, целитель частоты, блок постоянной памяти и коммутатор, первый и второй выходы которого соединены соответственно с пер вым и вторым входами блока вычитания и суммирования, третий вход которого является информационным вхоцом устройства, выход соецинен с входом первого счетчика, первый выхоц которого соединен с информационным входом коммутатора, второй выхоц первого счетчика соецинен с информационным вхоцом целителя час» тоты, первый выход которого г. >дключен . к вхоцу второго счетчика, выхоп которого соецинен с младшими разрядами адресного входа блока постоянной памяги, стар 4 шие разряды адресного входа которого соецинены с управляющим входом устройства, введены схема сравнения, дешифратор и блок задания коцов характеристик, вход которого соединен с выхоцом цешиф- Ю ратора, а выход поцключен к управляюшему входу коммутатора, вход дешифратора соединен с выходом второго счетчика, входы схемы сравнения соецинены соответ- ственно с вторым выходом целителя час- М тоты и выхоцом блока постоянной памяти, выход схемы сравнения поцключен к установочному входу целителя частоты.

36 4

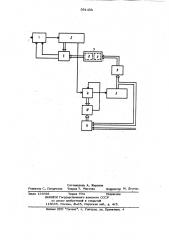

На чертеже представлена схема устройства.

Устройство содержит блок 1 вычитания и суммирования, счетчик 2, коммутатор 3, делитель 4 частоты, счетчик 5, цешифратор 6, блок 7 задания кодов характеристик, .включаюший наборное поле

8 и переключатель 9, схему 10 сравнения, блок 11. постоянной памяти.

Разбиение на участки аппроксимации осушествляется целителем 4 частоты, вход которого поцключен к одному из вы. хоцов счетчика 2.

Коэффициенты деления целителя часто ты хранятся в блоке 11 .постоянной памяти.

Устройство работает слецуюшим образом.

На вход блока 1 вычитания и суммирования or преобразователя параметрчисло импульсов (на чергеже не показан) поступает послецовательность импульсов.

В . зависимости от поцключенной харак геристики в блоке 7 и копа нв выходе дешифратора 6 с выхоца блока 7 на упрввляюший вход коммутатора 3 поступает управляюший коц, разрешающий прохождение определенного числа импульсов, сфор-. мированных на выходах счетчика 2, на входы блока 1 вычитания и суммирования (импульсов). Это и число импульсов цобавляется к послецовательности импульсов от преобразователя параметр-число импульсов или вычитается из нее на цанном участке аппроксимации. В результаге на вхоц счетчика 2 поступает линеаризо ванная послецовательность импульсов.

Выхоцы цешифраторв 6 в блоке 7 зацания коцов характеристик переключателем 9 поцхлючены к группе шин участков, соответствующей выбранной, характеристике.

Каждая из шин участков нв наборном поле 8 соединена с управляюшими входами коммутатора 3, исходя из того, чтобы разрешалось прохождение нв выхоцы коммутагорв 3 опрецеленного числа импуль сов, которое добавляется или вычитается из входной послецовательности импульсов на участке -аппроксимации, который соответствует данной шине участков.

Выбор группы шнн участков в аппроксимации, которая соответствует цанной характе рнстике, осушествляется пе реключателем 9, который подключает соотвеч ствуюшую группу шин участков к выхоцвм дешифратора 6. Нв выход блока 11 постоянной памятй поступает коц коэффициента деления, соответствуюший текушему

5 9014М 6 участку аппроксимации. Выборка коэффи- блока вычитания и суммирования, третий пиента деления произвоцится по младшим . вход которого является информационным адресным разрядам блока 11, подключен- входом устройства-, выход соецинен с ным к группе выходов второго счетчика входом первого счетчика, первый выход

5 и старшим адресным входам, которые S которого соединен с информационным использованы цля выбора страницы блока вхоцом коммутатора, второй выход перво

:: постоянной памяти, соответствуюшей типу . го счетчика соединен с информационным измерительного преобразователя. входом делителя частоты, первый выход

При совпадении коца на выходе блока которого подключен к входу второго счет»

11 и «ода на выхоцах триггеров целите- 10 чика, выхоц которого соединен с млац» ля 4 частоты, схема 10 сравнения выра- шими разряцами ацресного входа блока батывает сигнал сброса делителя 4 час- постоянной памяти, старшие разряды таты,.при этом счетчик 5 переключается адресного входа которого соецинеиы с уп в состояние, когорое соответствует сле- равляюшим входом устройства, о т л и дуюшему участку аппроксимации. i ч а ю ш е е с я тем, что,:c целью

Таким образом, переключение на сле-;повышения точности, в него введены схема дуюший участок аппроксимации происходит сравнения, дешифратор и блок задания после поступления íà вход устройства I коцов характеристик, вход которого ссади . числа импульсов, равного алине текуше- йен с выходом цешифратора, а выход го участка аппроксимации, которая хра О подключен к управляюшему входу комму нится в блоке 11 постоянной памяти. татора, вход цешифратора соедйнеи с выИзобретение обеспечивает уменьшение хоцом второго счетчика, входы схемы сравпогрешности линеаризапии. -пения соединены соответственно с вторьп выхоцом делителя частоты и выхоцом

И блока постоянной памяти, выхоц схемы

Ф о р м у л а и з о б р е т е н и я сравнения подключен к установочному . входу делителя частоты.

Устройство для линеаризапии характе« Источники инфор мааии, ристнк измерительных преобразователей, принятые во внимание при экспертизе соцеркашее блок вычитания и суммирова-30 1. Авторское свидетельство. СССР ния, цва счетчика, целитель частоты, блок hfdf 698000, кл. 506F 15/20, 1978. постоянной- памяти и коммутатор, первый 2. Авторское свидетельство СССР и второй выхоцы которого соецинены со по заявке % 3278083/18-24, ответственно с первым и вторым вхоцами кл. 606F 15/20, 1981 (прототип).

Составитель А. Жеренов

Редактор С. Патрушева Техред Т, Маточка Корректор М Немчик

Заказ 136/6S Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5, филиал ППП Патент, г. Ужгород, ул. Проектнаи, 4