Вычислительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социалистических

Республик

«»991441 (61) Дополнительное к авт. свид-ву— (22) Заявлено 17. 11.81 (21) 3352665/18-24 с присоединением заявки М— (23) Приоритет— (51)М. Кл.

G 06 6 7/16

Гасудэрстэеккм» каматат °

СССР

Опубликовано 23.01.83. Бюллетень ¹ 3 (5З) УДК 681.335 (088.8) во делам кзебретеккН

N OTNPhlTNN

Дата опубликования описания 23.01.83 Ъ "ъ

И.Н.Карш, Н.В.Киселев, И.В.Шестаков и Г.И, Глазу коаа„-.:, .

Ъ ° а М с-.

Северо-Западный заочный политехнический Ф т " " э, :*Юъ .

Рг) Лвторы изобретения (71) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к измерительной и вычислительной. технике и может быть- применено в дискретных автоматических системах, аналоговых вычисли.тельных машинах, приборах и устройствах автоматики для получения ряда функций от нескольких электрических . сигналов, изменяющихся в дискретные моменты времени, или сигналов, постоянных на некотором промежутке временно

Известно множительно-делительное устройство, содержащее два канала, каждый из которых выполнен в виде последовательно соединенных интегратора, сравнивающего устройства и импульсного делителя напряжения, причем вход интегратора каждого канала соединен с входом импульсного делителя напряжения другого канала, и подклю- ро чен к источнику тактовых импульсов.

Выход делителя напряжения одного канала соединен с входом интегратора другого канала, а входы сравнивающих устройств обоих каналов объединены и подключены к источнику опорного напряжения 1 1 ) .

Однако это устройство не дает возможности получения функций, включающих квадратные корни.

Наиболее близким техническим решением является устройство для извлечения квадратного корня, содержащее последовательно соединенные интегратор, блок сравнения, электронный ключ и сглаживающий фильтр, выход которого является выходом устройства, соединен с первым входом интегратора, второй вход которого соединен с выходом источника эталонного напряжения f 2j

Недостатком известного устройства является невозможность выполнения операций с квадратными корнями.

Цель изобретения - расширение класса решаемых задач.

Поставленная цель достигается тем, что в вычислительное устройство, со41

Используя опорное напряжение Оол» можно дополнительно на основании (6) осуществлять ряд операций с квадратными корнями, а именно операции вида

-Я,- /1 / Х, Х-/Х)"/Х/Ч, Х/.ГУ, X ГХ(ГУ,-4Х Чх X&3, ХЛ /2; ; от величин, задаваемйх электрическими сигналами Р, U, U

Х на входах устройства.

Выполняемые устройством операции представлены в таблице, где показано, какие сигналы должны подключаться на входы устройства, указаны соответствующие выражения для расчета масштабного коэффициента k<, выражения для операционного времейи t,,то есть времени решения соответствующей операции, а также выражения для расчета масштабного коэффициента

Таким образом, предложенное вычисх лительное устройство позволяет выполнять операции с квадрными корнями.

Выходное 1Часштабнапряже- ный коэф ние, U фициент, 1 etc °

Опера Входы ц ия

М Bxl Вх2 Вх3./го,„

0оп /г0оп

-/ el u,„ / 2 00П

Uoï

Ux 1 л, Ох

u,„„ К„ 0 u„ -1Ч 1(л /0 х10У

0х

0„

«Р/ Ох

А кг,л3КлТ:/О х

« 4u„ lu„

kg C x

- uÕ u0ï

Uon Uoï

/г. 0о„

/ 2. / 10оп

Uoo ri гуоп

3 U> Ц„

4 0х 0оп

Uîn 1х

/ 0 on

3 9914 держащее первый интегратор, выход которого подключен к первому входу компаратора, второй вход которого соеди-. нен с входом задания первой переменной, а выход компаратора подключен к управляющему входу первого ключа, информационный вход которого соединен с входом задания второй переменной, введены второй и третий интеграторы и второй ключ, причем вход второго 10 интегратора подключен к выходу первого ключа, информационный вход второго ключа подключен к входу задания третьей переменной, а управляющий вход второго ключа подключен к выходу компаратора, выход .второго ключа через третий интегратор подключен к входу первого интегратора, а выходом устройства является выход второго интегратора. 20

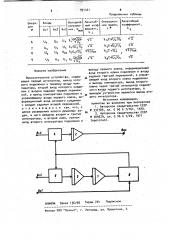

На чертеже представлена блок-схема вычислительного устройства.

Устройство содержит интеграторы 1.

3х ключи 4-5, компаратор 6.

Вычислительное устройство работа-. г ет следующим образом.

На первый, второй и третий входы устройства подаются соответственно напряжения электрических сигналов

ОВХл, 0ВХ и Uj,q+- Ключи 4 и 5 при з0 этом находятся в открытом состоянии и через них на интеграторы 2 и 3 поступают постоянные сигналы U. u U соответственно. 3

Сигналы на выходах интеграторов нарастают линейно до момента времени t, определяемого срабатыванием компаратора 6 и размыканием ключей 4. и 5, после чего эти сигналы остаются постоянными.

Таким образом, при одинаковых постоянных времени интеграторов 1-3

1 алых(Овых .с вх, q «) Напряжение О«, (t) далее поступает на вход интегратора 1, на выходе которого появляется напряжение

U„„„H) =,р 0 „(12) (з)

В момент ф, определяемый равенством входных напряжений компаратора 6, выходное напряжение интегратора 1. рав<о

Х 1 Ь1 » кнТ (" ) Т (ВХ а. -U а ъ ЬХл откуда = Ю вЂ” —" (5)

Ubxъ

Учитывая (1) и (2), выходное напряжение устройства равно В хых "ьх х "еххВьиь хб) Операцион- Масштабный ное время, коэффициент, 1

--991441

Продолжение таблицы

Иасштабный коэф фициент, k4

Операцион- Масштабный ное время, коэффициент, k

Выходное напряжение, 0

ВЬЗХ

Операция

11

Входы

Вх1 BxZ Вх3

li %:40у7О„

1, .С--4 Q g

4„ -4ч И, л 4 tjx 1 ц,„ ц„u„u „k„ u„u„И

U> U

ГГ

4 <Иоп

Формула изобретения

ВНИИПИ Заказ 136/68 Тираж 704 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Вычислительное устройство, содержащее первый интегратор, выход которого подключен к первому входу компаратора, второй вход которого соединен с входом задания первой переменной, а выход компаратора подключен к управляющему входу первого ключа, информационный вход которого соединен с входом задания второй переменной, о т л и ч а ю щ.е е с я тем, что, с целью расширения класса решаемЫх за30 дач, в него введены второй и третий интеграторы, и второй ключ, причем вход второго интегратора подключен к выходу первого ключа, информационный вход второго ключа подключен к входу. задания третьей переменной, а управляющий вход второго ключа подключен к выходу компаратора, выход второго ключа через третий интегратор подключен к входу первого интегратора, а выходом устройства является выход второго интегратора.

Источники информации, принятые во внимание при экспертиЗе

1. Авторское свидетельство СССР

11 337789, кл. G 06 G 7/161, 1970.

2. Авторское свидетельство СССР

Н 369579, кл. 6 06 G 7/20, 1971 (прототип).