Адресный формирователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

{61)Дополнительное к авт. свид-ву(22) Заявлено 220681 (21) 3303935/18-24 с присоединением заявки Нов (23) Приоритет— (И1 М. Кд.з

G 11 С 8/00

Государственный комитет

СССР

flo делам изобретений и открытий (53) УДК 681. 327 (088.8) Опубликовано 23,0183. Бюллетень Йо 3

Дата опубликования описания 2501,83

А.С. Лушников, A.Á. Однолько, И.П. Лазаренк и Ю;В,.Яинков-, 1 :,; . г (72).Авторы изобретения (71) Заявитель (54 ) АДРЕС НЫН ФОРМИРОВАТЕЛЬ

Изобретение относится к запоминаю щим устройствам и может быть исполь-., зовано при создании БИС на МДП-транзисторах.

Известны адресные формирователи, содержащие триггер-фиксатор на десяти транзисторах с выходными и управляющими шинами и два транзистора разбаланса, соединенные с входной шиной и шиной опорного потенциала (1).

Недостатками данных адресных формирователей являются низкая надежность и большое потребление мощности в статическом режиме.

Наиболее близким техническим решением к изобретению является адресный формирователь, содержащий триггер-фиксатор на десяти транзисторах, .три конденсатора, одиннадцатый и двенадцатый транзисторы разбаланса, тринадцатый, четырнадцатый и пятнадцатый отсекающие транзисторы, причем истоки первого, второго, третьего, четвертого, одиннадцатого и двенадцатого транзисторов соединены с общей шиной, затворы пятого и седьмого транзисторов соединены с истоком шестого и стоком первого транзисторов, затворы восьмого и десятого транзисторов соединены с истоком девятого и стоком четвертого транзистора, зат-. воры первого и второго транзисторов соединены со стоками одиннадцатого и третьего транзисторов и истоком восьмого, затворы третьего и четвертого транзисторов соединены со стоками второго и двенадцатого транзисторов и истоком седьмого, стоки седьМОГО и ВОсьмОГО транзистОрОв СОеди иены с первой управляющей шиной, стси ки пятого и десятого транзисторов соединены с третьей управляющей шиной, затворы шестого и девятого транзисторов соединены со второй управляющей шиной, а их стоки - с шиной питания, исток пятого транзистора соединен с выходной шиной прямого адресного сигнала, исток десятого транзистора соединен с выходной шиной инверсного адресного сигнала, затвор одиннадцатого транзистора соединен с первой обкладкой первого конденсатора и стоком четырнадцатого ,транзистора, затвор двенадцатого транзистора соединен с первой обкладкой второго конденсатора и стоком пятнадцатого транзистора, вторые обкладки первого и второго конденсаторов соединены с четвертой управллюЗО щей шиной; затворы тринадцатого, че"

991504

20 тырнадцатого и пятнадцатого транзисторов соединены с пятой управляющей шиной, истоки четырнадцатого и тринадцатого транзисторов соединены с первой обкладкой третьего конденсатора, вторая обкладка третьего конден- 5 сатора соединена с шиной питания, исток пятнадцатого транзистора соединен с шиной опорного потенциала, сток тринадцатого транзистора — с входной адресной шиной t». 30

Недостатком этого формирователя является то, что он потребляет большую мощность во включенном состоянии, так как присутствуют цепи прохождения активного тока от первой уп- 15 равляющей шины через седьмой и двенадцатый транзистор, либо через восьмой и одиннадцатый транзисторы.

Целью изобретения является снижение потребляемой формирователем мощности

Поставленная цель достигается тем, что в адресный формирователь, содержащий МДП-транзисторы, причем стоки и затворы первого и второго переклю- 25 чающих транэисторон соединены по триггерной схеме, истоки первого и второго транзисторов обратной связи подключены соответственно к стокам первого и второго переключающих тран 30 зисторов, истоки которых и истоки входного, опорного, первого и второго управляющих транзисторов соединены с шиной нулевого потенциала; затворы первого и второго переключающих тран- 35 эисторов подключены соответственно к затворам первого и второго управляющих транзисторов, стоки которых соединены соответственно с истоками первого и второго нагрузочных транзисторов, стоки которых подключены к шине питания, стоки первого и второго транзисторов обратной связи объединены и являются первым управляющим входом формирователя, а затворы подключены соответственно к стоку первого и затвору третьего. управляющих транзисторов и к стоку второго и затвору четвертого управляющих .транзисторов., затвор опорного транзистора соединен с шиной опорного напряжения, затвор входного транзистора является первым адресным входом формирователя, вторым адресным входом и выходом которого являются соответственно истоки третьего и четвертого управляю-55 щих транзисторов, стоки которых и затворы первого и второго нагрузочных транзисторов являются соответственно вторым и третьим управляющими входами формирователя, ннедены третий и четвер-4Е тый транзисторы обратной связи, истоки которых подключены соответственно к стоку входного транзистора и к стоку опорного транзистора, затворы— соответственно к стокам первогo и 65 второго управляющих транэисторон, а стоки - соответственно к затворам первого и второго переключающих транзисторов.

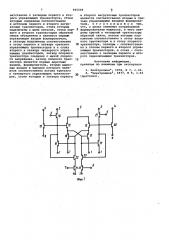

На фиг.1 приведена принципиальная схема предложенного формирователя, на фиг.2 — временные диаграммы, поясняющие его работу.

На фиг.1 обозначены шина 1 нулевого потенциала, шина 2 питания первый

3, второй 4 и третий 5 управляющие входы формирователя, шина 6 опорного напряжения, первый 7 и второй 8 адресные входы формирователи и выход 9 формирователя.

Предложенный адресный формирователь содержит (фиг.1) первый 10 и второй 11 переключающие транзисторы, первый 12 и второй 13 транзисторы обратной связи, входной 14 транзистор, опорный 15 транзистор,,перный 16 и второй 17 управляющие транзисторы, первый нагрузочный транзистор 18, третий 19 и четвертый 20 упранляющие транзисторы, второй нагрузочный транзистор 21, третий 22 и четвертый, 23 транзисторы обратной сняэи.

На фиг.2 изображены временные диаграммы напряжений U, Ug и . 0 соответственно на первом, втором и третьем управляющих входах формирователя и напряжения 0 на первом адресном входе формирователя.

Параметры транзистора 10 (фиг.1) выбираются равными параметрам транзистора 11, параметры транэисторон

12 и 13, 19 и 20, 18 и 21, 16 и 17, 22 и 23, 14 и 15 также попарно равны между собой.

Предложенный адресный формирователь работает следующим образом.

В исходном состоянии напряжение на входах 3 и 4 равно нулю, на входе

5 - высокое напряжение, равное, либо превышающее напряжение на шине

2 питания. Пусть напряжение на входе 5 равно напряжению на шине питания U>, тогда в исходном состоянии затворы транзисторов 12 и 13 будут заряжены до напряжения (U -,/. ), где

V — пороговое напряжение ИДП-транТ зистора. Через открытые транзисторы 19,20, 12 и 13 напряжение на входе 8 и входе 9 и на затворах транзисторов 10 и 11 установится ранним на» пряжению на входах 4 и 3 соответственно, т.е. будет равно нулю. Напряжение на шине 6 опорного напряжения постоянно и равно полусумме напряжений логического нуля и единицы на входе 7. Для пранильной работы адресного формирователя напряжение на шине опорного напряжения должно превышать пороговое напряжение

МДП-транзистора.

Напряжение на входе 7 должно уста новиться равным уровню ногине -.кого

991504

Формула изобретения

6$ нуля, либо единицы до появления высокого напряже ния на входе 3. Пусть, например, на входе 7 имеет место низкое напряжение, соответствующее логическому нулю.

В момент времени t (ôèã.2) на входе 3 (фиг.1) появляется импульс .напряжения, и. напряжение на входе

5 в этот момент уменьшается до нуля. Через открытые транзисторы 12 и 13 затворы транзисторов 11 и 10 заряжаются, а через транзисторы 23, 15 и 22, 14 разряжаются.

При равных токах заряда затворов транзисторов 10 и 11 ток разряда затвора транзистора 11 больше тока разряда затвора транзистора 10, так как на затворе транзистора 15 напряжение больше, чем на затворе транзистора 14, и транзистор 15 имеет большую проводимость. Поэтому затвор транзистора 10 заряжается быстрее до напряжения, больше порогового >)т, чем затвор транзистора 11.

При этом открытый транзистор 10 увеличивает ток разряда затвора транзистора 11, открытый транзистор 16 разряжает затворы транзисторов 12 и 22, уменьшая тем самым так заряда транзистора 11 и ток разряда зат вора. транзистора 10. К триггерной по» . ложительной обратной связи между тран зисторами 10 и 11 прибавляется положительная обратная связь, охваты>вающая транзисторы 22 и 23, что ускоряет процесс переключения. Разница напряжений на затворах транзисторов

10 и 11 лавинообразно нарастает. В конце процесса переключения напряжение ка затворах транзисторов 10 и 13 соответствует высокому уровню, на затворах транзисторов 11 и 12 напря>кение равно кулю. В момент времени (Фиг.2) подается импульс напря><ения на вход 4. Так как транзистор

7.

19 (фиг.1) закрыт, а транзистор 20 открыт, то через открытый транзистор

20 выход 9 заряжается до напряжения входа 4. Напряжение на входе 7 уже в момент времени t< (фиг.2) может иметь произвольное значение, не влияя на работу адресного формирователя, так как транзистор 22 (фиг.1) закрыт, и прохождение тока по цепи вход 3 — транзистор 13 — транзистор

22 - транзистор 14 — шина 1 исключается.

В момент времени (Фиг.2) напряжение на входах 3 и 4 уменьшается до нуля, а на входе 5 возрастает до

U, Адресный формирователь переходит в исходное состояние.

При высоком логическом уровне на входе 7 в момент времени t (фиг.2) затвор транзистора 11 (фиг.1) заряжается быстрее затвора транзистора

10, так как проводимость транзистора

15 меньше проводимости транзистора

14. По цепям положительной обратной связи через затворы транзисторов 11, 13 и 23 разница напряжений на затворах транзисторов 10 и 11 усиливается. В конце процесса переключения (фиг.2) напряжение на затворах транзисторов 11 и 12 (фиг.1) соответствует высокоиу уровню, а на затворах транзисторов 10 и 13 равно нулю.

Так как транзисторы 10,13 и 23

>0:çàêðûTû, то прохождение тока в цепи вход 3 — шина 1 исключается. Смена логического уровня на входе 7 (фиг.2) также не влияет на работу адресного формирователя, так как нулеь<>е напря15 жение на затворе транзистора 10 (фиг.1) удерживается транзистором 11 °

С приходом импульса на вход 4 в момент времени t< (фиг.2) напряжение на выходе 9 остается равным ну2р лю, а на входе 8 увеличивается до напряжения на входе 4.

Итак, введение транзисторов 22 и 23 позволяет снизить мощность, потребляемую адресным формирователем

25 в включенном состояния по цепи вход

3 — транзистор 12 — транзистор 23 транзистор 15 — шина 1, либо по цени вход 3 — транзистор 13 — транзистор 22 — транзистор 14 - шина 1, так как после срабатывания адресного формирователя один из транзисторов в каждой нэ пар 12 и 23, 13 и 22 оказывается закрытым.

При этом предложенный формирователь имеет малое время удержания на. пряжения на входе 7 на истинном логическом уровне, как и известный

Кроме того, транзисторы 22 и 23 образуют дополнительную положительную обратную связь, ускоряющую процесс переключения предложенного адресного Формирователя, что увеличивает его быстродействие.

Технико-экономическое преимущество предложенного адресного формирователя заключается в том, что он потребляет меньшую мощность, чем известный, при высоком быстродействии.

Адресный формирователь, содержащий МДП-транзисторы, причем стоки и затворы первого и второго переключающих транзисторов соединены по триггерной схеме, истоки первого и второго транзисторов обратной связи подключены соответственно к стокам *ервого и второго переключаккаих транзисторов, истоки которых и истоки входного, опорного, первого и второго управляющих транзисторов соединены с шиной нулевого потенциала, затворы первого и второго переключающих транзисторов подключены соот991504 ветственно к затворам первого и второго управляющих транзисторов, стоки которых соединены соответственно е истоками первого и второго нагрузочных транзисторов, стоки которых подключены к,шине питания, стоки первого и второго транзисторов обратной связи объединены и являются первым управляющим входом формирователя, а затворы подключены соответственно к стоку первого и затвору третьего управляющих транзисторов и к стоку второго и затвору четвертого управляющих транзисторов, затвор опорного транзистора соединен с шиной опорного напряжения, затвор входного транзистора является первым адресным входом, формирователя, вторым адресным входом и выходом которого являются соответственно истоки третьего и четвертого управляющих транзисторов,. стоки которых и затворы первого и второго нагрузочных транзисторов являются соответственно вторым и треч тьим управляющими входами формирователя, отличающийся тем, что, с целью снижения потребляемой

5 формирователем мощности, в него введены третий и четвертый транзисторы обратной связи, истоки которых подключены соответственно к стоку входного транзистора и к стоку опорного

10 транзистора, затворы — соответственно к стокам первого и второго управляющих транзисторов, .а стоки - соответственно к затворам первого и второго переключакиаих транзисторов.

Источники информации, принятые во внимание при экспертизе

1. Электроника", 1978, 9 7, с.36.

2. "Электроника", 1977, 9 9, с.52 (прототип).

991504

ФИГ

Составитель Т. Зайцева

Редактор В. Данко Техред М.Гергель Корректор E. Рошко .

Заказ 14б/71 Тираж 592 Подписное

ВННИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

М °

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4