Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

rui991564 (61) Дополнительное к авт. свид-ву 9 905962 (22) Заявлено 12.02;81(21) 3245277/24-07

Р1) М. Кл.з сприсоединениемзаявки ¹ (23) Приоритет

Опубликовано 23 01.83. Бюллетень Йо 3

Н 02 И 7/48

Государствеииый комитет

СССР ро декам изобретеиий и открытий ($3) УДК 621 314. .572 (088 ° 8) Дата опубликования описания 23.01.83

В.И. Сенько, В.C. Смирнов, Ю.К. Торопчинов Ь,*Р() н В,A. Сиариепа I . ""чХ :рр у . а / ..,р.т.. . c I

Кпеаскиа ордена Ленина политехнические нн ; тут;::;, :." - / им. 50-летия Великой Октябрьской социалистически„ революций а (72) Авторы изобретения (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ

В МНОГОСТУПЕНЧАТОЕ КВАЗИСИНУСОИДАЛЬНОЕ

Изобретение относится к электротехнике, в частности к преобразовательной технике, и может быть использовано в преобразовательных установках (ПЗУ) с квазисинусоидальным вы5 ходным напряжением для стабилизирован. ного прецизионного электропривода.

По основному авт. св. Р 905962 известно устройство, содержащее суммирующий и инверторный блоки с управляемыми ключевыми элементами, по.следовательно соединенные измерительный выпрямитель, аналого-цифровой блок, цифровой сумматоо-вычитатель и блок управления суммируницим блоком, выходы которого соединены с управляющими входами инверторного блока и вторыми входами цифрового сумматора-вычитателя f,1).

К недостаткам укаэанной схемы следует о нести то, что на ее выходе обеспечивается стабильное, но не регулируемое напряжение. Величина выходного напряжения однозначно определяется кодом, вырабатываеьйм блоком управления. Этот код жестко записан в ПЗУ и однозначно определяет амплитуду и форму выходного на пряжения. В целом же ряде устройств, и в первую очередь в злектроприводе> возникает необходимость,регулирования амплитуды напряжения, что затруднительно при использовании данной схема.

Целью изобретения является регу« лирование выходного напряжения при его повышенном качестве.

Поставленная цель достигается тем, что преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное, содержащий последовательно соединенные суммирующий и инверторный блоки с управляеьхями ключевыми элементами, последователь" но соединенные измерительный выпрямитель, входом подключенный к выходу инверторного блока, аналого-цнфровой блок и цифровой сумматор- вычитатель, выходы которого связаны с управляющими входами соответствующих ключевых элементов суммирующего блока, причем суммирующий блок выполнен в виде последовательно соединенных по выходу силовых ячеек, каждая as которых представляет собой замкнутую ° цепь as последовательно включенных источника напряжения и двух ключевых элементов, силовые электроды одного из которых образуют выходы ячейки, снабжен сдвигающим блокам, выполнен991564 образом.

Квазинусоидальное напряжение с выхода инвертора 2 после выпрямления схемой 4 поступает на вход аналого-цифрового блока 5, где преобразуется в двоичный многоразрядный код (. Код (соответствует величине реального выходного напряжения. Од.новременно на выходе блзка 1 управления формируется двоичный многоразрядный код Х, который сдвигающим блоком 7 делится на величину, кратную 2", т. е. 1,2,4,8 и т.д. Так, на

55 ным, например, в виде сдвигающего регистра с входами параллельной и последовательной з аписи, а также з адатчиком уровня выходного напряжения причем входы параллельной записи сдвигающего блока поразрядно соединены с выходами блока управления ключевыми элементами, к его входу последовательной записи подключен выход задатчика уровня выходного напряжения, а выходы этого блока поразряд-10 но соединены со вторыми входами цифрового сумматора-вычитателя.

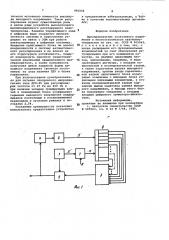

На фиг. 1 представлена функциональ. ная блок-схема преобразователя; на фиг. 2 — пример реализации блока управления; на фиг. 3 — пример выполнения схемы сравнения кодов; на фиг. 4 — пример реализации цифрового сумматора-вычитателя; на фиг. 5 пример реализации сдвигающего блока. функциональная блок-схема преобразователя (фиг. 1) содержит блок 1 управления, один из выходов которого связан с управляющими входами инверторного блока 2, силовой суммирующий блок 3, выход которого соединен с силовым входом инвертора 2, последовательно соединенные выпрямитель 4, аналого-цифровой блок 5 и цифровой сумматор-вычитатель б, вторые входы которого соединены с выходами сдвигающего блока 7, а выходы — со входами силового суммирующего блока 3, причем вход выпрямителя 4 соединен с выходом инвертора 2, а входы сдвигающего блока 7 — с выходами блока l управления. Регулирующим входом служит вход последовательной записи.

Выход инвертора 2 является выходом преобразователя.

На цифровом выходе X блока 1 уп- 40 равления формируется двоичный параллельный многоразрядный код, в любой момент времени соответствующий величине аппроксимированной синусоиды.

На цифровом выходе Е сдвигающего уст ройства 7 формируется двоичный парал лельный многоразрядный код, сдзину— тый по отношению к коду числа Х на число разрядов, равное регулирующему воздействию 8, что равнозначно делению числа Х на 2, где 8- целое число, равное 1,2,...,n.

Преобразователь работает следующим пример, если 8. 1, X=Z, если 9=2, Х = Е/2 и т.д. Таким образом, на выходе сдвигающего блока 7 формируется код числа, определяющий амплитуду выходного напряжения, причем. величину этого напряжения можно легко изменять в соответствии с законом 2 " . Действительно, коды чисел g и Е поступают на входы цифрового сумматоравычитателя б, который реализует one2Х рацию 2Z — (или

На его выходе формируется код, управляющий ключевыми элементами суммирующего блока . Например, при увеличении питающего напряжения, т.е при увеличении выходного напряжения, код g превысит,код Z на величину Q-Z.

Таким образом, для поддержания выходного напряжения неизменным и соответствующим величине Е необходимо из кода Z вычесть Q-Z т.е.

Z — (g-Е) =2Е-g

При уменьшении выходного напряжения код g будет меньше кода Z на величину Z-g т. е. для стабилизации необходимо к коду Z прибавить Е-g

Z+ (Z-$) =2Z-g

Таким образом, цифровой сумматорвычитатель, реализующий операцию

Z+Z-$=2Z-g будучи установленным в цепи отрицательной обратной связи, обеспечивает стабилизацию выходного напряжения заданного кодом числа Z, а код числа Z под воздействием регулирующего параметра В может изменяться в кратное 2- раз, т.е., изменяя 9, можно регулировать величину выходного напряжения ступенчато в

2 " раз.

Для более ясного представления о работе преобразоват еля целе со об разно рассмотреть работу блока 1 управления (фиг. 2) .

Блок 1 управления осуществляет формирование сигналов управления работой силовых ключеЙ суммирующего блока 3 и инвертора 2 в виде двоичного параллельного многоразрядного кода. Блок управления включает задающий генератор 8, счетчик 9 длительностиступеней, посто янное запоминающее устройство (ПЗУ)

10, реверсивный счетчик 11 управления ключами сумматора, триггер 12 управления реверсивным счетчиком, триггер 13 управления работой инвертора, схему 14 сравнения кодов, а также схемы И, ИЛИ, НЕ, необходимые для функционирования блока управления. ПЗУ 10 содержит числа, записанные в двоичном коде которые соответствуют длительностям ступеней выходного квазисинусоидального напряжения, Работу axeman удобнее рассматривать, начиная с момента времени, когда в счетчиках 9 и ll записаны

9915б4 нули, а триггер 12 находится в состоянии 1 . При этом на выходе ПЗУ установлен код, выбираемый по адресу 0 и соответствующий длительности нулевой ступени. С выхода генератора на счетный вход счетчика 9 непре- рывно поступают импульсы опорной частоты. При наборе в счетчике 9 кода (А, В ...А,,В„„ - фиг. 3), соответствующего длительности первой ступени, сигнал с выхода схемы 14 сравнения кодов через открытую схему 15 совпадения поступает на суммирующий ,вход реверсивного счетчика 11 . При этом изменяется его состояние на еди-ницу. Кроме того, обнуляется счетчик

9; Изменение состояния счетчика ll вызывает изменение информации на выI ходе ПЗУ, которая теперь соответствует длительности первой ступени, а также вызывает включение источника U в сумматоре 3.

Счетчик 9 длительности ступеней повторно заполняется импульсами генератора 8 до момента, пока не произойдет набор кода, соответствующего длительности первой ступени, поступающего с ПЗУ.

Аналогичным образом происходит формирование управляющего кода реверсивного счетчика 11 для всех по следующих ступеней первой четверти периода, за исключением верхней ступени. В ПЗУ записывается число, соответствующее половине длительности верхней ступени. При наборе этого кода в счетчике 9 импульс со схемы

14 сравнения переполняет реверсивный счетчик 11 (его состояние обнуляется).

Импульс переполнения счетчика 11 с выхода - Р опрокидывает триггер

12 и задним фронтом через сборку lб вычитает единицу из счетчика. Таким образом, после формирования первой пени, импульс с выхода схемы 14 сравного напряжения достаточно изменить

65 код величины этого напряжения и пракполовины верхней ступени выход схем сравнения оказывается подключенным к вычитающему входу счетчика 11, а. его состояние — TIE...Г, т.е. с выхода ПЗУ подается код, соответствующий длительности половины верхней ступени.

При наборе в счетчике 9 кода, соответствующего половине верхней стунения поступает на вычитающий вход счетчика 11 и уменьшает его состояние на единицу и т,д.

При переходе счетчика 11 через 0 прои .ходит опрокидывание триггеров 12 и 13 и аналогично формируется отрицательная полуволна выходного напряжения. Триггер 13 предназначен для управления работой ключей инвертора 2.

На фиг. 3 представлен вариант исполнения схемы сравнения кодов раэ- рядностью М с поразрядным сравнением.

На фиг. 4 представлен пример схемной реализации цифрового сумматоравычитателя б. Для выполнения операции 2Z-g код Z подается (в виде сиг5 налов Е,, Q, Z>,Z4 — фиг 4) на входы схемы со сдвигом влево на один разряд, что соответствует умножению кода Z на два, а код 7 поступает на входы сумматоров с инверсией (g, 9, (@ — фиг. 4),что соответствует 0 вычитанию кода У. При этом на один из входов сумматора младшего разряда необходимо подавать сигнал логической 1 .Сдвигающий блок 7 может быть вы15 полнен либо в виде сдвигаюЯего регистра, на вход параллельной записи которого в параллельном коде поступает управляющий код с выхода счетчика 11 (фиг. 2) и сдвигается на

2() число разрядов, задаваемое сигналом управления 6, подаваемым на сдвига ющий вход, либо в любой другой реализации.

В этом случае сдвигающий блок включает счетчик 17, аналогичный счетчику 11 (фиг. 2), и такую же схему управления на логических элементах 1821. Входами этой схемы служат логические входы а,б,в,г соответствующих точек блока управления (фиг ° 2).Сдвиг

"управляющего сигнала на число разрядов соответствующее сигналу управления б, осуществляется за счет деления частоты импульсов сигнала а на линейке триггеров 22. Этот сигнал преобразуется в последовательности импульсов с частотой 2 f0r 21 10,...2 1 и через логические схемы совпадения и сборку ИЛИ поступает на управление счетчика lб в виде а . В зависимости от значения 9, которое также может принимать значение 2, 2 ....2 о . в

3 частота а соответственно уменьшается в Р, 2".... 2 раз. A это равнозначно сдвигу управляющего сигнала на

45 такое же число разрядов.

Предлагаемое устройство практичес" ки не требует времени ° на преобразование кода управляющего сигнала, в то время как введение сдвигающего ре5О гибтра требует синхронизирующих им-.

;пульсов, генератора и время о нача,ле для записи параллельного кода, а затем для его сдвига.

Технико-экономический эффект от использования предлагаемого устройства состоит в следующем. Использование новых блоков и связей выгодно отличает предлагаемый преобразователь от известного, так как обеспечивает воэможность регулирования выходного напряжения при его повышенном качестве .

Дня ступенчатого изменения выход991564

Формула изобретения тически мгновенно изменм1 ся амплиту.да выходного напряжения. Такое регулирование играет существенную роль в целом ряде устройств высокоточного малоинерционного регулируемого электропривода. Задание управляющего кода в цифровом виде сохраняет высокую точность системы и существенно упрощает ее связь с ЭВМ при работе электропривода в цифровых системах.

Введение сдвигающего блока не вносит 10 инерционности в систему автоматического регулирования и не влияет на

его структурную устойчивость. Следует подчеркнуть простоту схемотехнической реализации предлагаемого пре- t5 образователя, а также возможность получения любой заданной формы выходного напряжения (включая постоянное) за счет, наличия ПЗУ в блоке управления. 20

При использовании преобразователя для питания синхронного микродвигателя типа ДСП-25 при регулировании .частоты от,25 Гц до 400 Гц и при наличии четырех суммирующих клю- щ5 чей s суммирующем блоке коэффициент гармоник выходного напряжения поддерживался постоянным в установившемся переходном и пусковом режимах и составлял 2,53.

Указанные преимущества позволяют использовать предлагаемое устройство

8 в прецизионном эЛектроприводе, а также в качестве исполнительных органовАСУ.

Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное по авт. св. СССР 9 905962, отличающий с я тем, что, с целью расширения его функциональных возможностей за счет обеспечения регулирования при его повышенном качестве, он снабжен сдвигающим блоком, выполненным, например, в виде сдвигающего регистра, с входами параллельной и последовательной записи, а также задатчиком уровня выходного напряжения, причем входы параллельной записи сдвигающего блока поразрядно соединены с выходами блока управления ключевыми элементами, к его входу последовательной записи подключен выход задатчика уровня выходного напряжения, а выходы этого блока поразрядно соединены с вторыми входами цифрового сумматора-вычитателя .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 905962, кл. Н 02 М 7/48, 1980.

991564

Составит ель Г, Мыцык

Редактор Н. Пушненкова Техред Т.Маточка Корректор М, Демчик

Заказ 160/74 Тираж 685 Подпи сН ое

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4