Преобразователь двоичного кода угла в двоично-десятичный код градусов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ki>9932 43

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву(22) Заявлено 190681 (21) 3315379/18-24 с присоединением заявки М— (23) Приоритет—

Опубликовано 30.01.83. Бюллетень М 4

Р М g+ з.

806 % 5/02

Государственный комитет

СССР во делам нзобретеннй н открытнй (53) УДК 681. 3 25 (088.8) Дата опубликования описания 3о-0183 (72) Авторы изобретения

Е .Ф. Киселев и О.A. Кузина

k ( (7t) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА УГЛА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД ГРАДУСОВ

Изобретение относится к автомати- ке и вычислительной технике и может: быть использовано в устройствах ото-.. бражения информации импульсной метеорологической радиолокационной станции.

Известен преобразователь двоич ного кода в двоично-десятичный, со.держащий двоичный счетчик, двоичнодесятичный счетчик, генератор импульсов и элемент И f1 ).

Недостаток известного преобразователя состоит в низком быстродействии и сравнительно большом обьеме аппаратуры. .Наиболее близким по технической сущности к предлагаемому является преобразователь двоичного кода в двоично десятичный, содержащий двоичный счетчик, двоично-десятичный счетчик, счетчики коррекции, причем информационный вход преобразователя соединен с информационным входом преобра= эователя, а выходи.двоично-десятичного счетчика являются выходами преобразователя g2).

Недостаток известного преобразователя состоит в низком быстродей-ствии

Цель изобретения — повышение быстродействия.

Поставленная цель достигается за счет того, что в преобразователь двоичного кода угла в двоично-десятичный код градусов, содержащий двоичный счетчик, счетчик коррекции, двончнодесятичный счетчик, выходы которого являются выходами преобразователя, информационные входы младших разрядов которого соединены с информационными входами двоичного счетчика, введены сумматор, блок памяти, первый и второй коммутаторы и блок управления, тактовый вход которого является тактовым входом преобразователя, вход запуска которого соединен с входами разрешения приема двоичного и двоично-десятичного счетчиков, с входом сброса счетчика коррекции и входом запуска блока управления, тактовый выход которого соединен со счетно входом счетчика коррекции с первым информационным входом перво2> го коммутатора, первый и второй выходы которого соединены соответственно с входами сложения и вычита-. ния двоичного счетчика, выходы переполнения и заема которого соединены соответственно с первым н вторым

993243 входами сброса блока управления, выход запуска которого соединен с вторым информационным входом первого коммутатора, управляющий вход которого соединен с выходом,старшего . разряда двоичного счетчйка, с входом переноса сумматора и с управляющим входом второго коммутатора, информационный вход которого соединен с выходом счетчика коррекции, а первый и второй выходы второго коммутатора соединены соответственно с входами сложения и вычитания двоично-деся тичного счетчика, информационный вход которого соединен с выходом блока памяти, входы младших разрядов и вход старшего разряда которого . соединены. соответственно с выходами . суммы и выходом переноса сумматора, первая группа входов которого соединена с информационными входами старших разрядов преобразователя, вход логического нуля которого соединен . с второй группой входов сумматора.

Блок управления содержит триггер, элемент задержки, элемент И-ИЛИ, элемент И и элемент ИЛИ, первый и второй входы которого являются соответственно первым и вторым входами сброса блока управления, вход запуска которого соединен с первым входом элемента И-ИЛИ с входом элемента задержки, выход которого является выходом запуска блока управления и соединен с третьим входом элемента

ИЛИ и вторым входом элемента И-ИЛИ, выход которого соединен с R-входом триггера, С-вход которого соединен с выходом элемента ИЛИ, а выход триггера соединен с первыььвходом элемента И, второй вход которого является тактовым входом блока управ ления, а выход элемента ii является тактовым выходом блока управления, второй вход сбРоса которого соединен с третьим входом элемента И-ИЛИ.

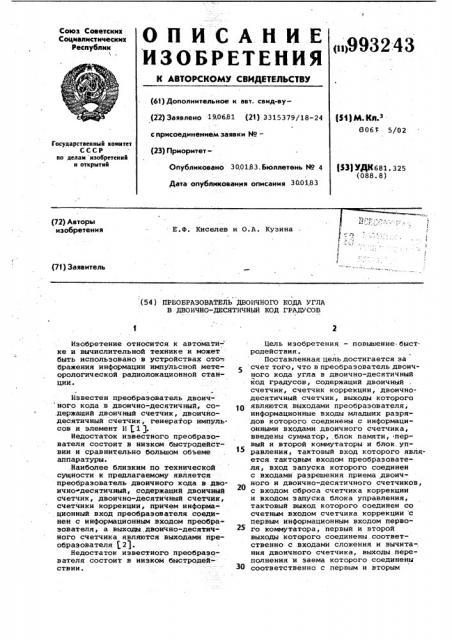

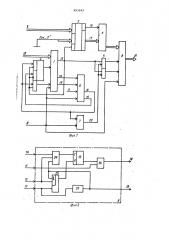

На фиг. 1 приведена стр-. ктурная схема преобразователя двоичного кода угла в двоично-десятичный код градусов; на фиг. 2 — блок-схема блока управления; на фиг. 3 - схема счетчика коррекции.

На фиг. 1 использованы следующие обозначения: двоичный счетчик 1, сумматор 2, блок 3 памяти, коммутаторы 4 и 5, блок 6 управления, счетчик 7 коррекции, двоично-десятичный счетчик 8, входы 9 старших разрядов кода угла, входы 10 младших разрядов кода угла, тактовый вход 11, вход

12 запуска, выход 13 старшего разряда счетчика 1, выходы 14 и 15 переполнений счетчика 1, выход 16 переноса сумматора 2, выход 17 кода суммы сумматора 2, выходы 18 и 19 блока управления, выход 20 счетчика коррекции и кодовый выход 21 двоично-десятичного счетчика 8. Блок 6

Преобразование производится путем запрещения поступления на выход

20 каждого восьмого, импульса Ч1 К 9 поскольку за время развертки кода

9 до максимального значения,,определяемого 2 = 2 =128 квантами должно быть выдано 112 импульсов двоично-десятичного число-импульсного кода.

Блок 6 управления предназначен .для формирования последовательности сигналов, синхронизирующих работу преобразователя во времени. управления (фиг. 2) содержит триггер 22, элемент 23 задержки, элемент

ИЛИ 24, элемент И-ИЛИ 25, элемент, И 26. Счетчик коррекции 7 (фиг. 3) содержит счетчик 27, элементы И 28 и 29.

Преобразователь работает следующим образОм.

Преобразователь выполняет преобразование двоичного п-разрядного

10 кода угла 7. в. двоично-десятичный л код р градусов.

При л-12 вес кванта двоичного ко- да равен hoL360 /2" 360О/21 5 16", а вес двоично-десятичного кода выбран

6У 0 1о

Для преобразования код а4 разделен на две части л л л

Т+ ю

А и

d. 1 d." 2.

1= 1

20 где ф = + Yj " 6i = Г д Я» коды

)и „ р--1=1 образованные m старшими и р=(п-m)

25 младшими разрядами кода соответственно;

d„., "„, g„. — разрядные цифры кодов

Д,, Ф, в.

Предлагаемый преобразователь

30 (фиг. 1) реализован для п-12, m-4.

На вход 11 преобразователя поступают тактовые импульсы ТИ11, на вход 12 - импульсы И 12.запуска, .а на входы 9 и 10 — коды и g со-. ответственно.

Блок 3 памяти вырабатывает двоично-десятичный код ф (ф") по коду +, формируемому сумматором 2 на основе соотношения

40 Р=. +,,- . „

I где e< — разрядная цифра старшего разряда кода ф

Счетчик 7 преобразует число-импульсный код ЧИК g» двоичного кода Д», определяемого соотношением е =4- В„ч((-e)e„(ö в двоично-десятичный число-импульс. ный код таким образом, чтобы цена каждого импульса была равна О, 1 .

993243

45

Перед началом цикла преобразования преобразователь содержит инфор-. мацию предыдущего цикла.

Цикл преобразования начинается с приходом импульса И 12 запуска, по которому в счетчики 1 и 8 заносятся коды

9 и Ф(") соответственно, триггер 22 и счетчик 27 устанавливаются в нулевое состояние-, на выходе 19 через формируется импульс,И 19.

С окончанием И 19 триггер 22 10 переходит в единичное состояние и разрешает прохождение ТИ11 на выход 18. ЧИК 4» с выхода 18 через коммутатор .4 поступает в счетчик 1 на вычитание при &» = 0 (на сложение при 9„ =1), а через счетчик 7 коррекции и коммутатор 5 - в счетчик 8 на сложение при 9 =0 (на вычитание прн 9» =1).

С окОнчанием импульса И 15 переполнения счетчика 1 в минус импульса И 14 переполнения в плюс поступление ТИ11 запрещается, а в счетчике

8 находится исковаай .код

При переполнении счетчика 1 в минус происходит -отработка преобразователем.лишнего такта преобразования, коррекция -которого производится предварительно по И 19.

Из описанного выше следует, что длительность цикла преобразования.. может быть определена выражением (4)

Дительность цикла преобразования прототипа определяется выражением с и

Т„РаФ, 2 (S) .

Сравнивая (4-) и (5), получаем оценку и м т -Угч- т т.е. для m-4

=2 =M О)

Таким образом, предлагаемое ycT-: ройство обладает более высоким бйст родействием. формула изобретения

1. Преобразователь двоичного кода угла в двоично-десятичный код градусов, содержащий двоичный счетчик, счетчик коррекции, двоично-десятич-ный счетчик, выходы которого являются выходами преобразователя, информационные входы младших разрядов которого соединены с информационными входами двоичного счетчика, .о т.л. и ч а ю шийся тем, что, с целью повышения быстродействия, в --: ® него введены сумматор, блок памяти, первый и второй коммутаторы и блок управления, тактовый вход которого является тактовым входом преобразова-. теля, вход запуска которого соединен 65 с входами разрешения приема двоичного и двончно-десятичного счетчиков с входом сброса счетчика коррекции и входом запуска блока управления, тактовый выход которого соединен со счетным входом счетчика коррекции и первым информационным входом первого коммутатора, первый и второй выходы которого соединены соответственно с входами сложения и вычитания двоичного счетчика, выходы переполнения и заема которого. соединены соответственно с первым н 1вторым входами сброса блока управления, выход запуска -которого соединен с вторым информационным входом первого коммутатора, управляющий-вход которого соединен с выходом старшего разряда двоичного счетчика, с входом переноса сумматора н с управляющим входом второго коммутатора, информационный вход которого соединен с выходом счетчика коррекции-, а первый и второй выходы второго коммутатора соединены соответственно с входами сложения и вычитания двоично-десятичного счетчика, информационный вход которого соединен с-выходом блока памяти, входы младших разрядов и вход старшего разряда которого соединены соответственно с выходами суюы и выходом переноса сумматора, первая группа входов которого соединена с информационными входами старших разрядов преобразователя,, вход логического нуля которого соединен с второй группой входов сумматора.

2. Преобразователь, о т л ич а ю шийся тем, что в нем-блокуправления содержит триггер, элемент, задержки, элемент И-ИЛИ, элемент И и элемент ИЛИ, первый и второй входы которого являются соответственно первым и вторым входами сброса блока управления, вход запуска которогс соединен с первым входом элемента

И-ИЛИ и входом элемента задержки, выход которого является выходом запуска блока управления и соединен с третьим входом элемента ИЛИ и вторым входом элемента И-ИЛИ, выход которого соединен с 4-входом триггера, С-вход которого соединен с выходом элемента ИЛИ, а выход, триггера соединен с первым входом элемента И, второй вход которого является.тактовым входом блока управления, а выход элемента И является тактовым выходом блока управления; второй вход сброса которого соединен с третьим входом элемента H-ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. АвтОрское Свидетельство СССР

9 756403, кл. G 06 Г 5/02, 1978.

2 ° Авторское свидетельство СССР

9 760084, кл. 6 06С 5/02, 1976.

993243

Составитель M. варшавский

Texyeä T.Фанта Корректор И.Шулла

Редактор С. Юско

Тираж 704 Подписное

;ВНИЙПИ Государственного комитета СССР по делам изобретений и открытий

113035,-Москва, Ж-35, Раушская наб., д. 4/5

Заказ 479/65

Филиал ППП "Патент", г. ужгород, ул. Проектная, 4