Программируемая логическая матрица

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (uj993246

Союз Советских

Социалистических

Республик (е1) Дополнительное к авт. саид-ву(22) Заявлено 1908.81 (21) 3328482/18-24

РЦИ.Кн.

606 Т 7/00 с присоединением заявки N9—

Государственный комитет

СССР по делам изобретений н открытий (23) Прморитет—

133) УДК 681.327 (088 ° 8) Опубликовано 300183. Бюллетень М 4 .Дата опубликования описания 300183 (72) Авторы изобретения Б..П. Качков, Б.Г. Лыснков и Н.М. Митюхина f" =-:

Ы

1 (71) Заявитель (54 ) ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА

Изобретение относится к вычисли тельной технике -и может использоваться в вычислительных устройствах и приборах цифровой автоматики для микропрограмм, кодопреобразования и реализации управляющих, арифмети-ческих и логических комбинационных устройств.

Известно устройство, содержащее матрицу элементов -И, матрицу элемен. тов. ИЛИ, регистры масок, блоки прерывания избыточных связей и инверторы f1).

Недостатком этого устройства является сложность организации арифметических операций.Наиболее близким техническим решением к предлагаемому является программируемая логическая матрица, содержащая подматрицу формирования логических произведений,-подматрицу формирования выходных слов и блок инвертирования входных переменных (2).

Недостатки известного устройства состоят в ограниченных функциональ-ных воэможностях вследствие сложности выполнения операции сложения .и невозможности построения на его основе многоразрядного сумматора.

Цель изобретения — расширение функциональных возможностей программируемой логической матрицы путем выполнения в ней арифметических операций .

Поставленная цель достигается тем, что в программируемую логическую матрицу, содержащую элементы НЕ, 1п:матрицу элементов И и матрицу элемен. тов ИЛИ, выходы которой являются одними из выходов программируемой логической матрицы, а входы подключены к,выходам матрицы элементов И, входы которой соединены с выходами элементов НЕ, введены логический блок и блок местного управления, выходы которого подключены к одним из входов логического блока, другие входы которого соединены с одними из входов блока местного управления и являются информационными входаМи программируемой логической матрицы, управляющими входами которой являются другие входы блока местного управления, выходы логического блока подключены к входам элементов НЕ и являются другими выходами программируемой логической матрицы.

ЛогичЕский блок содержит элементы ЮШ и элементы И, причем первые

993246

t0 входы первого и второго элементов

-ИЛИ и первого и второго элементов И являются одними из входов блока, другими входами и выходами которого являются соответственно вторые входы и выходы первого и второго элементов ИЛИ и первого и второго элементов И.

Блок местного управления содержит третий и четвертый элементы И, третий и четвертый элементы ИЛИ и триггер, единичный выход которого соединен с первыми входами третьего и четвертого элементов ИЛИ, а нулевой . выход — с первыми входами третьего и четвертого элементов И, вторые входы и выходы третьего и четвертого элементов ИЛИ и третьего и четвертого элементов И являются соответственно одними из входов и выходами блока, другими входами которого являются входы триггера.

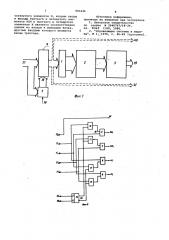

На фиг. 1 изображена структурная схема предлагаемой программируемой логической матрицыр на фиг. 2 функциональные схемы первого варианта выполнения логического блока и блока местного управления; на фиг. 3функциональные схемы одного из вариантов выполнения матрицы элементов

И и матрицы элементов ИЛИ; на фиг. 4функциональная схема второго варианта выполнения логического блока и блока местного управления.

Программируемая логическая матрица (фиг. 1) содержит элементы НЕ 1, матрицу 2 элементов И, матрицу 3 элементов ИЛИ, логический блок 4 и блок 5 местного управления. Логический блок содержит (фиг. 2) первый б и второй 7 элементы Н, первый 8 и второй 9 элементы ИЙИ. Блок местно. го управления содержит (фиг. 2) третий 10 и четвертый 11 элементы

ИЛИ, третий 12 и четвертый 13 элементы И и триггер 14.

На фиг. 3 изображены элементы HE

15-19, матрица элементов H 20-31 с пятью входами и двенадцатью выхода. ми и матрица элементов ИЛИ 32-34 с двенадцатью входами и тремя выходами.

На фиг. 1, фиг. 2 и фиг. 3 обозначены единичный выход триггера 35, один из входов 36 логического блока,. информационные 37 и управляющие

38 входы программируемой логической матрицы, выходы 39, 39, 39, 40 и 41 программируемой логической матрицы и выход 42 переноса блока местного управления.

Во втором варианте выполнения (фиг. 4) логический блок содержит элементы И 43 и 44 и элементы ИЛИ

45 и 46, а блок местного управления отсутствует.

Программируемая логическая матрица (ПЛМ) работает следующим образом.

Она реализует логические функции, представленные в дизъюнктивной нормальной форме (ДНФ). Блок 4 (фиг. 1 и фиг. 2) работает в двух режимах: в, режиме реализации сложения и режиме реализации ДНФ произвольной функции.

В первом режиме он предназначен для выработки вспомогательных функций

t;„а; Ь„» р„-ц„чЬ„, где а,.1 ; — цифры слагаемых в 1. -м разряде.

В рассматриваемом случае "-X1t 51=-X2., 4 -х, Ъ = х4, Ц„=Х,Х ;,=ХьХ

Р = Х1чХ g РгХ фХ4

Для выполнения первого режима на входы блока 4 набор входных переменных x -x> подается дважды: с входов 37 и с выходов блока 5.

Переменная х@-С „(где СВХ- сигнал входного. переноса) проходит через блок 4 без изменений. Во втором режиме блок 4 предназначен для простой передачи входных переменных х -х4. В этом случае на него поступает только один набор переменных хл -х@ с входов 37. С выхо. дов 36 блока 5 поступает константа

1100, причем единицы поступают на вторые входы элементов И б и 7, а нули — на вторые входы элементов

ИЛИ 8 и 9 (фиг. 2). В результате этого блок 4 осуществляет передачу всех входных переменных без изменений.

Блок-5 (фиг. 1 и 2) предназначен для задания в ПЛМ двух вышеуказанных реЯЬмов (режима реализации сложения и режима реализации ДНФ произвольной функции). Управляющий сигнал с входа 38 переводит триггер 14 в состояние "1", а все устройство переводит в режим реализации ДНФ произвольной функции. Управляющий сигнал на входе 38 переводит триггер 14 в состояние "0", а все устройство— в режим реализации сложения.

Сигнал с единичного выхода 35 триггера 14 подается на входы„элементов ИЛИ 10 и 11. Сигнал с нулевого выхода триггера 14 подается на входы элементов И 12 и 13. Матрица 2 элементов И 20-31 (фиг. 1 и 3) и матрица 3 элементов ИЛИ 32-34 предназначены соответственно для формирования логических произведений и формирования выходных слов (для определенности и удобства рассмотрения они запрограммированы для выполнения однотактного сложения двух разрядных частей двоичных слов). Программирование условно показано обрывом входных цепей у матриц 2 и 3. При этсм

993246 (фиг. 4), отличается только тем, что на входы 36 подаются в зависимости от режима работы либо одна из входных переменных х -х4, либо константа (0,1) от внешнего источника сигналов.

Таким образом, введение в ПЛМ логического блока 4 (фиг. 1) и блока 5 позволяют выполнять в ней операции сложения и реализовать на ее основе многоразрядные одноконтактные сумматоры.

Технико-экономическое преимущество предлагаемой программируемой логической матрицы заключается в ее более широких функциональных возможностях по сравнению с прототипом, Формула изобретения

1. Программируемая логическая матрица, содержащая элементы НЕ, матрицу элементов И и матрицу элементов ИЛИ, выходы которой являются одними,из выходов программируемой логической матрицы, а входы подключены к выходам матрицы элементов И, входы которой соединены с выходами элементов НЕ, о т л и ч а ю щ ая с я тем, что, с целью расиирения функциональных воз2южностей программируемой логической матрицы путем выполнения в ней арифметических операций, в нее введены логической блок и блок местного управления, выходы которого подключены к одним из входов логического блока, другие входы которого соединены с одними из входов блока местного управления и являются информационными входами про- ° граммируемой логической матрицы, управляющими входами которой являются другие входы блока местного управления, выходы логического блока подключены к входам элементов НЕ и являются другими выходами программируемой логической матрицы.

2. Матрица по п. 1, о т л ич а ю щ а я с я тем, что логический блок содержит элементы ИЛИ и элементы И, причем первые входы первогЬ и второго элементов ИЛИ и первого и второго элементов И являются одними из входов блока, другими входами и выходами которого являются соответственно вторые входы и выходы первого и второго элементов ИЛИ и первого и второго элементов И.

3. Матрица по пп. 1 и 2, о тл и ч а ю щ а я с я тем, что блок местного управления содержит третий и четвертый элементы И, третий и четвертый элементы ИЛИ и триггер, единичный выход которого соединен с первыми входами третьего и четвертого элементов ИЛ22, а нулевой выход — с первыми входами третьего и

Работа ПЛМ с использованием Второго варианта выполнения блока 4 65 метод прерывания связей не имеет значения для описания сущности пред лагаемого изобретения (связи могут прерываться как при помощи пережигания, так н при помощи электронных переключателей) . 5

Если ПЛМ-работает в режиме реализации ДНФ произвольной функции триггер 14 (фиг. 2) устанавливается в состояние "1", т.е. на его прямом выходе "1", а на инверсном выходе "0".

:В этом случае на входе элемента

NI22 10 появляетея "1",и, следовательно, на выходе элемента ЙЛИ 10 генерируется "1", которая подается на вход элемента И 6, на выходе котоРого появляется х, так как хз1 = х .

Так как сигнал прямого выхода триггера 14 подается также на вход элемента ИЛИ 11, на выходе элемента

И 7 появляется у .!Инверсный выход триггера 14 Q a0 подается на вход элемента И 12, на выходе которого появляется "0", который далее подается на вход элемента ИЛИ 8, на выходе которого появится х (х v 0 = x )

Так как сигнал с инверсного выхода триггера 14 подается также иа вход элемента И 13, на выходе элемента ИЛИ 9 появляется х, так как х ч О а х .

Таким образом, в этом режиме на 30 выходе блока 4 (фиг. 1 и 2) генерируются входные переменные х -х .. о

Если ILlIM работает в режиме реализации сЛожения, то триггер 14 устанавливается в состояние "0", т.е. 35 на его прямом выходе Q О, а на инверсном выходе Ц =1. В этом случае на выходах элемен= тов И 6 и 7 генерируются функции ,, 6.2 и 6,"2, соответственно, а на вщсо- 40 дах элементов ИЛИ 8 и 9 функции Р и Р соответственно.

Таким образом в этом режиме на выходе блока 4 генерируются функции

Р2 Р которые далее Вмес» 45 те с входным переносом СЭ22подаются на входы элементов НЕ (фиг. 3).

Далее элементы НЕ, матрица элементов И 2 и матрица элементов ИЛИ 3 реализуют ДНФ функции от аргуМентов (Gq, G Р, Р, С®, ), т.е. функции

50 (1),,(2) и (3) .

Таким образом, программируемая логическая матрица реализует логические функции.

Функции, описывающие сумматор с 55 аппаратно-логическим ускорением

5,9„p„e ч Ь„Сеч Р Со, (2) 6<= G

60 ч Ь,а,ч с ð, сэч «p,Ü,, ñ„qz)

С sbn G1+Рд.ф„ щ(, 993246

Г ф I четвертого элементов И, вторые входы и выходы третьего и четвертого эле- ментов ИЛИ и третьего и четвертого элементов И являются соответственно одними из входов и выходами блока, другими входами которого являются входы триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство по заявке Р 2940747/18-24, кл. б 06 F 7/00, 1980.

5 2. "Управляющие системы и маши" ны", 9 1, 1976, с. 46-49 (прототип).

993246

Составитель Т. Зайцева

Техред Т.Фанта

Корректор И. Шулла

Редактор С. Юско

Тираж 704 Подписное

ВНИИПИ Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 47 9/6 5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4