Комбинационный сумматор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советским

Социалистическим

Республик (1993253 (бт) Дополнительное к авт. свид-ву (22) Заявлено 06.08. 81 (21) 3323805/18-24 ($q) + gg з с присоединением заявки ИоС 06 F 7/50

Государственный комитет

СССР оо делам изобретений н открытий (23) Приоритетг

Опубликовано 3Q0L83 ° Бюллетень Йо 4

РЗ) УДК 681. 325..5(088.8) Дата опубликования описания 30.01.83.*

Ió (.

A. A.» Сорокин, Л. A. Мондрус, и В. В. Кореваев (72) Авторы изобретения (71) Заявитель (54 ) КОМБИНАЦИОННЫЙ CVNMATOP

Изобретение относится к вычислительной технике: и может быть исполь зовано в йроцессорах ЭВМ.

Известен сумматор, который кроме операции сложения выполняет и логи-ческие операции, обеспечивающие контроль операции сложения по четности., В случае, когда происходит ошибка в формировании переноса в любом раз-: ряде, соответствующие элементы схемы сумматора формируют ошибку и в разряде.суммы. Это позволяет в дальнейшеМ обнаружить ошибку в формировании переноса при контроле по четности -раз.. рядного сумматора 1)..

Недостатком сумматора является сложная схема, содержащая большое количество логических элементов и связей между ними.

Наиболее близким к предлагаемому является комбинацйонный суыкатор, содержащий в каждом разряде элементы

И и ИЛИ, причем первые Входы первоГО, второго и третьего элементов И соединены с шиной ввода первого слагаемого, а вторые входы первого и треть его элементов И:и первый вход четвертого элементы И соединены с ащной. переноса из соседнего младшего раз- . ряда, выходы первого, второго и чет-! вертого элементов И соединены со входами первого элемента ИЛИ, выход которого соединен с шиной переноса из

5 данного. РазРяда, а выход третьего элемента И соединен с первым входом второго элемента ИЛИ. Данный сумматор осуществляет операцию суммирования с обеспечением контроля по четност{) ти (2).

Недостаток устройства состоит в его функциональной ограниченности, заключающейся в невозможности выпол нения операции вычитания с обеспече15 .нием контроля по четности.

Яель изобретения - расширение функциональных возможностей сумматора за.счет выполнения операции вычитания с обеспечением контроля по четности, Поставленная цель достигается тем, что комбинационный сумматор, содержащий в каждом разряде четыре элемента И, два элемента ИЛИ, элемент ИЛИНЕ и первый элемент "Равнозначность", причем первые входы первого, второго и четвертого элементов И соединены .с .первым входом сумматора, второй вход первого, первый вход третьего . и второй вход четвертого элементов

И соединены с вторым входом суммато; Научно-исследовательский н проетстйо-конструкторский институт автоматизированных систем управлениятранспортом газа

993253 ра,: первый и второй входы элемента

ИЛИ-НЕ подключечы- к первому и второму входам сумматора, выходы первого, второго и третьего элементов И подключены к соответствующим входам пер вого элемента ИЛИ, выход которого подключен к выходу переноса сумматора и к первому входу первого элемента "Равнозначкость", выход которого соединен с выходом суьэж сумматора, выходы элемента ИЛИ-НЕ и четвертого элемента И подключены к соответствуKNQHM входам второго элемента ИЛИ, содержит в каждом разряде второй и третий элементы "Равнозначность", гпэичем первый вход второго элемента

"Равнозначность" соединен с третьим входом сумматора, а-второй входс шиной управления сумматора и с первым входом третьего элемента "Равнозначность", выход второго элемента

"Равнозначность" соединен с.вторыми входами второго и третьего. элементов,И, с третьими входами элемента

ИЛИ-НЕ и четвертого элемента И,. выход второго элемента ИЛИ соедийен с вторым входом третьего элемента

"Равнозначность", выход которого подключен к второму входу первого элемента "Равнозначность".

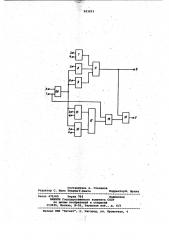

На чертеже представлена структурная схема комбинационного сумматора.Комбинационный сумматор содержит шину 1 управления, первый вход 2 для подачи первого слагаемого (умень шаемого) второй вход 3 для подачи второго слагаемого (аычитавмого), вход 4 для подачи переноса (заема) из предыдущего разряда, выход 5 суммы (разности), выход 6 переноса (заема) в следующий разряд, элементы .

И 7-10, HJIH 11 и 12, ИЛЙ-НЕ 13 и элементы "Равнозначность" 14-16.

Элементы И 7-9 н элемент ИЛИ 11 образуют узел формирования сигнала перейоса (заема). Элементы И 10, ИЛИ 12, KlIH-HE 13 и элементы "Равнозначность" 15-16 образуют узел формирования суммы (разности), а элемент "Равнозначность" 14 является. элементом ввода в зависимостй от операций первого слагаемого или уменьшаемого, на вход которого по шине 1 управления при операции сложения по дается потенциал соответствующий логической единице, а при операции вычитания — логическому нулю.

Комбинационный сумматор работает следующим образом.

Сигнал сумчы (или разности) вырабатывается на выходе 5. При возникновении сбоя в результате формиро- вания переноса (заема) сигнал переноса или заема передается через эле мент "Равнозначность" 16 на выход

5 суммы (разности), таким образом формируя ошибку и в разряде суммы, которая затем может быть обнаружвS

I0 на при контроле многоразрядного сумматора. по четности.

Таким образом, предлагаемый комбинационный сумматор отличается от известных более широкими функциональными возможностями, заключающимися в выполнении операции вычитания двой- ных чисел, представленных в прямых кодах, с обеспечением контроля операции вычитания по четности. Структура сумматора- при этом не усложняе. тся.

Формула изобретения

Комбинационный- сумматор, содвржащий в каждом разряде четыре элемвнта И, два элемента ИЛИ, элемент ИЛИНЕ и первый элемент "Равнозначность", причем первые входы первого, .второго

20 и четвертого элементов H соединены с первые входом сумматора, второй вход первого, первый вход третьего и второй вход четвертого элементов

И соединены с вторым входом суммато25 ра, первый и второй входы элемента

ИЛЙ«НЕ подключены к первому и второму входам сумматора, выходы первого,. второго и третьего элементов И подключены к соответствующим входам

30 первого элемента ИЛИ, выход которого подключен к выходу переноса cymea opa и к первому входу первого элемента "Равнозначность", выход которого соединен с выходом cymes сумматора, 35 выходы элемента ИЛИ«HE и четвертого элемента И подключены к соответствующим входам второго элемента.ИЛИ, о т л и ч а ю щ и и с .я тем, что, с целью. расширения функциональных

40 возможностей за счет выполнения операции вычитания с обеспечениеМ контроля по четности, сумматор содержит в каждом разряде второй и третий элементы "Равнозначность", причем первый вход второго элемента "Раанознач4 ность" соединен с третьим входом сумматора, а второй вход - с шикой управления сумматора и с первым входом третьего элемента "Равнозначность", выход второго элемента "Равнознач® HocTs соединен c BTopsMH входами второго к третьего элементов И, с третьими входами элемента ИЗП -ЙЕ и четвертого элемента И, выход второго элемента ИЛИ соединен с вторим входом третьего элемента "Равнозначности " выход которого подключен к второму входу nepsoro элемента "Равнозначность".

Источники информации

g0- принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 474804, кл. С 06 F 7/50, 1972.

2. Авторское свидетельство СССР

В 710042, «л. G 06 F 7/50, 1977 (про65 тОтип) °

993253

Составитель А. Степанов

Редактор С. Юско ТехредТ.фанта ХорректорИ. Шулла

«««« ««««« ««««««

Заказ .479/65 Тираи 704 .Подписное

ВНИИЕИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, й-35, Раушская наб., д. 4/5

Филиал ППП "Патент", a . Уигород, ул. Проектная, 4