Устройство для умножения @ -разрядных чисел

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<1993255 (61) ???????????????????????????? ?? ??????, ????????-????(22) ???????????????? 28. 07. 81 (21) 3343801>

G 06 F 7/52

Государственный комитет

СССР но. делам изобретений н открытий (23) Приоритет;

Опубликовано 30.0133. Бюллетень М 4 (Щ УДК 681.325 (088. 8) Дата опубликования описания 30.01.83

"(72) Авторы изобретения

Л. Г. Лопато и A. A. Шостак

\ In

1

1 (У1) Заявитель

Минский радиотехнический институт. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ и-РАЗРЯДНЫХ

ЧИСЕЛ

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродейству- ющих устройств умножения асинхронного типа.

Известно устройство для умножения и-разрядных чисел, содержащее и-разрядные Регистры множимого, множителя и результата, сумматор и блок управления 1 1).

Недостатком известного устройства является его низкое быстродействие, вызванное тем, что время, затрачиваемое на сдвиги информации в регистрах, не зависит от числа единиц в разрядах множителя и всегда равно

n tcg.

Известно также устройство ддя умножения h-разрядных чисел, содержа» щее и-разрядные регистры множимого и множителя, 2п-разрядный сумматор, матрицу из и ээллееммееннттоов в ИИ, блок из (2n-3) элементов ИЛИ н два блока из и элементов И каждый (2.).

Недостаток известного устройстванизкое быстродействие, поскольку длительность: такта работы устройства зависит от времени переходного процесса во втором блоке элементов И.

Наиболее близким к предлагаемому является устройство для умножения и-разрядных чисел, содержащее п-раз-.

Рядный регистр множимого,, и-Разрядный Регистр ьыожителя, (2n-1)-разрядный накапливающий сумматор, матрицу. из и элементов И, (2n-3)-Разрядный 2. ,блок элементов ИЛИ, п-разрядный бзуок элементов И и и-разрядный комбина,ционный сумматор, причем выходы регистра множимого соответственно соединены с первой группой- входов матрицы элементов И, выходы (2, . ° ., 2) го --РаэрядОВ КОТОРОЙ соединены с соответствующими входами элементов

ИЛИ блока элементов ИЛИ, выходы элементов ИЛИ которого соответственно соединены с (2, ..., 2n-2)-ми вход2О ными разрядами накапливающего сум-. матора, первый и (2n-1)-й разрядные входы накапливающего сумматора соответственно соединены с первым и п --м выходами матрицы элементов И, вторая группа входов которой соответствен2 но соединена с выходами элементов

И блока элементов И, первые входы .которых соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены

993255 с выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения(3).

Недостаток известного устройства— сложность.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что в устройстве для умножения и-разрядных чисел, содержащем и--разрядный регистр множимого, и-разрядный ре-. гистр множителя, (2n-1)-разрядный накапливающий сумматор, матрицу из и элементов И, (2п-3)-разрядный

1 блок элементов ИЛИ, и-разрядный блок элементов И и и-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первой группой входов матрицы элементов И, выходы (2, 2п-2)-го разрядов которой соединены с соответствующими входами элементов

ИЛИ блока элементов ИЛИ, выходы эле-. ментов ИЛИ которого соответственно соединены с (2. .. °, 2п-2)»ми входными разрядами накапливающего сумматора, первый и (2n-1)-й разрядные входы накапливающего сумматора соответственно соединены с первым и п -м выходами матрицы элементов И, вторая группа входов:которой соответственно соединена с выходами элементов И бло ка элементов И, первый входы элементов И блока элементов И соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного сумматора, а третьи входы объединены и соединены с управляющим входом накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации окончания операции умножения, выходы элементов И блока элементов И соответственно соединены с входами установки в нуль и раз» рядов регистра множителя, инверсные выходы, которого соответственно соединены с входами комбинационного сумматора, а вход разрешения записи регистра множителя соединен с шиной синхронизации устройства.

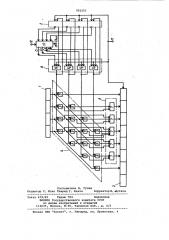

На чертеже изображена структурная схема устройства для умножения и-разрядных чисел (для п-ч).

Устройство для умножения и-разрядных чисел содержит и-разрядный регистр 1 множимого, и-разрядный регистр 2 множителя, (2п-1)-разрядный накапливающий сумматор 3, матрицу 4 иэ и элементов И 5, (2п-3)-разрядный блок 6 элементов ИЛИ 7, и-разрядный блок 8 элементов И 9, и-разрядный комбинационный сумматор 10, ши5 ну 11 синхронизации, управляющий вход 12 и -выход 13 индикации окончания операции умножения, причем выходы регистра 1 множимого соответственно соединены с первой группой входов матрицы 4 .элементов И 5, выходы (2, ..., 2п-1)-го разрядов которой соединены с соответствующими входами элементов ИЛИ 7 блока 6 элементов ИЛИ, выходы элементов ИЛИ 7 которого соответственно соединены с (2, ..., 2п-2)-ми входными разрядами накапливающего сумматора 3, первый и (2п--1)-й разрядные входы накапливающего сумматора 3 соответственно соединены с первым и и -м выходами матрицы 4 элементов И 5, вторая группа входов которой соответственно соединена с выходами элементов И 9 блока 8 элементов И и с входами установки в ноль и разрядов регистра 2 множителя, первые вхоцы элементов И 9 блока 8 элементов И соответственно соединены с прямыми выходами регистра

2 множителя,, инверсные выходы кото- рого соответственно соединены с входами комбинационного сумматора 10, выходы комбинационного сумматора 10 соответственно соединены с вторыми входами элементов И 9 блока 8 элементов И, третьи входы которых объ35 единены и соединены d управляющим входом накапливающего:сумматора 3, входом разрешения записи регистра 2 множителя и шиной 11 синхронизации устройства, управляющий вход 12 уст40 ройства соединен с входом переноса комбинационного сумматора 10, выход переноса которого соединен с выходом

13 индикации окончания операции умножения.

45 Устройство Работает следующим образом.

Пусть требуется перемножить множимое х на множитель у = у .у у у, =

1010. В исходном состоянии в регистре 1 хранится двоичный код множимого х без знака, а в регистре 2 двоичный код множителя у также без знака, сумматор 3 обнулен, а на выходе счетчика сформирован результат с c 4,,c с с 0101 + 0001 = 0110.

Собственйо работа устройства начинается с момента прихода первого синхроимпульса на вход 11 устройства.

По этому синхроимпульсу формируется управляющий сигнал на выходе второго элемента И 9 блока 8 элементов И (так как толька с у 1), который производит передачу соответствующим . образом сдвинутого множимого с выходов элементов И 5 второй строки

65 матрицы 4 через блок 6 элементов

993255

ИЛИ 7 в накапливающий сумматор 3, а также осуществляет установку второго разряда регистра 2 множителя в нуль с разрешения синхроимпульса, поступающего на его вход разрешения записи с.шины 11 синхронизации уст- 5 ройства. После этого одновременно с суммированием частичного произведения в накапливающем сумматоре 3 в комбинационном сумматоре 10 формиру. ется результат с с4,с с с+ 0111 + 10

+ 0001 1000.

Во втором такте работы устройства с приходом второго скнхрокмпульса на шину 11 синхронизации устройства на выходе четвертого элемента И 94 блока 8 элементов И фоРмируется управляющий сигнал (c4 1 и у4 1), который производит передачи соответствующим образом сдвинутого множимого с выходов элементов И 5 четвертой строки матрицы 4 элементов И 5 через блок 6 элементов ИЛИ 7 в накапливакв1ий сумматор 3 и осуществляет уста новку четвертого разряда регистра 2. множителя в ноль. После этого, одно« временно с суммированием в накапливающем. сумматоре 3 очередного частичного произведения, комбинационном сумматоре 10 формируется результат с с4сьс с 1111 + 0001 = 0000 и возникает перенос спы = 1. Поскольку

c+„ - =1, то на выходе 13.индикации устройства присутствует сигнал, что означает окончание операции узыожения чисел.

Отсутствие, по сравнению с прото- 35 типом, и-разрядного буферного регист. ра и второго блока элементов И значительно упрощает устройство, не снижая его быстродействия.

Формула изобретения

Устройство для умножения и-разрядных чисел, содержащее и-Разрядный 45 регистр множимого, и-разрядный регистр множителя, (2n-1)-разрядный накапливающий сумматор, матрицу из п элементов И, (2n-3)-разрядный блок элементов ИЛИ, и-разрядный блок элементов И и и-разрядный комбинационный сумматор, причем выходы регистра множимого соответственно соединены с первой группой входов.матрицы элементов И, выходы (2, 2п -2)-го разрядов которой соединены с соответствующими входами элементов

ИЛИ блока элементов ИЛИ, выходы элементоэ ИЛИ которого соответственно соединены с (2, ..., 2п-2) -ми входными разрядами иакапливакнцего сумматора, первый и (2n-1) -й разрядные входы накапливающего суююатора соот» ветственно соединены с первым и и -м

4 выходамн матрицы элементов И, вторая группа входов которой соответственно соединена с выходами элементов И блока элементов И, первые входы элементов И блока элементов И соответственно соединены с прямыми выходами регистра множителя, вторые входы элементов И блока элементов И соответственно соединены с выходами комбинационного суююатора, а третьи входы объединены и соединены с управляющим входом .накапливающего сумматора и шиной синхронизации устройства, вход и выход переноса комбинационного сумматора являются соответственно управляющим входом устройства и выходом индикации-окончания операции умножения, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, выходы элементов И блока элементов И соответственно соединены с входами установки в нуль и разря дов регистра множителя, инверсные выходы которого соответственно соединены с входами комбинационного сумматора, а вход разрешения записи регистра множителя соединен с шиной синхронкзацик устройства.

Источники информации, принятые во внимание при экспертизе

1. Карцев M. A. Арифметика цифро- . вых машин. И., "Наука", 1969, с. 350, 364.

2. Авторское свидетельство СССР

9 482740, кл. 6 06 F 7/52, 1974.

3. Авторское свидетельство СССР по заявке Ю 3321307/18-24, кл. G 06 F 7/52, 1981 (прототип).

Составитель В. Гусев

Редактор С. Юско Техред Т. Фанта Корректор В. «Бутяга

Заказ 479/65 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауыская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4