Запоминающее устройство

Иллюстрации

Показать всеРеферат

G П И С А Н И Е (и 993268

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6! ) Дополнительное к ввт. свид-ву (22) Заявлено 29.01.81 (21) 3262874/18-24 (53)M. Кл.

QO6 Р 13/02

G 11 С 17/00 с присоедннениеат заявки №

Гесударстеекньй кемнтет

СССР (23)Приоритет (5Ç) УДК 681.327. .6 (088.8) ао делан кзебретевкй и втарнтий

Опубликовано 30.91.83. Бюллетень № 4

Дата опубликования описания 01.02.83 I!

1 .,.

Ю.A. Айзман, А. В. Лайшевский, B. Н. Бодрин, А . С. Йевяйсив .. .", -„;: ., и В. П.Марухнеико т: т ... pi .

L

Геофизическая экспедиция №2 Цещрального произвбдственнщго " геологического объединения по геофизическим работам (72) Авторы изобретения (7I) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО.1

Изобретение относится к вычислитель ной технике, к устройствам, где необходимо накапливание. некоторого массива двоичной информации с последующим непрерывным считыванием в последователььом коде, например в растровых графичес5 ких индикаторах с дискретным методом формирования изображения. При опросе

ЗУ синхронно с движением луча ЭЛТ на выходе ЗУ формируется последовательный код, соответствующий видеосигналу графического изображения.

Известны ЗУ, позволяющие осуществлять непрерывное считывание накопленного массива двоичной информации в после- > довательном коде и состоящие из матрицы памяти и двух сдвиговых регистров. Каждая ячейка матрицы памяти имеет информационный выход, адресный и считываю ший входы, причем информационные выхо- 2о ды каждого столбца матрицы объединены и через селектор соединены с соответствующими входами сдвиговых регистров.

Выходы регистров объединены по ИЛИ и

2 образуют выход ЗУ. Адресные входы так же объединены в группы и образуют адресные шины, а считывающие входы объединены и образуют шину считывания Maw рикы.

Работают сдвиговые регистры в противофазе, т.е. пока с одного информация считывается в последовательном коде, во второй через селектор в параллельном коде перезаписывается информация одной строки матрицы, и наоборот, чем и до стигается непрерывное считывание инфор. мации. Частота сдвига информации в регистрах определяется частотой формирования последовательного кода, тогда как частота обращения к матрице ниже чаототы формирования последнего в и раз, где n — разрядность регистра f1).

Недостаток данного ЗУ наличие сдвиговых регистров.

Наиболее близким к предлагаемому по технической сущности является ЗУ, содержащее матрицу памяти, элементы И и элемент ИЛИ, причем первые адресные

68 4 формируется последовательный двоичный код. Частота формирования последоватеш ного кода равна 1/ сакэ, rEte >3 - время прохождения импульса между соседними выходами ЭЗ 5. Когда импульс считывания поступит на вторую часть матрицы 2, информация первой полустроки первой части матрипы 2 будет считана, и код на адресных шинах 3 сменяется другим, соответствующим выборке второй полустроки. По окончании считывания первой строки матрицы 2 на шину считывания подается следующий импульс, период следования которых равен 2К ээ, где Кчисло столбцов в одной части матрицы 2.

После смены кода в первой части.матрицы 2 начинает считываться информация второй полустроки первой части матрицы

2, за время считывания которой во второй части матрицы 2 на принадлежащих ей адресных шинах 4,осуществляется смена кода, соответствующего выборке второй полустроки. Аналогично производится считывание информапии с остальных. строк матрицы 2.

Предложенное ЗУ позволяет производить считывание информации с частотой, превышающей предельно допустимую часто ту обращения к ячейкам памяти матрицы

ЗУ.. 3 ММ входы каждой ячейки матрицы памяти объединены в группы и образуют адресные шины строк; вторые адресные входы каждой ячейки памяти объединены вдоль и образуют адресные шины столбцов; информационные выходы объединены монтажным или схемным ИЛИ и образуют выход

ЗУ.

Частота обращения к матрипе равна частоте формирования последовательного >О кода, которая ограничена быстродействием ячеек матрицы памяти (2 3

Низкое быстродействие является не достатком известного ЗУ.

Цель изобретения — повышение быстрр- 1 действия считывания информации ЗУ независимо от быстродействия элементов матрицы.

Поставленная цель достигается тем, что запоминающее устройство, содержащее запоминающую матрицу и элемент

ИЛИ, входы которого соединены с соответствующими информационными шинами, запомннающей матрицы, а выход элемента ИЛИ является выходом устройства, д дополнительно содержит элемент задержки, вход и выход которого соединены с соответствующими шинами запоминающей матрицы.

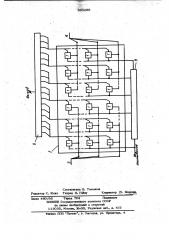

На чертеже приведена схема заломив нающего устройства.

Запоминающее устройство включает ячейки 1 памяти, образующие матрицу памяти 2 с двумя группами адресных шин 3 и 4, элемент 5 задержки и элемент

ИЛИ 6.

Адресные. входы ячеек 1 памяти объединены вдоль полустрок матрицы 2 и образуют две группы адресных шин 3 и . 4. Все информационные выходы чее 1 40 памяти подключены к элементу ИЛИ 6.

Считывающие входы ячеек 1 памяти объединены вдоль столбцов матрицы 2 и соединены с выходами ЭЗ 5, вход которого образует шину считывания ЗУ.

Перед считыванием информации на нд« ресные шины подан код, соответствующий, выборке первых полустрок матрицы 2. считывание начинается с момента поступления на одноименную шину импульса, 50 . который последовательно формируется на выходах ЭЗ 5, цри этом на выходе ЗУ

Форм ула иэ обретения

Запоминающее устройство, содержащее запоминающую матрицу и элемент ИЛИ, входы которого соединены с соответствующими .информационными шинами запоминающей матрицы, а выход элемента ИЛИ является выходом устройства, о т л и ч аю щ е е с я тем, что, с целью повыше>-. ния быстродействия устройства, оно содержит элемент задержки, вход и выход которого соединены с соответствующими шинами запоминающей матриц.

Источники информации, принятые во внимание при экспертизе

1. Соловейчик И. Е. Дисплэй в системах с ЭВМ. Советское Радио, 1979.

2. Гуглин И.E. Электрониый синтез телевизионных иэображений. Советское

Радио, 1979, с. 114, 115 (прототип).

Составитель .В. Теленков

Редактор С. Юско Текред И. Гайду Корректор М. Шарош

Заказ 480/66 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по. делам изобретений и mmðûòêé

113035, Москва, Ж- 35, Раушская иаб., д. 4/5

Филиал ППП «Патент;- r. Ужгород, ул. Проектная, 4