Генератор псевдослучайных последовательностей

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Саеетских

Сециалистикескик республик

{61)дополнительное к авт. свид-ву (22) Заявлено 01.06В1" {2i)3293893/18-21

fgg)+ Кд э

Н 03 К 8/84 с присоединением заявки ИоГосударственный комитет

СССР по делам изобретений и открытий (23) Приоритет (33) УДК 621. 37З.

4 (088. 8) Опубликовано 3001ВЗ. Бюллетень N94

Дата опубликования описания 309133 (72) Авторы изобретения

В.В. Богданов и В.С. Лупиков (73) Заявитель (54) ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ

ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Изобретейие относится к импульс ной технике и может быть использо- вано для формирования тестовых последовательностей.при контроле и диагностике неисправностей цифровых устройств автоматики, телемеханики и вычислительной техники

Известна устройство для формирования псевдослучайных сигналов сломной структуры, содержащее генератор тактовых импульсов, генератор псевдослучайной последовательности, эле- : мент И, электронный ключ, счетчик тактов, элемент НЕ, дешифратор, счетчик циклов и триггер, позволяющее формировать многократно повторяемые периоды псевдослучайной последова».. тельности, сдвинутые один относитель но другого на заданный интервал времени 1).

Недостатком этого устройства является невозможность формирования псевдослучайной последовательностив обратном направлении и блокирования выходных сигналов устройства на отдельнйх отрезках последовательности.

Наиболее близким по технической сущности к предлагаемому является генератор псевдослучайных последовательностей, содержащий генератор так-, З0 тоже импульсов элемент Й первыя вход которого соединен с выходом генератора тактовых импульсов, вычи таищий счетчик, счетный вход которого соединен с выходом элемента И, группу элементов И, выходы которых являются выходами генератора, 6 -разрядный реверсивный сдвигающий регистр, установочный вход кото(эого соединен с шиной "Установка", вход синхрони-зации соединен с выходом элемента

И, а.выходы соединены с первыми входами группы элементов И, первый и второй сумматоры по модулю два, .входы которых соединены с выходами реверсивного сдвигающего регистра, а выходы соединены соответственно

c,ïåðâûì и вторым информационными входами реверсивного сдвигающего регистра (2 1..

Недостатком этого устройства являются его ограниченные функциональные возможности, ° так как при использовании генератора псевдослучайных после- довательностей в качестве источника входных тестовых воздействий контролируемых устройств в ряде случаев непосредственно воспользоваться последовательностью кодов генератора не упается, поскольку в.этих устройст993444

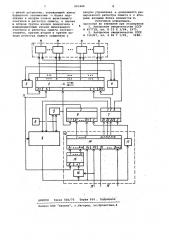

На чертеже также показан пример

25,выполнения буферного запоминающего блока 10, который содержит запоминающий блок 14 с произвольной выборкой, счетчик 15 адреса, элемент

ИЛИ 16 и формирователь 17 импульсов.

ЗО Блок 9 управления выполнен на

D-триггерах.

Генератор работает следующим образом.

Перед началом работы составляется

35 программа формирования выходной псевдослучайной последовательности кодов в ниде последовательности управляющих слов.. Каждое управляющее слово имеет (и + 3) разряда,где n - разрядность

4ц регистра 2. Первые и разрядов управляющего слова A1...An содержат двоичный код длины а отрезка псевдослу-. чайной последовательности, на которой генератор выполняет одну иэ воз45 можных операций, предусмотренных в коде операции. Код операции содержится в (n + 1), (n + 2), (n + 3)-ем разрядах управляющего слова (Ад+л, А„, A„ ).. Разряд A„+„ содержит прйзнак конца программы. A »„ О в последнем управляющем слоне программы, а в остальных словах A + = 1.

Разряд An+ определяет направление формирования отрезка псевдослучайной последовательности: в прямом направлении при An+g = 1 и в обратном направлении при A n+< = О. Разряд

А„+ определяет состояние выхода генератора. Если А +э = 1, то на выход поступает формируемая генера6О. тором последовательность кодов. Если Ад+ = О, то на выходе поддержива ется уровень логического "0", а фор« мируемая генератором последовательность кодов не поступает потребите 5.лю (маскируется). вие большой скорости изменения тестовах нозникают состояния неопределенности вследствие одг временного изменения нескольких входных воздействий, появления на входах контролируемых устройств запрещенных комбинаций и других причин. Иногда для проверки правильности функционирования устройств требуется повторение определенных участков последовательности кодов генератора (пересчетные схемы ), поэтому при контроле целесообразно использонать не всю псевдослучайную последовательность кодов, а отдельные ее участки, формируемые н прямом или обратном направлении, с блокировкой или без блокировки выходных сигналов. генератора, для этого предварительно необходимо составлять программу проверки контролируемых устройств, определяющую порядок и характер формирования отдельных участков псевдослучайной последовательности. Выполнять эту программу путем изменения вручную выполняемых генератором функций, как в известных устройствах., тр,.доемко и практически невозможно, вследствых воздействий контролируемых устройств.

Цель изобретения — автоматизация процесса формирования запрограммированных участкон генерируемой последовательности.

Поставленная цель достигается тем, что в генератор псевдослучайных последовательностей,, содержащий генератор тактовых импульсов, выход которого соединен -. первым нходой элемента И, выход которого подключен ,к счетному входу вычитающего счетчика, и к синхронизирующему входу и эазрядного реверсивного регистра сдвига, установочный вход которого соединен с шиной установки, первый и второй информационные входы соединены соответственно через первый и второй сумматоры по модулю два с соответствующими выходами п -разрядного реверсивного регистра сднига, выходы которого также соединены с первыми входами блока элементов И, дополнительно введены буферный запоминающий блок, регистр, сдвига и блок управления, первый вход которого соединен с шиной установки, второй вход соединен с выходом генератора тактовых импульсов„ третий вход соединен с выходом вычитающего счетчика, а четвертый вход подключен к первому выходу регистра сдвиГа, первый выход блокЬ управления соединен с вторым входом элемента И, второй выход подключен к входу считывания буферного запоминающего блока, уста- новочный вход которого соединен с шиной установки, управляющий выход буферного запоминающего блока подключен к входам записи вычитающего, счетчика и регистра сднига, а первая и вторая группа выходов подключена к информационным входам вычитающего счетчика и регистра сдвига соотнетственно, причем второй и третий выходы регистра сдвига соединены с входом управления и -разрядного реверсивного регистра сдвига и с вторыми входами блока элементов И.

На чертеже приведена функциональная схема генератора псевдослучайных последовательностей.

Генератор псевдослучайных последовательностей содержит блок 1 элементов И, п -разрядный реверсинный регистр 2 сдвига, сумматоры 3 и 4 по модулю 2, элемент И 5, вычитающий счетчик б, регистр 7 сдвига, генератор 8 тактовых импульсов, блок 9 управления, буферный запоминающий блок 10, шину 11 установки, шины 12 информационных входов, шину

13 записи.

993444

Составленная программа загружа». ется в блок 10, где она хранится и может быть многократно использована. Перед загрузкой программы сигналом по шине 11 обнуляется счетчик

15 адреса блока 10 ° На шины 12 подается первое управляющее слово программы и сигналом по шине 13 оно записывается в нулевую ячейку памяти..

Сигнал с шины 13 через элемент ИЛИ

16 поступает на счетный вход счетчика 15 и своим задним фронтом переводит его в следующее .состояние. Аналогично в блок 14 записываются остальные управляющие слова программы.

После загрузки программы сигналом по шине 11 снова обнуляется счетчик

15 и устанавливаются в исходные состояния регистр 2 и блок 9 управления. На выходе блока 9 управления формируется сигнал, выдаваемый на вход разрешения считывания блока 10.

На информационные входы блока 10 поступает первое управляющее слово из нулевой ячейки памяти. Сигнал с выхода формирователя 17. задержанный относительно сигнала на входе разрешения считывания блока 14, переписывает первые и разрядов управляющего слова (а) в вычитающий счетчик

6, а (и + 1), (n + 2), (n + 3)-ий разряды (код операции) - в регистр 7.

После окончания считывания управляющего слова из блока 10 на первом выходе блока 9 управления проявляется сигнал, разрешающий прохождение импульсов с генератора 8 тактовых импульсов через элемент И 5 на вход синхронизации регистра 2 и на счетный вход вычитающего счетчика б. При этом в зависимости от сигнала на входе управления направлением сдвига регистра 2 происходит сдвиг информации в регистре 2 в прямом или обратном направлении, и формируется псевдослучайная последовательность кодов в прямом или обратном направлении. Б зависимости от состояния третьего ре« гистра 7 генерируемая последовательность кодов поступает на выход устройства или блокируется с помощью блока элементов И 1. Каждый импульс на выходе элемента И 5 уменьшает со-, держимое вычитающего счетчика 6 на единицу. После Ь сдвигов регистра 2 счетчик 6 обнуляется, на его выходе

2 формируется сигнал, поступающий в блок 9 управления. В результате на выходе блока 9 управления появляется сигнал,.запрещающий прохождение импульсов через элемент И 5. Так кон- чается формирование первого отрезка псевдослучайной последовательности кодов, соответствукицего первому уп.равляющему слову програмьы. Послеэтого блок 9 управления формирует сигнал на вход разрешения считывания блока 10, и второе управляющее слово програмьы переписывается в счетчик 6 и регистр 7. Формируется

;новый отрезок псевдослучайной посде,довательности кодов в соответствии с кодом операции, записанном в реги5 стре 7, длиной в Д кодов, занесенной

,в счетчик 6, и т.д. Управляющие слова програмьит по порядку считываются иэ блока 10 до тех пор, пока в последнем управлякицем слове проходит приз+

10 нак конца программы, который блокирует в блоке 9 управления выдачу сигналов разрешения считывания в блок 10 °

Таким образом, введение в генерат5 тор псевдослучайных последовательностей блока 9 управления, регистра

7 и блока 10 позволяет организовать автоматическую работу генератора по заранее разработанной программе, aosможности составления выходной последовательности кодов из отдельных отрезков псевдослучайной последовательности, формируемых s прямом или обратном направлении, с блокировкой или без блокиРовки выхода УстРойства, что позволяет, более эффективно использовать генератор для контроля и диагностики цифровых устройств.

Формула изобретения

Генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, выход котоЗ5 рого соединен с первым входом эле-,, мента И, выход которого подключен к счетному входу вычитающего счетчика, и к синхронизирукицему входун-разрядного реверсивного регистра

g0 сдвига, установочный вход которого соединен с шиной установки, первый и второй информационные входы соединены соответственно через пврвый и второй сумматоры тто модулю два с45 соответствующими. выходами тт -разрядного реверсивного регистра сдвига, выходы которого также соединены с . первыми входами блока элементов И, отличающийся тем, что, 50 с целью автоматизации процесса формирования запрограммированных участков генерируемой последовательности, в него дополнительно введены буферный запоминающий блок, ретистр сдвига и блок управления, первый вход которого соединен с шиной установки, второй вход соединен с выходом генератора тактовых импульсов, третий вход соединен с выходом вычитакицего счет-. чика, а четвертый вход подключен к

60 первому выходу регистра сдвига, первый выход блока управления соединен с вторым вХодом элемента И, второй выход подключен к входу считывания буферного запоминающего блока, ус65 тановочный вход которого соединен

99 34 44 входом управления и -разрядного реверсивного регистра сдвига и с вторыми входами блока элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 497718, кл. Н 03 К 3/84, 1975.

2. Авторское свидетельство СССР . в 756397, кл. G 06 F 1/02) . 1980 ° вНИИПИ Заказ 506/75 Тираж 934 . Подписное

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4 с шиной установки, управляющий выход буферного запоминающ:- о блока подключен к входам записи вычитающего . счетчика и регистра сдвига, а первая и вторая группа входов подключена к информационным входам вычитающего счетчика и регистра сдвига соответственно, причем второй и третий выходы регистра сдвига соединены с