Генератор функций

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистическик

Республик

<п>993446 (63) Дополнительное к авт. свид-ву (22) Заявлено 140431 (21) 3273445/18-21 с присоединением заявки ¹â€” (23) Приоритет (:)публиковано 30.0 1.83. Б оллетень ¹ 4 (51) М. Кй.з

Н 03 К 4/02

Государственный комитет

СССР но делам изобретений и открытий.

t$3) УДКб81..142 (088.8) Дата опубликования описания 3001.83

{72) Автор изобретения

С.В. Стрижак

{71) Заявитель

{.54) ГЕНЕРАТОР ФУНКЦИЙ

Изобретение относится к импульсной технике и может найти применение в устройствах автоматики.

Известен генератор функций, содержащий генератор импульсов, распределитель импульсов, группу аналоговых .ключей, группу потенциометров, источник опорного напряжения и сумматор(13, Недостатки известного устройства— низкая надежность и большие габариты.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее генератор тактовых импульсов, первый и второй элемен- 5 ты И, управляемый делитель частоты, блок программируемой памяти, дешифратор и счетчик, группа выходов которого соединена с входами дешифратора, группа выходов которого соединена с входами блока программируемой памяти, группа выходов которого соединена с входами управляемого делителя частоты, а дополнительный выход соединен с первым входом второго элемента И 2). 25

Недостатком известного устройства являются недостаточные функциональные возможности, так как оно не позволяет работать в режиме частотно-импульсной модуляции. 30

Цель изобретения — расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в генератор функций, содержащий генератор тактовых импульсов, первый и второй элементы И, управляемый делитель частоты, блок программируемой памяти, дешифратор и счетчик импульсов, группа выходов которого соединена с входами дешифратора, группа выходов которого соединена с входами блока программируемой памяти, группа выходов которого соединена с входами управляемого делителя частоты, стробирующий вход которого соединен с выходом генератора тактовых импульсов, а прямой выход — с первым входом первого элемента И, а первый вход второго элемента И соединен с дополнительным выхбдом блока программи-руемой памяти, введены инвертор, триггер, дискриминатор уровня, формирователь ступенчатого напряжения и, делитель. частоты, вход которого соединен с выходом генератора тактовых импульсов, а выход — с входом счетчика импульсов, установочным входом управляемого делителя частоты и первым входом триггера, выход которого соединен с вторыми входами первого

993446

Формула изобретения

Генератор функций содержаций щ генератор тактовых импульсов, первый и второй элементы И, управляемый делитель частоты, блок программируемой памяти, дешифратор и счетчик импульсов, группа выходов которого соединена с входами дешиф-. ратора, группа выходов которого соединена с входами блока программируемой памяти, группа выходов которого соединена с входами управляемого делителя частоты, стробирующий вход которого соединен с выходом генератора тактовых импульсов, а прямой .выход — с первым входом первого элемента И, а первый вход второго элемента И соединен с дополнительным выходом блока программируемой памяти, отличающийся тем,что, с целью расширения функциональных возможностей, в него введены инвертор, триггер, дискриминатор уровня, 40 формирователь ступенчатого напряжения и делитель частоты, вход которого соединен с выходом генератора тактовых импульсов, а выход — с входом счетчика импульсов, установочным . 45 входом управляемого делителя частоты и первым входом триггера, выход которого соединен с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами формирователя ступенчатого напряжения, первый вход второго элемента И соединен через инвертор с третьим входом первого элемента И, третий вход второго элемента И соединен с инверсным выходом управляемого делителя частоты, при этом выход формирователя ступенчатого напряжения соединен с входом дискриминатора уровня, выход которого соединен с вторым входом триггера.

Источники информации, принятые во внимание при экспертизе

1. Опубликованная заявка ФРГ

9 2544896, кл. Н 03 К 4 -02, 1975.

2. Авторское свидетельство СССР и второго элементов И, выходы которых соединены с первым и вторым входами формирователя ступенчатого напряжения, первый вход второго элемента И соединен через инвертор с третьим входом первого элемента И, третий вход второго элемента И соединен с инверсным выходом управляемого делителя частоты, при этом выход формирователя ступенчатого напряжения соединен с входом дискриминатора уровня, выход которого соединен с вторым входом триггера.

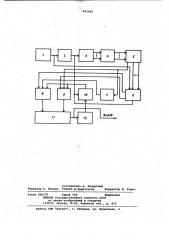

На чертеже показана структурная схема устройства.

Генератор функций содержит генератор 1 тактовых импульсов, делитель

2 частоты, счетчик 3 импульсов, деши-. фратор 4, блок 5 программируемой

;памяти, управляемый делитель 6 частоты, инвертор 7, первый и второй элементы И 8 и 9, триггер 10, формирователь 11 ступенчатого напряжения, дискриминатор 12 уровня.

Устройство работает следующим образом.

На выходе формирователя 11 формируется сигнал, который представляет собой ступенчатую аппроксимацию заданной функции. Величина ступени определяется длительностью управляющего импульса на выходе элементов

И 8 и 9 . Если же на выходе элементов 8 и 9 присутствует логический

"0", то напряжение на выходе формирователя 11 остается неизменным.

Управляющий импульс на выходе элемента 9 приводит к увеличению напряжения на выходе устройства, а управляющий импульс на выходе элемента 8 — к уменьшению. Информацию о монотонном изменении выходного сигнала устройства несет логический сигнал на дополнительном выходе блока 5. Другие выходы блока 5 несут информацию о количестве и величине ступеней аппроксимированного сигнала

При генерации функции импульсами с генератора 1 через делитель 2, счетчик 3, дешифратор 4 последовательно опрашиваются входы блока 5 и, таким образом, на управляющие входы управляемого делителя б последовательно подаются кодовые пакеты.

Цепь-дискриминатор 12, триггер 10 обеспечивают строгое задание максимального напряжения выходного сигнала. При достижении выходным сигналом максимального значения на выходе дискриминатора 12 появляется импульс, который переводит триггер 10 в состояние логического "0". Логический "0" на выходе триггера 10 блокирует прохождение сигналов через элементы И 8 и 9, напряжение на выходе устройства прекращает изменяться. Передним фронтом импульса с выхода делителя 2 триггер 10 устанавливается в исходном состоянии и напряжение на выходе устройства начинает уменьшаться, или остается постоянным в зависимости от логического сигнала на дополнительном выходе блока 5.

Возможностью менять частоты и скважность сигналов управления формирователя 11, изменяя коэффициент деления, делитель б позволяет в предлагаемом устройстве менять количество и величину ступеней выходного сигнала, что дает возможнОсть аппроксимировать сигналы сложной конфигурации при минимальном объеме.

Р 609496, кл. Н 03 К 4/02, 1974.

993446

Составитель A. Поддубный

Редактор A. Мотыль Техред..Е.Харитончик Корректор Е. Рошко

Заказ 506/75 Тираж 934 Подписное

ВНИИПИ Государственного коьятета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.. ужгород, ул. Проектная, 4