Буферное логическое ттл устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (n>993477 фь (61) Дополнительное к авт. свид-ву(22) Заявлено 0607.81 (21) 3312331/18-21 с присоединением заявки М— (51) М. Кп. з

Н 03 К 19/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

Опубликовано 30.01,83. Бюллетень Йо 4

Дата опубликования описания 3001.83 (33) УДК 621. 374 (088, 8) (72) Авторы изобретения

В.И. Эннс, A.È. Авдеев и tO.В. Кружано (71) Заявитель (54) БУФЕРНОЕ ЛОГИЧЕСКОЕ ТТЛ-УСТРОИСТВО

Изобретение относится к импульс= .ной н вычислительной технике и авто.матике, а именно к буферным ТТЛ-устройствам, реализующим функцию инверсий и тавтологии и предназначенным для использования в счетных и управФ ляющих ЭВМ, в системах сбора и обработки информации, в различных систе-.. мах контроля и управления, в схемах памяти и т.д, Известны логические буферные

ТТЛ-устройства, осуществляющие функ- . ции инверсии и тавтологии (1 ).

Такие устройства обычно выполняют в виде двух последовательно включенных ТТЛ-инверторов, обладают небольшим быстродействием и постоянно потребляют мощность.

Наиболее близким к предлагаемому по технической сущности является буферное устройство, отключающееся в пассивном режиме при помощи ключа от шины Земля, содержащее ключ отключающий устройство от шины Земля, входного и выходного каскадов; последний содержит блок инверсии и блок тавтологии,.причем блок тавтологии содержит первый транзистор, 5аэа которого подключена к выходу входного каскада, коллектор подключен к базе второго транэиСтора и через резистор к источнику напряжения (2 J.

Однако устройство обладает низким быстродействием и помехоустойчивостью.

Цель изобретения — повышение помехоустойчивости буферного логического ТТЛ-устройства, Поставленная цель достигается тем, что буферное логическое ТТЛустройство, содержащее ключ, входной транзистор, эмиттер которого соединен с входной шиной, база через резистор — с шиной питания, коллектор с базой промежуточного транзистора, коллектор которого соединен с базамн первого и второго транзисторов и через резистор с шиной питания, коллектор первого транзистора соединен с первой выходной шиной, коллектор второго транзистора соединен с базой третьего транзистора и через резистор — с шиной питания, коллектор третьего транзистора соединен с второй выходной шиной, эмиттеры первого, второго и третьего транзисторов подключены к аноду диода, катод которого соединен через ключ с общей шиной и.через ре993477

15

25

35

60

65 эистор - с шиной питания, дополнительно содержит диод и ключ, причем эмиттер промежуточного транзистора соединен с анодом дополнительного диода, катод которого соединен через параллельно подключенные резистор и дополнительный ключ с обцей шиной.

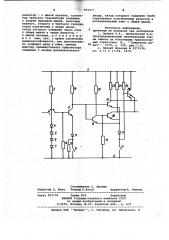

На чертеже изображена электрическая схема предлагаемого логического устройства.

Эмиттер транзистора 1 является входом логического устройства. База транзистора 1 через резистор 2 соединена с шиной 3 питания, База транэистора 1 соединена также с анодом диода 4, катод которого соединен с анодом диода 5. Катод диода 5 сое.динен с анодом диода б, катод которого соединен с анодом диода 7, катод которого соединен с общей шиной. Коллектор транзистора 1 соединен с базой транзистора 9, а также через резистор 10 соединен с общей шиной. Эмиттер транзистора 9 соединен с анодом. диода 11, катод которого соединен с ключом 12, а также через резистор 13 — c общей шиной 8.

Второй конец ключа 12 соединен с обцей шиной.8, Коллектор транзистора 9 соединен через резистор 14 с шиной 3 питания, а также соединен с базами транзисторов 15 и 16, Коллектор транзистора 16 является выходом устройства, реализующим функцию тавтологии, Эмиттер транзистора 16 соединен с анодом диода 17, Коллектор транзистора 15 соединен через резистор 18 с шиной 3 питания и через резистор 19 - с обцей шиной 8, а также с базой транзистора 20 ° Эмиттер транзистора 15 и эмиттер транзистора 20 соединены с эмиттером транзистора 16, Коллектор транэистора 20 является выходом устройства, реализующим функцию инверсии. Катод диода 17 соединен с ключом 21 также соединен С базой двухэмиттерного транзистора 22 и через резистор

23 - с шиной 3 питания. Второй конец ключа 21 соединен с общей ши- . ной 8. Первый эмиттер транзистора 22 соединен с коллектором транзистора

16, второй — с коллектором транзистора 20, коллектор транзистора 22 соединен с шиной 3 питания. Коллектор транзистора 20 соединен через резистор 24 с шиной 3 питания, Коллектор транзистора 16 соединен через резистор 25 с шиной 3 питания.

Устройство работает следующим образом.

Потенциал катода диода 11 близок к потенциалу обцей шины S при разомкнутых ключах 12 и 21 и при единичном сигнале на входе устройства определяется потенциалом на базе транзистора 1, который ограничен диодной цепью (диоды 4 — 7) . Транзистор 9 при разомкнутых ключах 12 и 21 и единичном сигнале на входе устройства находится на границе проводящего состояния и состояния отсечки и пропускает незначительный ток, ограниченный резистором 1"- большой величины поэтому после включения ключей 12 и 21 транзистор 9 сразу переходит в проводящее состояние, в отличие от транзисторов 15 и 16, которые при разомкнутых ключах 12 и 21 находятся в состоянии отсечки, так как потенциал на.катоде диода

17 равен потенциалу шины 3 питания, Потенциал на коллекторе транзистора

9 и -соответственно потенциалы на базах транзисторов .15 и 16 начинают уменьшаться. Вследствие этого транзисторы 15 и 16 остаются в состоянии отсечки, несмотря на уменьшение потенциала на их эмиттерах, а. транзистор 20 переходит в проводящее состояние. Резисторы 18 и 19.представляют из себя делитель напряжения и при разомкнутых ключах 12 и 21 обеспечивают потенциал на базе транзистора 20 меньший, чем потенциал йа базе транзистора 15. Поэтому при нулевом сигнале на входе устройства после замыкания ключей 12 и 21 тран- зистор 9 остается в состоянии отсечки, а в первую очередь в проводящее состояние переходят транзисторы .15 и 16, Вследствие этого потенциал на коллекторе транзистора 15 и соответственно на базе транзистора 20 уменьшается-и транзистор 20 остается в состоянии отсечки, несмотря на уменьшение потенциала .на его эмиттере. Резисторы 24 и 25 обеспечивают выходной ток единичного выходного сигнала. Транзистор 22 обеспечивает большо выходной ток после выключе.ния ключей 12 и 21, необходимый для зарядки большой емкости нагрузки.

Резистор 10 уменьшает потенциал базы транзистора 9 при единичном входном сигнале, повышение которого обусловлено емкостными токами после выключения ключей 12 и 21.

Формула изобретейия

Буферное логическое ТТЛ-устройство, содержащее ключ, входной транзистор, эмиттер которого соединен с входной шиной, база через резистор — с шиной питания, коллектор— с базой промежуточного транзистора, коллектор которого соединен с базами первого и второго транзисторов и через резистор с шиной питания, коллектор первого транзистора соединен с первой вйходной шиной, коллектор второго транзистора соединен с базой третьего транзистора и через

Составитель С. Пронин

Редактор С. Юско Техред T.Ôàíòà Корректор A. Ференц .

Заказ 507/76

Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам-изобретений и открытий

113035, Москва,. Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г, ужгород, ул. Проектная, 4

5 — 9934

;резистор - с шиной питания, коллектор третьего транзистора соедийек с второй выходной шиной, эмнттеры первого, второго и третьего транзисторов подключены к аноду диода, катод которого соединен через ключ с общей шиной и через реэисторс шиной питания, о т л и ч а ю щ е"е с я тем, что, c öåëüþ увеличения помехоустойчивости, оно дополнительно содержит диод и ключ, причем 10 эмиттер промежуточного транзистора соединен с анодом дополнительного диода, катод которого соединен через параллельно подключенные резистор и дополнительный ключ с общей шиной.

Источники информации, принятые во внимание при экспертизе

1. Валиев К.A., Орликовский A.A.

Полупроводниковые интегральные схе- мы памяти на биполярных транзисторных структурах. М., Советское радио, 1979, с. 229, рнс.7.21.

2. Патент Франции В 2373124,кл. G 11 С 17/06, 1979 °