Управляемый мажоритарный элемент

Иллюстрации

Показать всеРеферат

ОПйСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву{22) Заявлено 220781 (21) 3322239/18-21

Сеюз Советских

Социалистических

Республик . (ni993479 ($)) М Кд 3

Н 03 К 19/23 с присоединением заявки М2Государственный комитет

СССР но делам изобретений и открытий (23) ПриоритетОпубликовано 30.01,83. Бюллетень Мо 4

4 (53) УДК 621. 382 (088. 8) Дата опубликования опнсания3001.83 (72) Авторы изобретения.С.Н. Косоусов В.A Максимов, Я.Я. Петрич

I и С,И. Назаров

1 ( 3 р ° °

>

I (71) Заявитель (54) УПРАВЛЯЕИЫЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ

Изобретение относится к вЫчислительной технике и электронике и может быть использовано при построении многоканальных вычислительных систем, в частности для поканально« го разделения системы, например, в режиме проверки работоспособности каждого канала мажоритарно-резервированной системы.

Известен мажоритарный элемент на комплементарных МДП-транзисторах pil)

Недостаток известного элемента заключается s его узких функциональ» ных воэможностях, в частности, проявляющихся в невозможности его использования для поканального разделения систем.

Наиболее близким к предлагаемому по технической сущности является

- мажоритарный элемент, содержащий первый, второй ИДП-транзисторы с ка налами р-типа, третий, четвертый

МДП-транзисторы с каналами п-типа, первый, второй, третий ннверторы, выходы которых подключены к выходу элемента, первый инвертор включен между стоками первого и третьего

МДП-транзисторов, истоки которых соединены соответственно с шиной питания и общей шиной, второй и третий, инверторы включены между стоками второго и четвертого МДП-транзисторов, истоки которых соединены соответств цно с шиной питания и общей шиной, затворы первого, третьего

МДП-транзисторов и вход второго инвертора соединен с вторым информационным входом, входы первого и третьего инверторов — с первым, эат. воры второго и четвертого ИДП-транэ ист оров — с треть им 2 1.

Однако мажоритарный элемент не обеспечивает возможности отключения сигналов, поступающих в данный канал из других, в то время, как такая необходимость возникает в режймах проверки работоспособности каждого канала, а также при отказе двух каналов s трехканальной системе.

Цель изобретения — расширение функциональных возможностей мажоритарного элемента, Поставленная цель достигается тем, что в мажоритарный элемент, со

2 держащий первый, второй МДП-транзисторы с каналами р-типа и третий, четвертый ИДП-транзисторы с каналами п-типа, первый, второй, третий инверторы, выходы которых соединены с выходом элемента, первый инвертор

993479 включен между стоками первого и третьего МДП-транзисторов, истоки которых соединены соответственно с. шиной питания и общей шиной, второй и третий инверторы включены между стоками второго и четвертого МДПтранзисторов, затворы первого и ,третьего МДП-транзисторов и вход второго инвертора соединен с вторым информационным входом, входы первого и третьего инверторов - с первым, затворы второго.и четвертого МДПтранзисторов - с третьим, введены пятый и шестой МДП-транзисторы с ка. налами р-типа, HcTQKHtкоторых соединены с шиной. питания, а стоки соответственно со стоком первого и истоком второго МДП-транзисторы, и седьмой, восьмой МДП-транзисторы с каналами п-типа, истоки которых соединены с общей шиной, а стоки соответственно со стоком третьего и истоком четвертого МДП-транзисторов, затворы пятого, восьмого МДПтранзисторов соединены с прямым, а затворы шестого, седьмого — с ин-. версным управляющими входами.

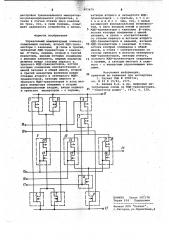

На чертеже приведена схема управляемого мажоритарного элемента.

Первый 1, второй 2, третий 3, четвертый 4 — МДП-транзисторы с каналами соответственно р- и п-типа, пятый 5, шестой 6 и седьмой 7, восьмой 8 — МДП-транзисторы с каналами соответственно р- и п-типа, первый инвертор 9 включен между стоками первого 1 и третьего 3 МДП-транзисторов, второй 10 и третий 11 инверторы - между стоками вторвго 2 и чет вертого 4, истоки первого 1, пятого

5, шестого 6 и третьего 3, седьмого

7, восьмого 8 МДП-транзисторов соединены соответственно с шиной 12 питания и общей шиной 13, стоки пятого 5 и шестого .6 соответственно,со стоком первого 1 и истоком второго 2 МДП-транзисторов, стоки седьмого 7 и. восьмого 8 — соответственно со стоком третьего 3 и истоком четвертого 4, выходы инвертаров подключены к выходу 14 элемента,входы первого 9 и третьего 11 инверторов соединены с первым информационным входом 15, затворы первого 1, третьего 3 МДП-транзисторов и вход второго инвертора 10 с вторым 16, затворы второго 2 и четвертого 4

МДП-транзисторов - c третьим 17, затворы шестого и седьмого 7 МДПтранзисторов соединены с инверсным

18 управляющим входом, затворы пя того. 5 и восьмого 8 — с прямым 19, Инверторы выполнены.на МДП-транзисторах р-типа 20 - 22 и МДП-транзисторах п-типа 23 - 25, Управляемый мажоритарный элемент .работает следующим образом.

5 !

О

ЗО

При наличии логической 1 на прямом управляющем входе 19 и логического 0 на инверсном 18 элемент выполняет функцию мажорирования.

Логический 0 на первом 15 и втором 16 либо на первом 15 и третьем 17, либо на втором 16 и третьем

17 информационных входах инициирует заряд на выходе 14 до уровня логической 1 через открытые МДПтранзисторы соответственно„первый

1 и 20 МДП-транзисторы с каналом р-типа первого инвертора 9 либо шестой 6, второй 2 и МДП-транзистор

21 с каналом р-типа третьего инвертора 11, либо шестой 6, второй 2 и мдп-транзистор 22 с каналом р-типа второгo инвертора 10. Логическая 1 на, первом 15 и втором 16 либо на первом 15 и третьем 17, либо на втором 16 и третьем 17 информационных входах инициирует заряд на выходе 14 до уровня логического 0 через открытые транзисторы соответственно, третий 3 и МДП-транзистор23 с каналом и-типа первого инвертора 9, либо восьмой 8, четвертый

4 и МДП-транзистор 24 с каналом п- . типа .третьего инвертора 11, либо восьмой 8, четвертый 4 и МДП-транзистор 25 с каналом п-типа второго инвертора 22. Таким образом, совпадение логических значений сигналов на любых двух информационных входах приводит к формированию на выходе

14 элемента логического уровня через соответствующие открытые транзисторы, соединяющие шину 12 питания либо общую шину 13 с выходом 14 элемента.

При наличии логического 0 на прямом 19 и логической 1 на инверснсу 18 управляющих входах откры ты пятый 5 и седьмой 7 и закрыты шестой 6 и восьмой 8 транзисторы, в результате чего выходным сигналом является инвертированный сигнал, поступающий на первый 15 информационный вход.

Таким образом, при наличии сигнала разрешения на управляющих входах 19 и 18 элемент выполняет функцию мажорирования, при отсутствии функцию инвертирования сигнала, поступающего на первый 15 информационный вход, что обеспечивает возможность разделения многоканального устройства на отдельные независимые каналы.

Использование предлагаемого элемента дает положительные эффекты, заключающиеся в том, что расширение функций элемента позволяет при подаче сигналов íà его управляющие входы отключать соседние каналы от данного, тем самьм обеспечивается возможность независимого функционирования каждого канала в режиме

993479

Формула изобретения

1Â

В

Заказ 507/76

34 - Подписное

ППП "Патент", од,ул.Проектная,4 настройки трехканального мажоритарно-резервированного устройства, а -также в случае отказа двух каналов из трех, что, в свою очередь, повышает надежность устройства в целом, 5 управляемый мажоритарный элемент, содержащий первый, второй МДП-тран- !О зисторы с каналами Р-типа и третий, четвертый МДП-транзисторы с каналами .П-типа, первый-, второй и третий инверторы, выходы которых соединены с выходом элемента, первый инвертор j5 включен между стоками первого и» третьего MQI-транзисторов, истоки— которых соединены соответственно с шиной питания и общей шиной, второй и третий инверторы включены между стоками. второго и четвертого МДП транзисторов, затворы первого и третьего МДП-транзисторов и вход второго инвертора соединен с вторым информационным входом, входы первого и третьего инверторов - с первым, . затворы второго и четвертого МДПтранзисторов — с третьим, о т л ич а ю ц н и с я тем, что, с целью расширения функциональных возможностей, в него введены пятый и шестой

МдП-транзисторы с каналами Р --тила, .истоки которых соединены с шиной питания, а стоки ", соответственно со стоком первого и истоком второго

МДП-транзисторов и седьмой, восьмой

МДП-транзисторы с каналами И-типа, истоки которых соединены с общей шиной, а стоки - соответственно со стоком третьего и истоком четвертого

МДП-транзисторов, затворы пятого, восьмого МДП-транзисторов соединены с прямым, а затворы шестого и седьмогo — с инверсным управляющими вхо- . дами.

Источники информации, принятые во внимание при экспертизе

1. Патент ChlA Р 3900742, кл, Н 03 К 19/42 1975.

2. Валиев К.A. и др, Цифровые интегральные схемы на МДП-транзисторах. Советское радио, 1971, с. 339, 12