Программируемый делитель частоты следования импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (n>993481

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву(22) Заявлено 08.0681 (21) 3323721/18-21

1511М. Кп.з

Н 03 К 23/00 с присоединением заявки ¹â€”

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет(53) УДК 621. 374 ° .4(088.8) Опубликовано 3001.83 Бюллетень № 4

Дата опубликования описания 300183 (72) Авторы изобретения

A Ñ. Сидоров, Э.В. Волков, Л.Н. Новиков и A Â. Калинин (7! ) Заявитель (54} ПРОГРАМИИРУЕИЫИ ДЕЛИТЕЛЬ ЧАСТОТЬ1

СЛЕДОВАНИЯ ИМПУЛЬСОВ

Изобретение относится к импульсной технике, в частности к программируемым делителям. частоты, и может быть использовано в цифровых синтезаторах частот.

Известен делитель частоты с дробным переменньм коэффнциентом деления, содержащий делитель частоты с переменным коэффициентом деления, первый вход которого является входом устройства, и блоки дробных разрядов, первые вход и выход блока старшего дробного разряда соединены соответственно с выходом и вторым входом делителя частоты с переменным коэффициентом деления, выход блока. младшего дробного разряда соединен соответственно с вторыми входом н вы. ходом блока старшего дробного разряда 1).

Недостатком такого делителя частоты является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому являетоя программируемый делитель .частоты с переменным коэффициентом деления и блок исключения импульсов, регистры и сумматоры, при этом первые входы делителя частоты с переменным коэффициентом деления и блока исключения импульсов подключены к входной шине, второй вход делителя частоты с переменным коэффициентом деления соединен с выходом блока исключения импульсов, первый выход — с вторьм входом блока исключения импульсов, а выход — с тактовыми входами регист. ров, информационные входы которых подключены к инФормационным выходам сумматоров соответствующих разрядов, а выходы — к первым информационным входам сумматоров соответствующих разрядов, вторые информационные входы которых и третий вход делителя частоты с переменным коэффициентом деления подключены к шине ввода управления, причем выход переноса сумматора старшего разряда соединен с управляющим входом блока исключения импульсов, а входы переноса — с выходом переноса сумматора последующего младшего разряда (2).

Недостаток устройства - низкое быстродействие.

Цель изобретения — повышение быстродействия, Для достижения цели в программируемый делитель частоты следования импульсов, содержащий блоки дробных разрядов, каждый из которых состоит

9934 81 из.регистра и сумматора, выход которого соединен с йнформационным входом регистра, первый информационный вход — с выходом регистра, а второй информационный вход — с соответствующей шиной ввода кода управления, 5 и делитель частоты первый вход которого соединен с входнОЙ шиной, второй вход — с соответствующей шиной ввода кода управления, а выход — с тактовыми входами регистров каждого блока дробного разряда, введен элемент задержки, первый вход которого соединен с ныходом делителя частоты, второй вход — с выходом переноса сумматора блока младшего. дробного разряда, а выход - с входом переноса сумматора блока старшего дробного разряда, выход которого сдединен с третьим входом делителя частоты.

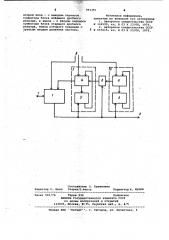

На чертеже представлена структуР"

20 ная схема устройства.

Устройство содержит делитель 1 частоты с переменным коэффициентом деления, блоки 2 и 3 дробных разрядов каждый из которых состоит из сумматора 4 и регистра 5, элемент б единичной задержки, входную шину 7, шину 8 ввода кода управления, выходную шину 9, Устройство работает следующим образом, Импульсы входной частоты поступают на шину 7 устройства. Импульсы выходной частоты снимаются с шины 9 делителя 1. В разрядах регистров 5 35 хранится результат суммирования, а в элементе 6 групповой перенос;сформированный сумматорами 4 а предыдущем цикле работы устройства. Информация с выходов регистров 5 поступает на первые информационные входы соответствующих сумматоров 4. Сигнал с выхода элемента 6 поступает на вход переноса сумматора блока старшего дробного разряда. На второй вход делителя 1 по шине 8 поступает код целой части коэффициента деления. На вторые информационные входы сумматоров 4 по шине 8 поступают коды соответствующих разрядов дробной части коэффициента деления. В результате на выходах сумматоров формируются сигналы суммы и сигналы групповых переносов текущего такта суммирования. Возникающий сигнал группового переноса сумматора блока старшего дробного разряда поступает на третий вход делителя 1 и увеличивает его целочисленный коэффициент деления всякий раз на единицу, реализуя тем самьм усредненный дробный 60 коэффициент деления.

С приходом каждого очередного выходного импульса делителя 1 в регистры 5 заносится новая информация о результатах суммирования, а в 6S элемент 6 — групповой перенос сумматора блока младшего дробного разряда.

Поскольку в течение текущего цикла деления сигнал группового переноса сумматора блока младшего дробного разряда, сФормированный в предыдущем цикле деления и хранящий- ся н элементе б, не изменяется в течение времени между двумя выходными импульсами устройстна, то его максимальное быстродействие опреде ляется быстродействием сумматора только блока старшего дробного разряда и не зависит от числа блоков дробных разрядов при их соответствующем последовательном наращивании. фиксированная единичная задержка групповдго переноса сумматора блока младшего дробного разряда на один период выходной частоты не влияет на равномерность формирования сигна ла переноса сумматора блока старшего дробного разряда. 8 результате величина паразитной девиации выходной импульсной последовательности устройстна сохраняется минимальной.

Предлагаемое техническое решение позволяет без существенчого усложнения повысить быстродействие устройства в число раз, равное числу последовательно соединенных блоков дробных разрядон..А это позволяет снизить во столько же раз целую часть минимального коэффициента деления, реализуемого грограммируемым делителем частоты с дробным переменным коэффициентом деления на максимальных входных частотах. Независимость быстродействия устройства от количества блоков дробных разрядов позволяет при использовании програь мируемого делителя частоты в цифровом сннтезаторе частот увеличить число синтезируемых частот. формула изобретения

Программируемый делитель частоты следования импульсов, содержащий блоки дробных разрядов, каждый из которых. состоит из регистра и сумматора, выход которого соединен с информационным входом регистра, первый информационный вход — с выходом регистра, а второй информационный вход - с соответствующей шиной ввода кода управления, и делитель частоты, перный вход которого соединен с входной шиной, второй вход — с соответствующей шиной ввода кода управления, а вьход — с тактовьми входами регистров каждого блока дробного разряда, отличающийся тем, что, с целью повышения быстродействия, в него введен элемент задержки, первый вход которого соеди- . нен с выходом делителя частоты, 993481

Составитель 0, Кружилина

Редактор С. Юско Техред Т.Фанта Корректор И. Шулла

Заказ 507/76 Тираж 934 Подписное

ВНИИПИ Государственного комитета СССР по делам. изобретений И открытий

113035, Москва, Ж"35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 второй вход — с выходом переноса-сумматора блока младшего дробного разряда, а выход - с входом перекоса сумматора блока старшего дробного разряда, выход которого соединен с третьим входом делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 344590, кл. Н 03 К 23/00 1970.

2. Авторское свидетельство СССР

5 9 657615, кл. Н 03 К 23/00 1976,